# 11 MAINFRAME PDP 11/40

# 11 MAINFRAME PDP 11/40

#### LEARNING ACTIVITY UNIT

KD11-A INTRODUCTION AND OVERVIEW

DECEMBER 18, 1973

#### RATIONALE

Welcome to the wonderful world of the PDP-11/40. You have now completed your study of the PDP-11/05 and you should have a solid foundation of PDP-11 principles which you will use to develop your understanding of the 11/40. Don't feel that you are going on to something completely different and that you can therefore forget about the 05. The 40 is really just an extension of the 05 in that many of the concepts are similar and many of the basic operations are done in almost an identical fashion. Following are some of the features of the 40 that you will find to be similar to what you already know about the 05.

- 1. The operation of functions internal to the C.P. are controlled by a Read Only Memory (ROM).

- 2. The Bus Control is handled in a similar fashion, which must be so since all of the controlling signals on the PDP-11 Unibus are identical regardless of the C.P. being used.

- 3. The C.P. contains a set of 16 registers which are used by the programmer (R0 R7) and for handling some of the internal operations (R10 R17).

- 4. The instruction set is identical to that used on the 05 with the exception of a few additional instructions.

- 5. Console operations are identical with the addition of a few more indicators. So you can see that you already have a lot of information which is relevant to the 11/40.

During this unit you will be having what essentially amounts to a discussion period among you, your fellow students and your instructor. The instructor will attempt to point out all of the similarities and differences between the 11/05 and the 11/40. He will also discuss the specifications and applications of 11/40's. He will summarize the

the objectives of the 11/40 course and outline for you what you will be doing for the next four days or so. Please feel free to debate points with your instructor and among yourselves under the guidance of the instructor.

In some ways this is the most important lesson on the 40 since it will help you to tie together facts which you have learned about the 05 with information you are finding out about the 40. In addition this lesson should help you to make the transition from the 05 course to the 40 course and start you on your way to becoming PDP-11/40 giants.

# PREREQUISITES

Successful completion of the PDP-11/05 portion of the course.

### OBJECTIVES

To demonstrate knowledge of some of the major characteristics of the 11/40 by correctly answering five out of the six questions given in the post test.

# LEARNING ACTIVITIES

- I. Attend the 90 minute discussion period. Please ask any questions you have concerning 11/40 specifications, applications, systems concepts, configurations, etc. Be sure to take note of references made to figures, drawings, tables, etc. during the discussion.

- II. Attempt the post test. You have 20 minutes.

#### APPENDIX A

The following list is a point outline of the 11/40 course. Each point is a two hour LAU.

- 1. KD11A Introduction and Overview (this LAU).

- 2. Block Diagram: multiplexors and data paths.

- 3. Block Diagram: control section.

- 4. Block Diagram: clocking, Unibus control, branching.

- 5. Flow Diagram: introduction, overview, instruction format.

- 6. Flow Diagram: Jamupp to console, console.

- 7. Flow Diagram: single operand instructions.

- 8. Flow Diagram: double operand instructions, overlap.

- 9. Flow Diagram: traps/service.

- 10. Lab Project: maintenance module usage

- 11. Logic Diagrams: conventions, special circuits, layout

- 12. Logic Diagrams: data paths, # word, IR decode.

- 13. Logic Diagrams: timing, Jamupp.

- 14. Logic Diagrams: status, bus control

- 15. Lab Project: scoping clock, Unibus.

- 16. Power System: block diagram, distribution.

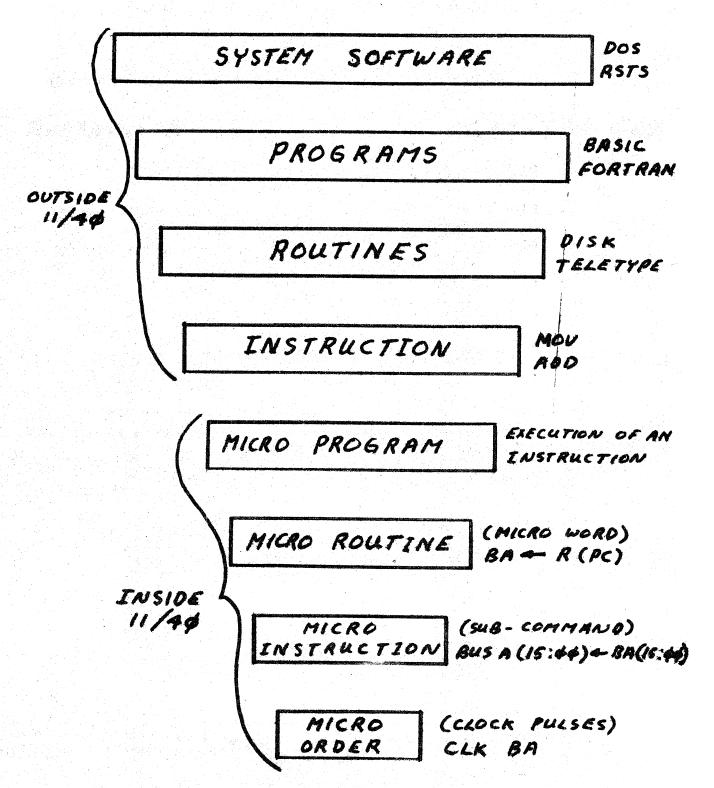

# SYSTEM HIERARCHY

### APPENDIX C

#### THE MARK INSTRUCTION

The MARK is an instruction that facilitates stack cleanup procedures when returning from a subroutine. Stack cleanup simply means resetting Stack Pointer R6 to the value it contained just prior to jumping to the subroutine. It is unique in that the instruction itself is executed off the stack.

# PROGRAMMING OPERATION

The routine shown below illustrates the operation of the MARK and may be used by the technician to check for proper operation.

Given R5 = 1234, R6 = 2000

```

5000/MOV R5, -(6)

; (1776) 1234, old R5

2/MOV #20, -(6)

;(1774) 20, Pl

4/#20

6/MOV #30, -(6)

; (1772) 30, P2

10/#30

12/MOV #40, -(6)

;(1770) 40, P3

14/#40

16/MOV #MARK3, -(6)

;(1766) 006403, MARK3 instr.

20/#MARK3

22/MOV R6, R5

;(5) 1766, content of R5 = adrs

of MARK 3 instr

24/JSR PC, 6000

; dst \rightarrow R [TEMP] , (TEMP) 6000

26/index

; R [SP] -2 \rightarrow R [SP], (6) 1764

5030/HALT

; R [SF] \rightarrow @R [SP], (1764) 5030

; R[PC] \rightarrow R[SF], (7) 5030

; R TEMP \rightarrow R [PC]. (7) 6000

```

```

6000/HALT

6002/RTS5

;R[DF]→R[PC], (7) 1766:adrs of

MARK3 on stack

;@R[SP] → R[DF], (5) 5030:return PC

;R[SP]+2→R[SP], (6) 1766

```

Load address to 5000 and depress START. The instruction in 5000 saves the contents of R5 (325) on the stack in location 1776. The next three MOV instructions in 5002, 5006, and 5012 push three parameters onto the stack. Then the instruction in location 5016 pushes the MARK instruction (6403) onto the stack into location 1766. At this point, R6 contains 1766, which is transferred into R5 when the MOV instruction in location 5022 is executed.

Finally, the JSR is executed, which saves the return PC on the stack in location 1764 and causes program control to transfer to location 6000 where the machine halts.

After the machine halts, the registers and stack appear as shown below:

R 7 = 6002; address of next instr. in subtn. R 5 = 1766; address of the MARK instr.

R 6 = 1764; stack

|                  |                  |           |             |    | ·    |

|------------------|------------------|-----------|-------------|----|------|

| 1764             | return PC = 5030 | result of | instruction | at | 5024 |

| 1766             | MARK3 006403     | result of | instruction | at | 5016 |

| 1770             | P3 = 40          | result of | instruction | at | 5012 |

| 1772             | P2 = 30          | result of | instruction | at | 5006 |

| 1774<br>original | P1 = 20          | result of | instruction | at | 5002 |

| R6= 2000         |                  |           |             |    |      |

Normally at this point the subroutine would use the SP to retrieve the parameters for its execution.

This will cause execution of the RTS Now press CONT. instruction in 6002. The RTS will transfer the contents of R5(1766) into the PC and pop 5030 off the stack into

APPENDIX C Page 3

R5. Since the PC contains 1766, the next instruction executed will be the MARK instruction. After fetching the MARK, the PC gets updated to 1770, then the SP gets the contents of the PC (1770) plus two times the number of arguments (6) which is 1776. The PC gets the contents of R5 (5030) therefore pointing to the next instruction after the JSR. Then 1234 is popped off the stack and put into R5 which restores the C.P. to the correct condition to continue on in the main program.

# APPENDIX D-1

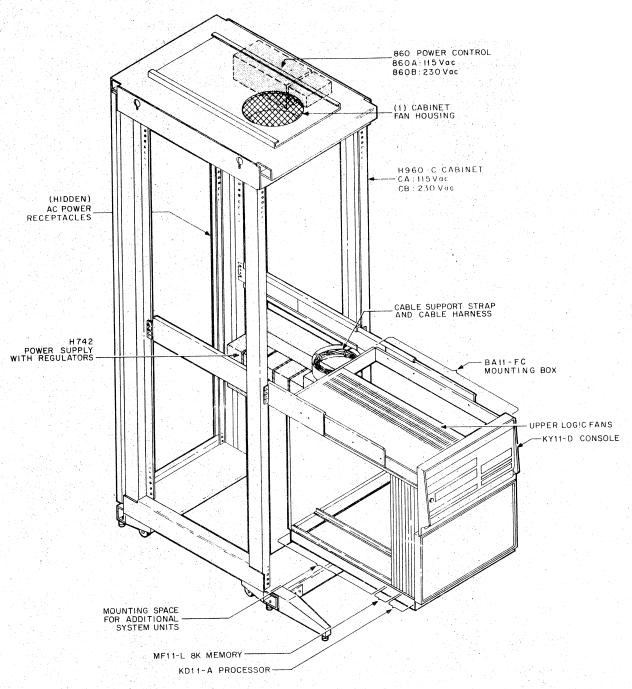

11-1386

H960 - CD

# APPENDIX D-2

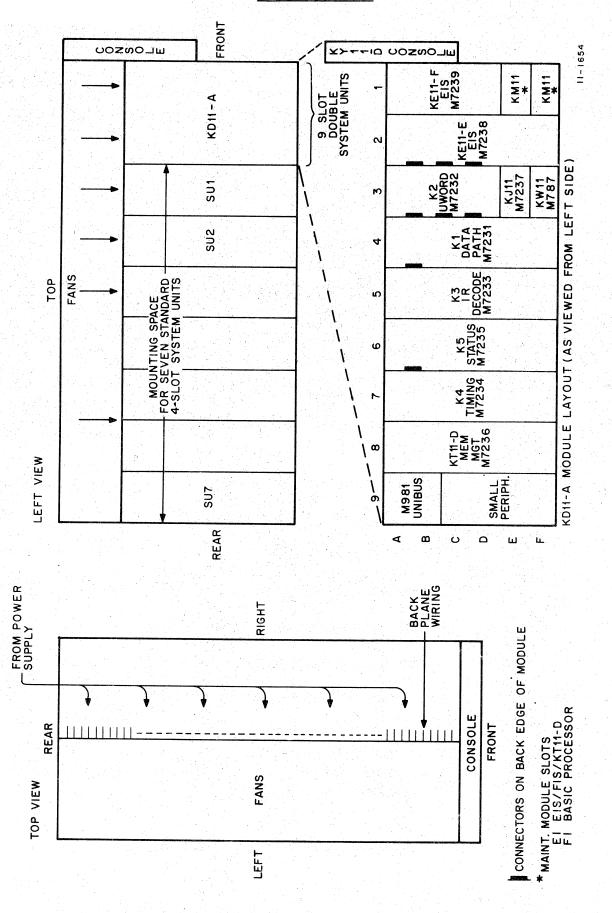

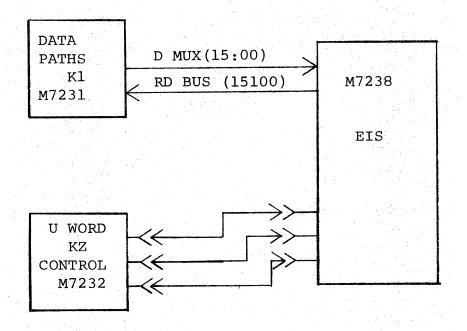

# KD11-A MODULES

| 늘 있으로 그리지만 다 가를 하고 하다. | 이 사람이 살아 살아 있다. 그 살아 하셨다면 얼마 하는 것 같은 사람들이 많아 가야 하는 것도 먹는데 다.                                           |

|------------------------|--------------------------------------------------------------------------------------------------------|

| 55-09701               | KYll-D Console, hex, no module pins, two back side connectors to connect to Kl & K5 modules via cables |

| M981                   | Unibus cable connection with terminator, double height                                                 |

| M7231                  | Kl, Data Path, hex, one back side con-<br>nector to console                                            |

| M7232                  | K2, U Word, quad. three back side con-<br>nectors to M7238 (EIS)                                       |

| м7233                  | K3, IR Decode, hex                                                                                     |

| M7234                  | K4, Timing, hex, clock adjustment                                                                      |

| M7235                  | K5, Status, hex, one back side con-                                                                    |

|                        | nector to console                                                                                      |

| *M7236                 | KTll-D, Memory Management, hex                                                                         |

| *M7237                 | KJll-A, Stack Limit Register, single height                                                            |

| *M7238                 | KEll-E, EIS option, hex, three back side connectors to M7232                                           |

| *M7239                 | KEll-F, FIS option, quad                                                                               |

| *M787                  | KWll-L Line Clock option, single height                                                                |

| *W130, W131            | KMll, Maintenance module set 1) Processor 2 slots reserved 2) Options                                  |

| Small<br>Peripheral    | 1) KLll: M105 single 2) DLl1 M7820 single M7800 quad M780 double                                       |

<sup>\*</sup>Pre-wired processor options-not included as part of the basic processor.

# APPENDIX D-3

#### APPENDIX E

#### LIST OF SOME 11/40 APPLICATIONS

Communications: Message Switching, Data Concentration,

Remote Terminals, System "Front Ends"

Engineering: Calculation, Design and Drafting, Sim-

ulation, Graphics

Computation: Scientific Calculation, In-house Time-

sharing, Timesharing Utilities, Hybrid

Systems (A/D)

Business: Inventory Control, General Accounting,

Payroll, Reservations, Text Editing, Data Storage and Retrieval, Order Entry,

Source Data Collection, Key-to-Tape

Education: Computer-aided Instruction, Programming

Courses, Computer Science Courses, Problem Solving, Engineering Courses,

Administrative Processing

Industry: Data Acquisition and Control, Data

Monitoring and Logging, Machine Control,

Numerical Control, Testing, Process Control, Typesetting, Traffic Control, Electric Utility Monitoring and Control

Research: Oceanographic Studies, Gas Chromat-

ography/Mass Spectroscopy, Signal

Processing

#### APPENDIX F

LIST OF 11/40 INTERNAL OPTIONS

KEll-E, Extended Instruction Set

KEll-F, Floating Instruction Set

KT11-D, Memory Management

KJll-A, Stack Limit Register

KWll-L, Line Frequency Clock

# APPENDIX G

# LIST OF THE BASIC 11/40 MAINDECS

| CPU |            |                                 |

|-----|------------|---------------------------------|

|     | T1         | Branch                          |

|     | T2         | Conditional Branch              |

|     | Т3         | Unary                           |

|     | <b>T4</b>  | Binary                          |

|     | <b>T</b> 5 | Rotate/Shift                    |

|     | Т6         | CMP Equality                    |

|     | Т7         | CMP Non-equality                |

|     | <b>T</b> 8 | Move                            |

|     | Т9         | Bit Set Clear Test              |

|     | T10        | ADD                             |

|     | T11        | Subtract                        |

|     | T12        | Jump                            |

|     | T13        | JSR, RTS, RTI                   |

|     | T14        | 40 Traps Test                   |

|     | T15        | ll Family Instruction Exerciser |

|     | T17        | System Exerciser                |

|     |            | Power Fail                      |

|     |            | General Test Program            |

|     |            |                                 |

#### Memory

Basic Address Test Up

Basic Address Test Down

No Dual Address Test

Basic Test Patterns

Moving Ones and Zeros

One's Susceptibility

Worst Case Noise

Core Heating

Random Data

8K Special

Up-Down Address Test

Memory I/O Exerciser

0-124K Exerciser

# LEARNING ACTIVITY UNIT

KD11A PROCESSOR

BLOCK DIAGRAM

DATA PATHS

1/9/73

#### RATIONALE

Previously, you have been introduced to the 11/40 and have studied it from a physical point of view. You have seen the mechanics of the mounting box, the cabinet, module locations, etc. You have also studied the 11/05 processor and have seen how a C.P. can be depicted in a block diagram format.

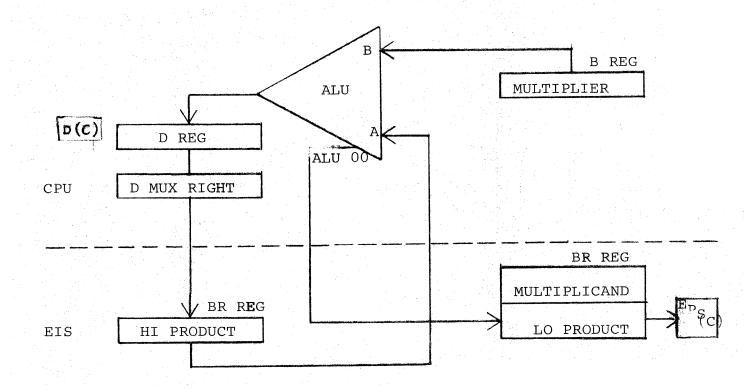

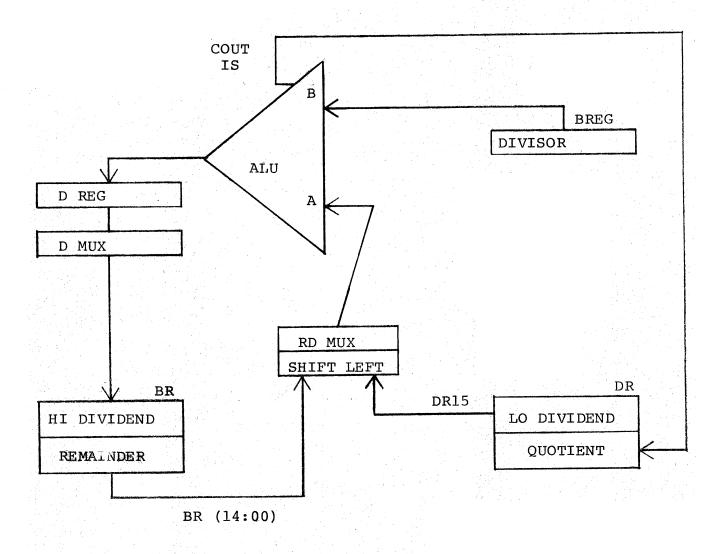

Now you are going to be introduced to the KDllA Block Diagram. You will observe how the C.P. can be broken into three basic sections of which, in this unit, we are primarily interested in the Data Path section. You will learn the name and function of each of the major components in this section and how data is manipulated for various operations.

The skills you learn in this unit will prove invaluable in future LAU's, since you will be doing similar analysis in studying the other portions of the block diagram. More importantly, you will find the block diagram to be indispensible as a trouble shooting aid. For example, once you have properly analyzed the symptoms of a problem, you will be able to narrow its location down to one of the major components within that section if you have a good understanding of the block diagram.

# PREREQUISITES

Satisfactory performance to this unit.

# OBJECTIVES

Using the list of Data Manipulation Functions in Appendix B and any other reference material, write the sets of functions required to implement a given instruction.

# LEARNING ACTIVITIES

#### I. LECTURE

Attend the twenty minute lecture. Pay close attention, and jot down notes on the block diagram itself. Hold questions until the end of the lecture.

# II. PROJECTS AND PROBLEMS

Α.

- Do the problems and answer all the questions.

You will find the correct answers in Appendix A.

- 2. Refer to the KD11A Processor Maintenance Manual, Table 3-3 on p. 3-23 to p. 3-34.

- 3. All page references made in this LAU are to the above mentioned manual unless specifically stated otherwise.

- 4. As you go through the following projects, make pertinent notes on your block diagram. These should prove to be invaluable trouble shooting aids in the lab and in the field.

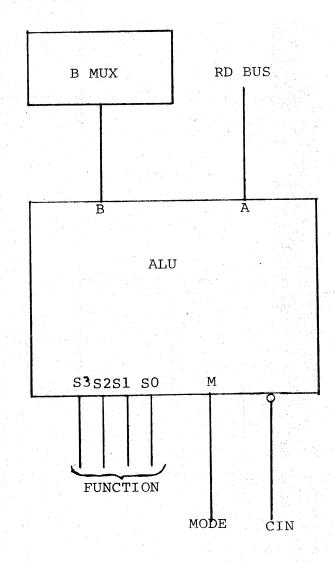

- B. Locate the Arithmetic Logic Unit (ALU) approximately in the center of the page.

- 1. Observe that there are five control lines going into the ALU. These will cause the ALU to execute one of thirty-two functions which are shown in Table 3-2 on p. 3-17. Study this table and analyze the various functions.

- 2. Make special note of the function specified by the \*. What two instructions would make use of this operation? Mark this on your block diagram since this is the only place in the machine where this operation occurs.

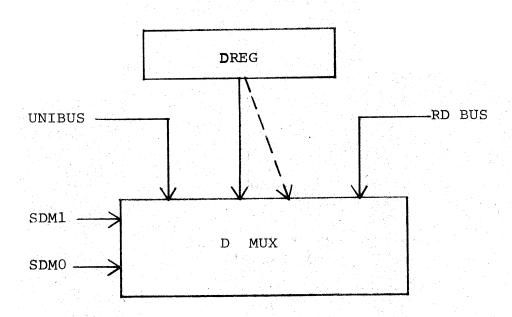

- C. Locate the D Reg and the D Mux just below the ALU.

- 1. Specification of which input is to be gated

through the D Mux is done by the

and \_\_\_\_\_ signals.

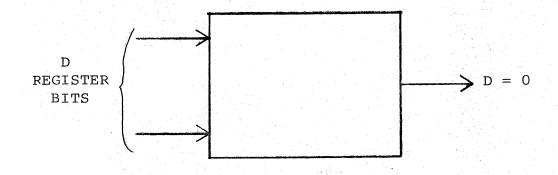

- 2. Analyze the function of the box labeled D (C).

- 3. Refer to Table 3-1 on p. 3-14. Which of the following combinations of signals would allow an instruction to be read in from core, gated through the D Mux and presented to the I Reg?

- (a) SDM1 (0) \* SDM0 (0)

- (b) SDM1 (0) \* SDM0 (1)

- (c) SDM1 (1) \* SDM0 (0)

- (d) SDM1 (1) \* SDM0 (1)

Check your answer. If you were correct, go on to section D. If not, read the following description.

We are fetching an instruction. We have done the bus cycle and the data (which is the instruction) is on the Unibus data lines. We now want to take this data and clock it into the IReg. The data comes from BUS D (15:00) through receivers and into the D MUX via the left-most input on our diagrams. We then must select this input by setting up the gating signals so that SDMO is a l and SDMl is a 0. As you can see from Table 3-1 this is the combination which selects the Unibus data. The data (which you will remember is our instruction) will be on the D MUX Bus and all that is left is for us to generate the CLK IR signal to have the instruction clocked into the I Reg.

If you still do not understand this sequence, ask your instructor about it.

- D. Locate the B Reg, B Constants and B Mux which feed the BIN of the ALU.

- 1. Analyze the B Mux function in Table 3-1. To swap bytes the gating signals must have what values?

B Mux Low (07:00)

- (a) SBML0 = \_\_\_\_

- (b) SBMLl =

B Mux High (15:08)

- (c) SBMHO = \_\_\_\_

- (d) SBMH1 =

- 2. What would be the value of these signals to accomplish sign extension of the value in the B Reg?

- (a) SBML0 = \_\_\_\_

- (b) SBML1 = \_\_\_\_

- (c) SBMH0 = \_\_\_\_

- (d) SBMH1 = \_\_\_\_

OR

- (e) SBML0 = \_\_\_\_

- (f) SBML1 = \_\_\_\_

- (g) SBMH0 = \_\_\_\_

- (h) SBMH1 =

Indicate on your block diagram where byte manipulation takes place.

| 3. | The CIN MUX feeds the input designated CIN with one of the following values:                                                                                |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | (a)                                                                                                                                                         |

|    | (b)                                                                                                                                                         |

|    | (c)                                                                                                                                                         |

|    | Discuss some of the functions for which these inputs could be used.                                                                                         |

| 4. | The AIN input is fed from a 16 bit inverter labeled BUFFER which is fed from a wired -OR indicated by the dashed OR symbol. At this point, data comes from: |

|    | (a)                                                                                                                                                         |

|    | (b)                                                                                                                                                         |

|    | (c)                                                                                                                                                         |

| 5. | You will find the COUT MUX below and to the left of the ALU. Observe that this multiplexor has four inputs which are:                                       |

|    | (a)(d)                                                                                                                                                      |

|    |                                                                                                                                                             |

|    | (c) <u></u>                                                                                                                                                 |

|    | Analyze and discuss among yourselves the                                                                                                                    |

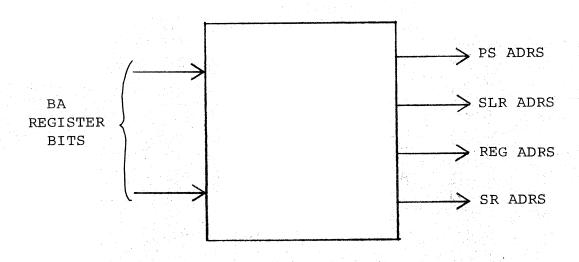

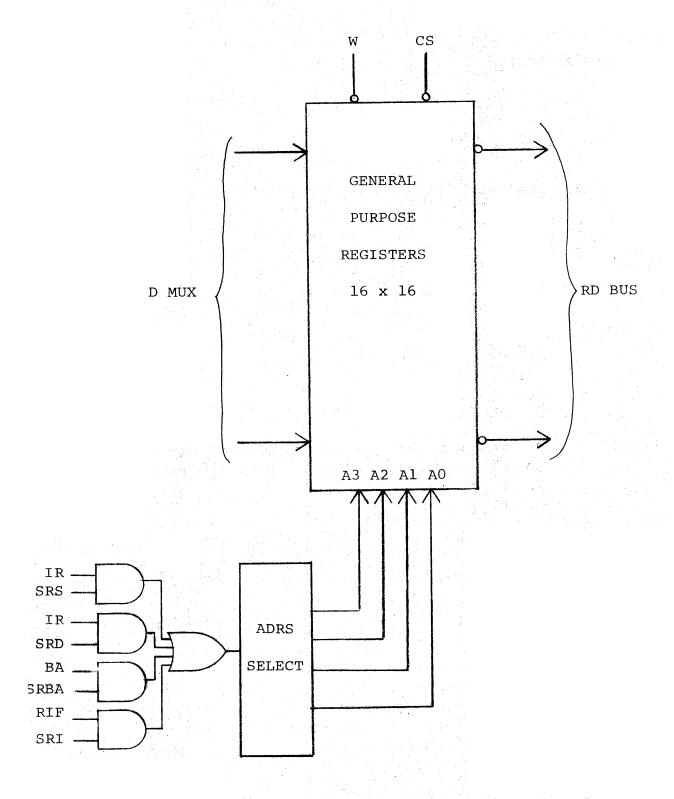

- E. Locate the General Purpose Registers (GPR's), sometimes called Scratch Pad Registers; the Register Address Inputs; and the list of register names in the upper right hand corner of the block.

- 1. A brief description of the function of each of these registers is given in the first paragraph of section 3.3.5 on p. 3-15. Read it.

- What enabling signal will be brought up to allow us to get the address contained in R [2] for the following instruction?

| т | NC  | 12  | ١ |

|---|-----|-----|---|

| T | TAC | ( Z | , |

| (a)                                    |                   |                     |         |       |

|----------------------------------------|-------------------|---------------------|---------|-------|

| Which of the four<br>be used to select | groups<br>the rec | of addre<br>gister? | ss line | s wil |

| (b)                                    |                   |                     |         |       |

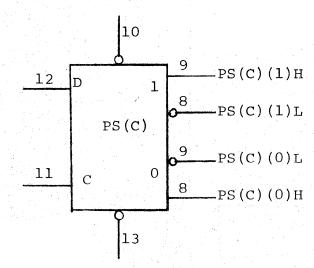

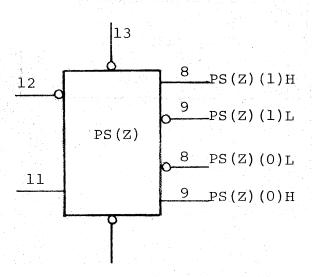

- F. Locate the Processor Status Word (PSW) between the B Mux and the GPR's.

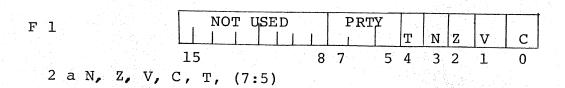

- 1. Note how many bits are illustrated here. What are they?

| 1   |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |     |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|

| å   |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |     |

| - 1 | 5 A 1 4 4 4 1 | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |     |

| - 1 |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 1   |

| 1   |               | and the first term of the first section of the firs |       | í . |

| 1   |               | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |     |

|     | <br>1 1 1     | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 1 1 |     |

|     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |     |

2. Which bits can be affected implicitly?

| 1-1 |  |  |  |  |  |

|-----|--|--|--|--|--|

| (a) |  |  |  |  |  |

|     |  |  |  |  |  |

Discuss the reasons for this.

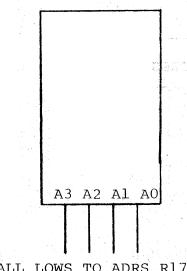

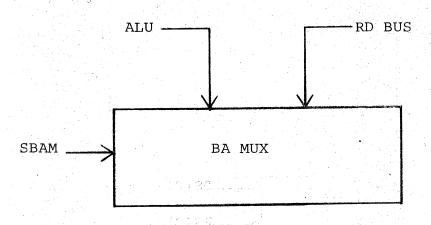

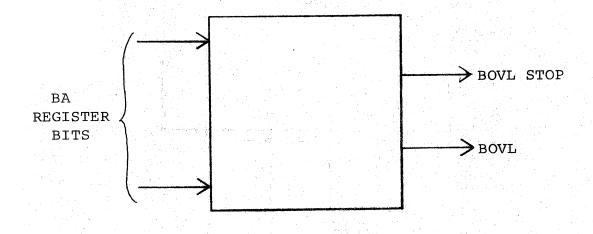

- G. Locate the BA Mux, the BA Reg, the Internal Data, and Address Decode and the Address Display which are found directly below the GPR's.

- 1. Note the BA Mux control in Table 3-1 on p. 3-14 and read section 3.3.2 on p. 3-15.

- H. At this point you should be familiar with the Data Path section of the block diagram. You should understand the function and operation of every block within this section.

- I. Refer to the list of Data Manipulation Functions in Appendix B. Write the set of functions required to implement the operations listed below. If more than one operation is required, group the functions into separate sets and complete each set with its required clocking signal.

- 1. Move the contents of the PC into the BA.

- 2. Increment the contents of RO, as in INC %O.

- 3. Add the contents of R3 to the contents of R2, as in ADD %3, %2.

- 4. Pop a word off the Processor Stack into the PC.

# III. ADDITIONAL EXERCISES

If you feel that you need more practice before you attempt the tese, your instructor will be glad to provide you with more examples.

If you have been having trouble with the previous exercises, do not hesitate to ask your instructor for assistance.

#### IV. POST TEST

Attempt the post test. You have twenty minutes. Do the best you can.

#### APPENDIX A

- B 3 a 0 b 1 c PS (C)

- 4 a PSW ANDed with BUS RD FM PS

- b GPR'S

- c BUS RD (15:00) (Internal Options)

- 5 a PS (c)

- b ALU 15

- c COUT 07

- d COUT 15

- C 1 SDMO, SDM1

- 3 b SDM1 (0) \* SDM0 (1)

- D 1 a SBML0 = 0

- b SBML1 = 1

- c SBMH0 = 0

- d SBMH1 = 1

- 2 a SBML0 = 0

- b SBML1 = 0

- c SBMH0 = 1

- d SBMH1 = 0

- e SBML0 = 1

- f SBML1 = 0

- g SBMH0 = 1

- h SBMH1 = 0

- E 2 a SRD

- b IR (2:0)

#### I 1 Operation BA←PC

RIF (3:0) = 07RA  $(3:0) \leftarrow RIF (3:0)$ BA  $(15:00) \leftarrow R(15:00)$ CLK BA

# 2 Operation $D \leftarrow R[0] + 1$

RA(3:0) ← IR (2:0) AIN (15:00) ← R(15:00) CIN ← 1 ALUout = A plus CIN CLK D Alternate Method

RA (3:0) ← IR (2:0)

AIN(15:00) ← R(15:00)

BCON (15:00) ← 1

BIN (15:00) ← BCON(15:00)

CIN ← 0

ALUout = A plus B plus CIN

CLK D

# Operation R $[0] \leftarrow D$

RA (3:0) ← IR (2:0)

DMUX (15:00) ← D (15:00)

R(15:08) ← DMUX(15:08)

R(07:00) ← DMUX(07:00)

WRH

WRL

# 3. Operation B←R[3]

```

RA (3:0) ← IR(8:6)

DMUX(15:00) ← R(15:00)

BREG(15:00) ← DMUX(15:00)

CLK B

```

# Operation D+B+R[2]

RA(3:0) ← IR(2:0) AIN(15:00) ← R(15:00) BIN(15:08) ← BREG(15:08) BIN(07:00) ← BREG(07:00) CIN ← 0 ALUout = A plus B plus CIN CLK D

# Operation $R[2] \leftarrow D$

RA(3:0) ← IR (2:0)

DMUX(15:00) ← D(15:00)

R(15:08) ← DMUX(15:08)

R(07:00) ← DMUX (07:00)

WRH

WRL

# I. 4. Operation BA $\leftarrow$ R[SP] D $\leftarrow$ R[SP] +2

RIF(3:0) = 06

RA(3:0) ← RIF(3:0)

BA (15:00) ← R(15:00)

AIN(15:00) ← R(15:00)

BCON(15:00) ← 2

BIN(15:00) ← BCON(15:00)

CIN ← 0

ALUout = A plus B plus CIN

CLK BA

CLK D

## Operation R[SP]← D

RIF(3:0) =06

RA(3:0) RIF (3:0)

DMUX(15:00) D(15:00)

R(15:08) DMUX (15:08)

R(07:00) DMUX(07:00)

WRH

WRL

(DATI)

Operation R[PC] ← BUS Data

RIF(3:0) =07 RA(3:0)←RIF(3:0) DMUX(15:00)←BUS D (15:00) R(15:08)← DMUX (15:08) R(07:00)←DMUX (07:00) WRH WRL

#### KD11A DATA MANIPULATION FUNCTIONS

# GENERAL PURPOSE REGISTERS

| $RA(3:0) \leftarrow RIF(3:0)$<br>$RA(3:0) \leftarrow IR(8:6)$          | RIF $(3:0) = 00$ |

|------------------------------------------------------------------------|------------------|

| RA(3:0) ← IR(2:0)<br>RA(3:0) ← BA(3:0)                                 |                  |

|                                                                        |                  |

| $R(15:08) \leftarrow DMUX(15:08)$<br>$R(07:00) \leftarrow DMUX(07:00)$ | RIF (3:0) =17    |

# ARITHMETIC LOGIC UNIT

| $AIN(15:00) \leftarrow R(15:00)$     | BCON(15:00) ← 1                      |

|--------------------------------------|--------------------------------------|

| $AIN(07:00) \leftarrow PS(07:00)$    | € 2                                  |

|                                      | <b>←</b> 4                           |

| $BREG(15:00) \leftarrow DMUX(15:00)$ | ←10                                  |

| $BIN(15:00) \leftarrow BCON(15:00)$  | BCON (15:00) ←177570                 |

| $BIN(15:08) \leftarrow BREG(15:08)$  |                                      |

| $BIN(07:00) \leftarrow BREG(07:00)$  | ALUout = A plus CIN                  |

| $BIN(15:08) \leftarrow BREG(07:00)$  | A plus CIN                           |

| BIN(07:00) 	BREG(15:08)              | A plus B plus CIN                    |

| BIN(15:08)← BREG (07)                | A Minus B                            |

|                                      |                                      |

|                                      | ALUout = B plus CIN                  |

| CIN←1 CIN←0 COUT←PS(                 | c) COUT←ALU15                        |

| D(15:00) 		ALUout (15:00)            | PS(7:0) ← DMUX(7:0)                  |

| $DMUX(15:00) \leftarrow D(15:00)$    | $IR(15:00) \leftarrow DMUX(15:00)$   |

| $DMUX(15:00) \leftarrow R(15:00)$    |                                      |

| DMUX(15:00) 	BUS D(15:00)            | $BA(15:00) \leftarrow R(15:00)$      |

| DMUX(15:00) < COUT, D(15:01)         | $BA(15:00) \leftarrow ALUout(15:00)$ |

|                                      | BA(IJ:00) ALUOUL(IJ:00)              |

# CLOCKING SIGNALS

| WRH CLKB | CLK | BA | CLK IR |

|----------|-----|----|--------|

| WRL CLKD | CLK | PS |        |

LEARNING ACTIVITY UNIT

KD11A BLOCK DIAGRAM

CONTROL SECTION

1/15/74

#### RATIONALE

By now you have had a good overview of the KDllA Block Diagram. You have learned how data flows through and how it is manipulated within the CP. You have also learned how the 11/05 Control Section operates and how it affects the manipulation of data in the 05.

Now, in studying the 11/40 Control Section, you will first approach it from the point of view of how it is similar to the 11/05. After that, you will analyze the <u>different</u> concepts which the 11/40 utilizes.

A complete understanding of the 11/40 Control Section is imperitive if you are to troubleshoot the machine properly. If you do not realize what is actually happening in this section, it will be almost impossible to comprehend the flow diagrams or to predict what will happen when you are using the maintenance board.

#### PREREQUISITES

Satisfactory completion of all units to date.

#### **OBJECTIVES**

- A. Given a list of Control Section Facilities, you must be able to match these with five generalized functional descriptions.

- B. Given a list of microinstructions, show what will be contained in certain registers and what will be on certain lines in the Control Section during the execution of each microinstruction.

You will have thirty minutes to do this and will be allowed one error in A and one in B.

#### LEARNING ACTIVITIES

#### I. LECTURE

Attend the forty-five minute lecture. Make notes on your block diagram. Hold your questions until the end of the lecture.

- II. PROJECTS/PROBLEMS (Answers in Appendix B)

- A. Given the list of Control Section Facilities in Appendix A, choose one which is best described by each of the eight following functional statements.

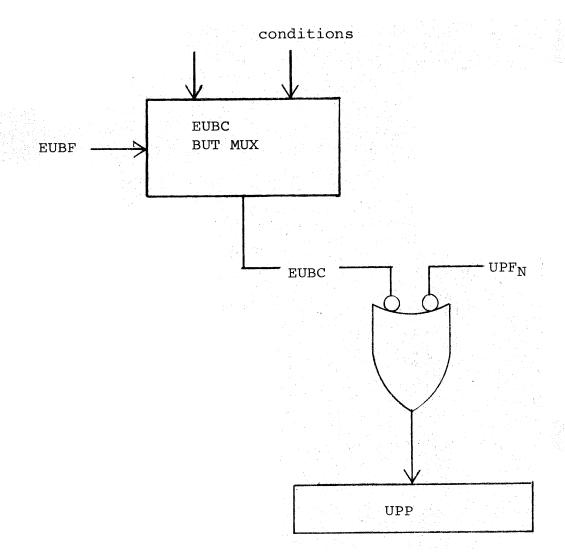

| 1. | It takes signals from the FLAG Control I REG and IR Decode to provide signals for the BUT MUX. |

|----|------------------------------------------------------------------------------------------------|

|    | Ans.                                                                                           |

|    |                                                                                                |

| 2. | It provides the controlling signals for the ALU                                                |

|    | Ans.                                                                                           |

| 3. | It provides the controlling signals for the D MUX.                                             |

|    | Ans.                                                                                           |

| 4. | Its output can be used to stop the processor at a particular micro instruction                 |

|    | Ans                                                                                            |

| 5. | Its contents specify the address of the microword currently in the UREG.                       |

|    | Ans.                                                                                           |

| 5. | It contains the machine instruction currently being executed by the 11/40.                     |

| 8. These lines indicate whether or not, and if so, what alterations of the base | 7. | Its output forces the micro program to a particular address without regard to the microinstruction currently being executed. |

|---------------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------|

|                                                                                 |    | Ans.                                                                                                                         |

| address will occur.                                                             | 8. | if so, what alterations of the base                                                                                          |

B.

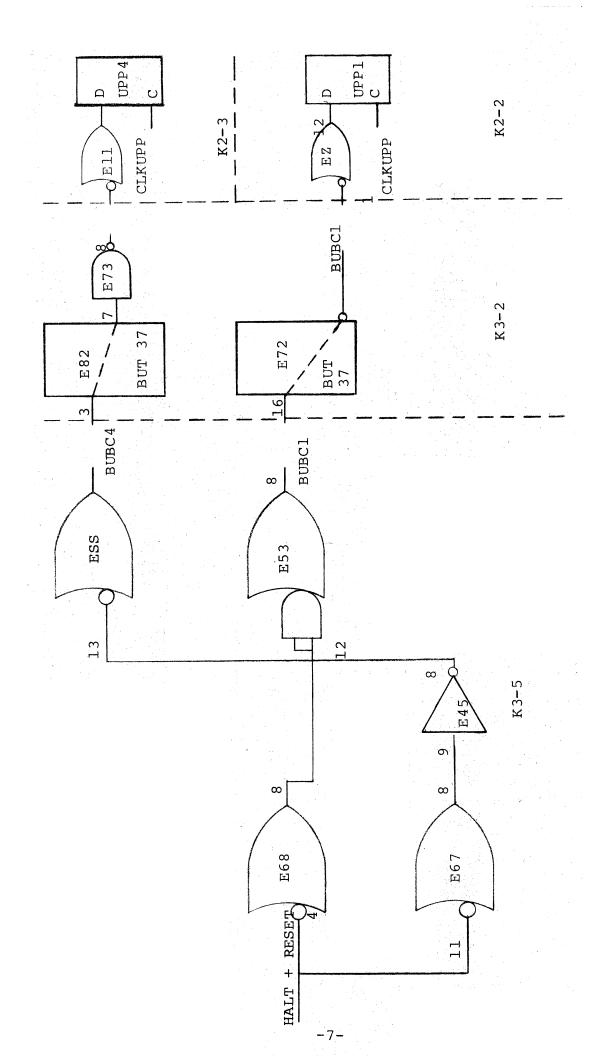

1. Which of the microinstructions drawn below would contain a BUT?

#### KD11A 020 000

C. Take the POST TEST. Do the best you can.

#### III. ADDITIONAL READING

To enhance your understanding of this unit, it is recommended that you read and study pages 3-18 through 3-20 in the KDllA Processor Maintenance Manual.

# WHAT'S NEXT

In the next unit you will complete your study of the Block Diagram. You will also have a chance to review the entire block.

#### KD11A 020 000

## APPENDIX A

#### LIST OF CONTROL SECTION FACILITIES

- 1. I REG

- 2. IR Decode

- 3. FLAG Control

- 4. UBC Branch Control

- 5. ALU Control MUX

- 6. ALUM, ALUS (3:0)

- 7. BUT MUX

- 8. JAMUPP

- 9. UPP

- 10. Main Control ROM

- 11. PUPP

- 12. SR: BUPP Compare

- 13. UPF (7:0)

- 14. U REG

- 15. U (15:09)

- 16. UBF (4:0)

- 17. BUT Decoder

# KD11A 020 000

#### APPENDIX B

#### ANSWERS TO PROBLEMS

- 1. UBC Branch Control

- 2. ALU Control MUX

- 3. U REG

- 4. SR: BUPP Compare

- 5. PUPP

- 6. I REG

- 7. JAMUPP

- 8. UBF (4:0)

# ANSUERS TO PROBLEMS

B.

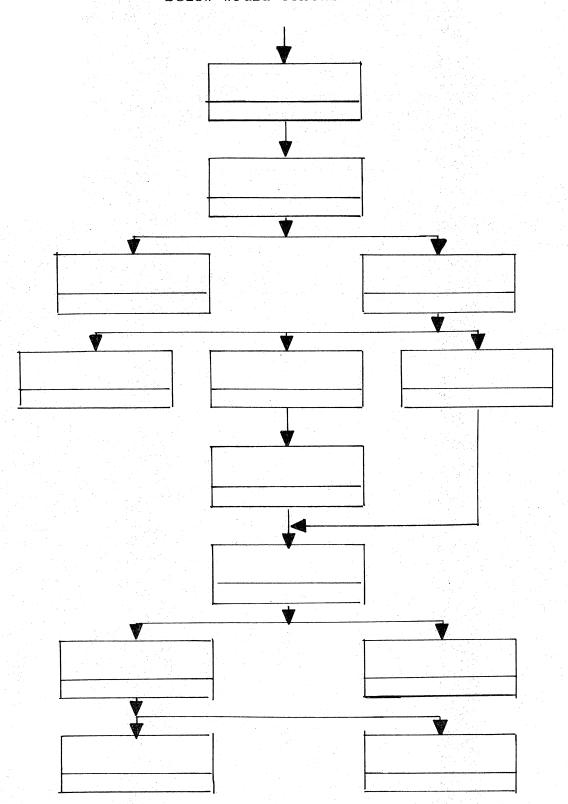

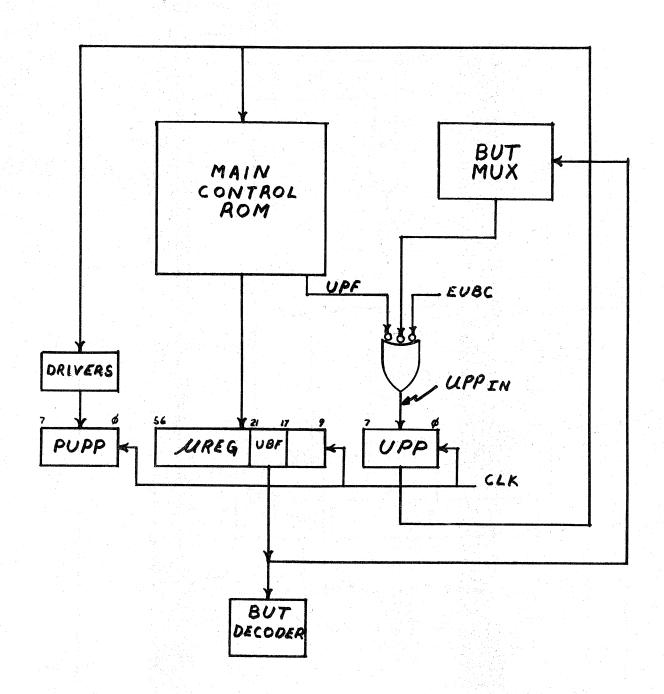

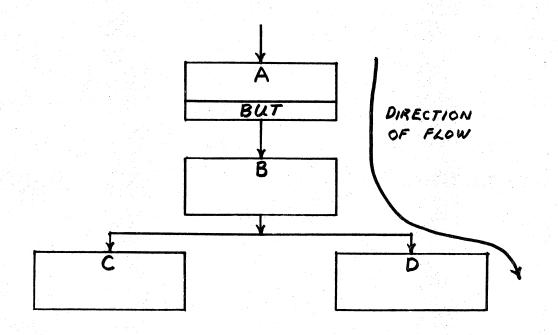

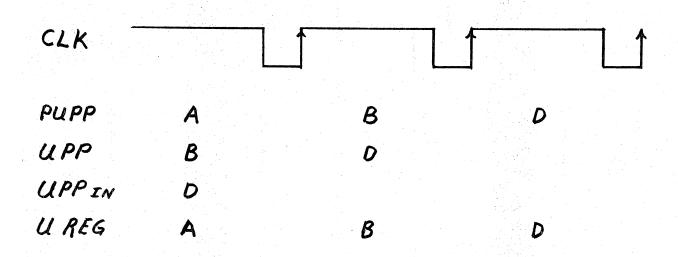

CONTROL SECTION SIMPLIFIED BLOCK DIAGRAM

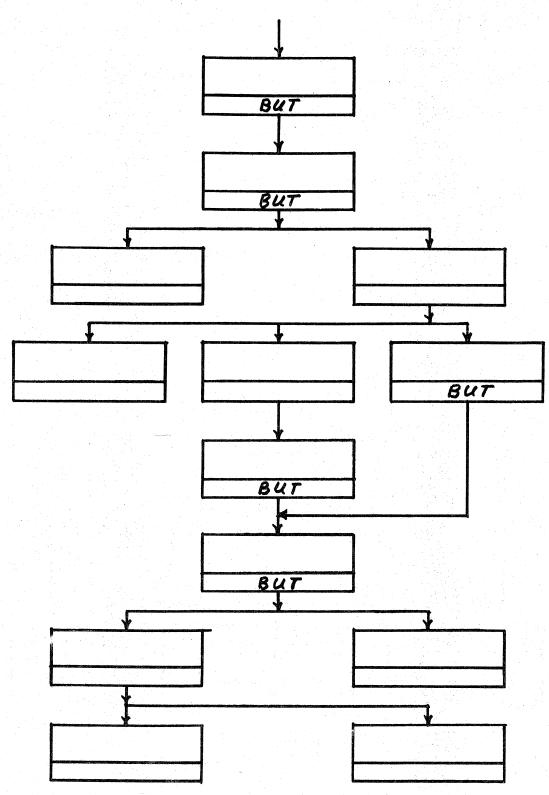

SIMPLIFIED MICROBRANCH CONTROL

EXAMPLE OF MICROBRANCHING

LEARNING ACTIVITY UNIT

KD11A BLOCK DIAGRAM

CLOCK, UNIBUS, CONSOLE

JANUARY 17, 1974

#### RATIONALE

By now you are pretty familiar with the 11/40 Block Diagram. You have seen how data is manipulated within the C.P. and also how the Control Section causes this manipulation to take place.

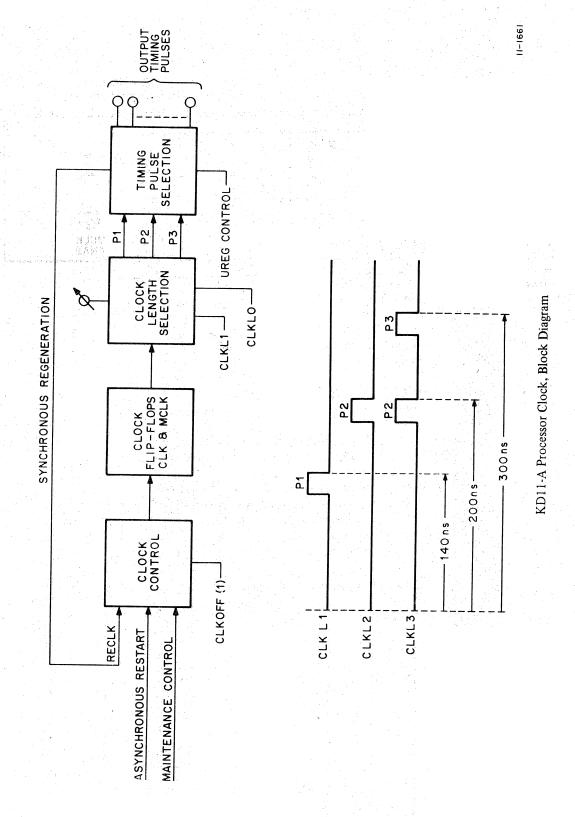

In this unit, you will cover the remaining parts of the Block Diagram. You will learn primarily how the 11/40 Processor clock operates and how these clocking signals are utilized within the Control and Data Path sections. You will also learn about such miscellaneous portions of the block as the Unibus Interface, Console Interface, etc. This unit will also serve as a review of the entire KD11A Block Diagram.

Use this unit to make sure that you really understand the Block Diagram. You will find it immensly useful as you study the flows and the logic as well as when you are troubleshooting.

#### PREREQUISITES

Successful completion of all units to date.

#### OBJECTIVES

Given a list of blocks or signals, you must be able to indicate which one would be faulty to generate the symptoms described. You must successfully complete three of the four questions in the alloted thirty minutes.

#### LEARNING ACTIVITIES

#### I. LECTURE

Attend the thirty minute lecture. Make notes on your block diagram. Do not ask your questions until the end of the lecture.

#### II. PROJECTS AND PROBLEMS

- A. Refer to Fig. 3-11 in your KDllA Processor

Maintenance Manual. Write down which signal

would be faulty to cause the following symptoms.

Check your answers with those in Appendix B.

Be sure to ask your instructor to clarify any

point you do not fully understand.

- 1. The machine is hung doing nothing and you observe no clocking signals. However, you are able to do all operations successfully using the maintenance board.

| 1 | Any micr | oinstr | uction | which   | specifies  | a CL2  |   |

|---|----------|--------|--------|---------|------------|--------|---|

|   | results  | in the | genera | ation o | of both a  | P2 and |   |

|   | a P3 pul | se. M  | icroin | structi | ions speci | fring  | _ |

| 7      |      |  |

|--------|------|--|

| Answer |      |  |

|        | <br> |  |

CL1 or CL3 operate properly.

- B. Refer to the list of Data Manipulation Functions in the Appendix of LAU# KD11A 010.000 and to your KD11A Block Diagram. Write the set of facilities including the clock length which would execute the following operations most efficiently. The answers are in Appendix B.

- 1. PC ← PC + 2

Answer

2.

- 2. R5 R3 + R5

- 3. Push the contents of the PC onto the Processor Stack.

- 4. Depressing the LOAD ADRS key

- C. Using the KDllA Block Diagram, find the signal which would be faulty to cause the following symptoms.

| 1. Whenever you do a LOAD | ADRS operation, you    |

|---------------------------|------------------------|

| observe on the ADDRESS    | DISPLAY that the upper |

| Byte is always changed    | to contain garbage.    |

| Answer     |  |

|------------|--|

| 7 22 20 20 |  |

2. Whenever the D Mux is enabled such that you see the contents of the D Reg in the Data Display, you see garbage. The same garbage is seen every time the D Mux is enabled in this way.

| Ans | we | r |  |  |  |  |

|-----|----|---|--|--|--|--|

|     |    |   |  |  |  |  |

3. You are trying to execute a program. After pressing and releasing the Start switch, the machine Halts. The same thing happens when you subsequently press CONT. You observe that the PC is incrementing properly and that Rl3 contains the instruction it should have executed.

| Ansv | ve | r | 100  |      |      |       |   |

|------|----|---|------|------|------|-------|---|

|      |    |   | <br> | <br> | <br> | <br>_ | - |

D. Take the Post Test. Do the best you can.

#### III. ADDITIONAL READING

To enhance your understanding of the Clock section, read and study pages 3-21 to 3-22 of the KD11A Processor Maintenance Manual. You should, at this time, be able to read and understand all of Chapter 3 from page 3-12.

#### WHAT'S NEXT?

You should now be well prepared to continue your study of the Flow Diagrams. If you have the Block well under your belt, you should have no problem with the flows.

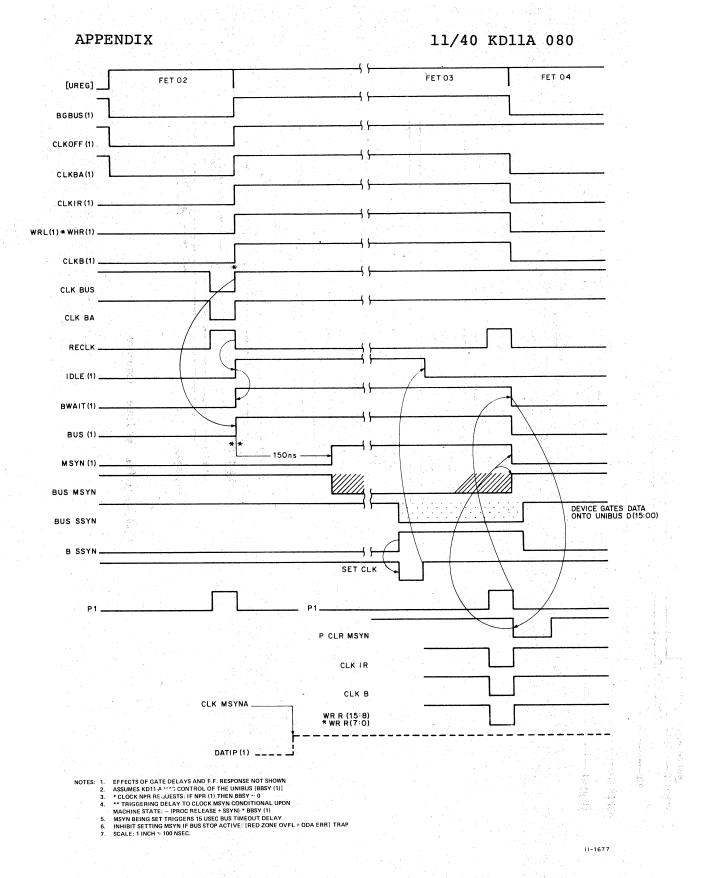

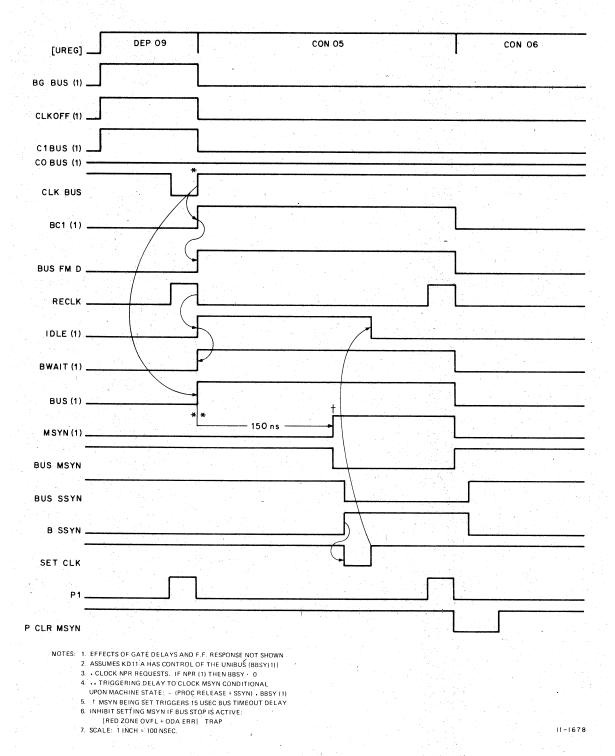

# REGISTER CLOCKING PULSES

| REGISTER | CLOCK  |

|----------|--------|

| I REG    | P1, P3 |

| B REG    | P1, P3 |

| D REG    | P2     |

| GPR      | P1, P3 |

| BA REG   | Pl, P2 |

#### ANSWERS TO PROBLEMS

Α.

- 1. RECLK

- 2. CLKLO

В.

1.  $PC \leftarrow PC + 2$

RIF (3:0) = 07

RA (3:0) ← RIF (3:0)

BCON (15:00) ← 2

BIN (15:00) ← BCON (15:00)

AIN (15:00) ← R (15:00)

CIN ← 0

ALUOUT = A PLUS B PLUS C

D (15:00) ← ALUOUT (15:00)

CLK D

DMUX (15:00) ← D (15:00)

R (15:08) ← D MUX (15:08)

R (07:00) ← D MUX (07:00)

WRH

WRL

CLKL3

- 2. R5 ← R3 + R5

- a. B ← R3

RA (3:0) ←IR (2:0)

D MUX (15:00) ←R (15:00)

B (15:00) ←D MUX (15:00)

CLK B

CLKL1

b. R5 ← B + R5 RA (3:0) ← IR (2:0) AIN (15:00) ← R (15:00) BIN (15:08) ← B (15:08) BIN (07:00) ← B (07:00)

#### ANSWERS TO PROBLEMS (CONT'D)

В,

2.

b. CIN ← 0

ALUOUT = A PLUS B PLUS CIN

D (15:00) ← ALUOUT (15:00)

CLK D

D MUX (15:00) ← D (15:00)

R (15:08) ← D MUX (15:08)

R (07:00) ← D MUX (07:00)

WRH

WRL

CLKL3

#### 3. $(SP) \downarrow \longrightarrow PC$

a. BA, SP ← SP - 2

RIF (3:0) = (06)RA  $(3:0) \leftarrow RIF (3:0)$ AIN  $(15:00) \leftarrow R (15:00)$ BCON (15:00) ← 2 BIN (15:00) ← BCON (15:00) ALUout = A MINUS B BA (15:00) \rightharpoonup ALUout (15:00) CLK BA D  $(15:00) \leftarrow ALUout (15:00)$ CLK D D MUX (15:00) ← D (15:00)  $R (15:08) \leftarrow D MUX (15:08)$  $R (07:00) \leftarrow D MUX (07:00)$ WRH WRL CLKL3

#### b. BUSD ← PC

RIF (3:0) = 07

RA (3:0) RIF (3:0)

AIN (15:00) R (15:00)

CIN 0

ALUOUT = A PLUS CIN

D (15.00) ALUOUT (15:00)

#### ANSWERS TO PROBLEMS (CONT'D)

В.

3.

b. CLK D CLKL2

(DATO)

- 4. LOAD ADRS

- a.  $R(17) \leftarrow SR$

RIF (3:0) = 17

RA (3:0) - RIF (3:0)

BUS D (15:00) - SR (15:00)

D MUX (15:00) - BUS D (15:00)

R (15:08) - D MUX (15:00)

R (07:00) - D MUX (07:00)

WRH

WRL

CLKL1

b. BA ← R(17)

RIF (3:0) = 17 RA (3:0) ← RIF (3:0) BA (15:00) ← R (15:00) CLKBA CLKL1

- C. 1. WRH

- 2. CLKD

- 3. CLKIR

# LEARNING ACTIVITY UNIT FLOW DIAGRAMS I INTRODUCTION OVERVIEW MINST FORMAT

### RATIONALE

So far you have learned about the Block Diagram and can now identify those areas of the block known as Data Paths, Control Section, Clock, Unibus Timing and Control. You can visualize, for instance, how some of the elementary operations are accomplished via the block like updating the PC, IR gets Unibus Data, etc. Now it is time to go one step farther and move on to the flows.

Probably everyone's definition of flow diagrams include something about a step by step explanation of an operation. Flows are designed to make some operation easily understandable. It usually consists of a set of symbols which must be identified and learned. The flows that you learned in the 11/05 were more like a listing and therefore, the ideas were there but not the symbology. This is not true, however, with the 11/40. Once we learn the "language of the flows" an attempt will be made to understand what the flows tell us concerning the 11/40's operation. Our primary objective in this unit then will be to learn how to "read" the flows.

The whole concept of the ROM control is captured in these flows. They identify and explain each micro instruction and show each possible sequence. Acquiring this reading the flows ability will provide you with the proper foundation to continue with the subsequent units concerning the flows.

### PREREQUISITES

Satisfactory completion to date of all previous units.

# **OBJECTIVES**

Given four flow machine state blocks with various amounts of information you must identify and define which micro instruction field is involved to select or make happen the questioned operation. To successfully complete this unit, you must correctly answer three of four of these questions. You will be allowed to use all available references and your notes but a twenty (20) minute time limit will be in effect.

# PRETEST

To be filled in when fully programmed environment is in progress.

# LEARNING ACTIVITIES

### I. LECTURE

Attend a 20 minute lecture where the instructor will give you an overview of the microprogram flows. He will point out to you the various places you will find information about the flows, and talk in general terms about the ideas and concepts behind them. The emphasis will be on how to use the flows in a maintenance and learning environment. Time will be allowed at the end of this lecture to answer questions prior to going on to your activities.

# II. PROJECTS/QUESTIONS

### A. Micro instruction format

As you already know, the 11/40 is a "ROM" machine. This means that all controlling of the machine operations are accomplished by micro instructions. These micro instructions are 56 bits in length and there are 256 of them.

- Identify, define, describe each of the 56 bits of a micro instruction. A complete detailed description appears in the appendix. A ready reference appears in the:

KD11A Processor Maintenance Manual DEC11 HKDAA-A-D, Pg. 2-7 Fig, 2-4, Pg. 2-8, 2-9 Table 2-1

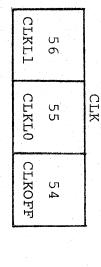

- 2. Note how the bits are grouped into the various fields, that is; the CLKL 1, CLKLO and CLKOFF grouped together to become a field called CLK. Note all fields by referring to KDllA Processor Maintenance Manual DEC11-HKDAA-A-D, pg 2-6 Fig. 2-3

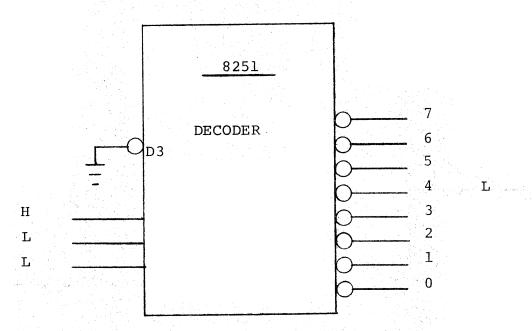

- 3. Refer to the 6th page in the PDP11/40 System Engineering Drawings and look over the tables found there. Each of the major field's uses are given by these tables. For instance when the BUS code is equal to 5, what type of bus transaction will be initialized; answer DATO.

- 4. Now familiarize yourself with the ROM (micro instruction) listing in the PDP11/40 System Engineering Drawings found on about the 22nd page just after the K2 print set.

- 5. Refer to your block diagram, now and identify some of these fields as to where they feed and what they control

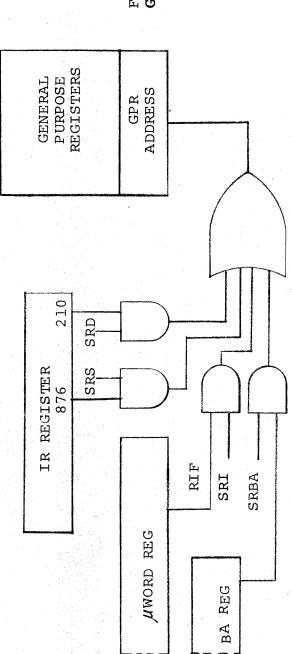

- a. SRI and RIF to select some general purpose register

- b. SBC to generate a constant

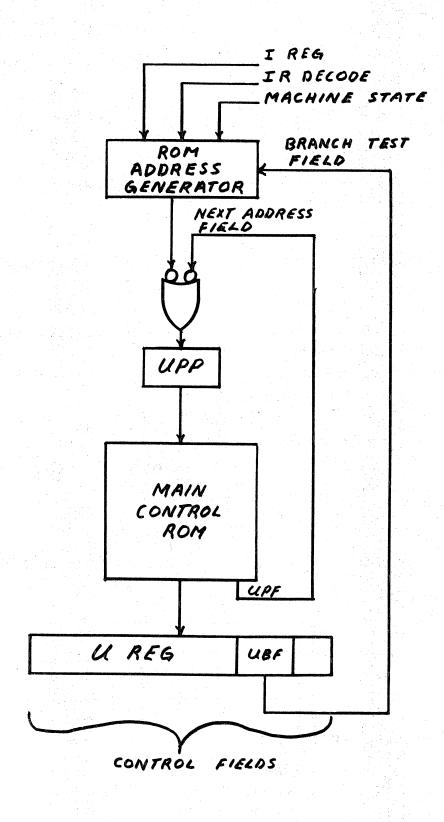

- c. UPF to affect the UPP register

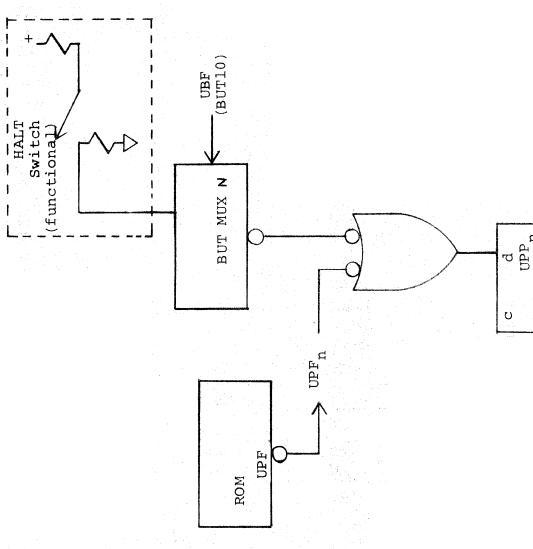

- d. UBF to control the BUT multiplexer

- 6. The SBC code will be equal to when generating a constant of two (2).

- 7. When attempting to address R[PC] using SRI and the RIF bits, SRI is on a 1 and RIF equals \_\_\_\_\_.

- 8. When DAD says use the micro instruction to set up the ALU and we want the ALU to add, the ALU field equals .

- 9. The BUT decoder looks at the field to translate the BUT number.

- 10. A BUT 12 really asks this question is

### B. Micro program Flow

1. Only three basic symbols are used in the PDP11/40 Flow diagrams, they are given here and on pg 4-1 of the KD11A Processor Maintenance Manual DEC11-HKDAA-A-D.

Machine State

Exit Point

- 2. The most involved symbol of course is the machine state (one micro instruction) Refer now to the appendix and familiarize yourself with every aspect of this flow symbol.

- 3. Each machine state box reporesents one micro instruction, one elementary operation, one small step necessary for the overall accomplishment of a machine operation.

- 4. A machine operation could be;

- a. To load an address

- b. To examine a register

- c. To execute a machine instruction

- d. Etc.

- 5. Read pages 4-1 thru 4-4 in the KD11-A Processor Maintenance Manual DEC 11-HKDAA-A-D with special emphasis on the flow diagram example figure 4-2 on page 4-2

- 6. Start (1) indicates to you that start is a (condition/flip flop)

- 7. The signal HALT SW is read as

- 8. Referring to fig 4-2, page 4-2 in KD11A Processor Maintenance Manual DEC11-HKDAA-A-D

- a. What flow sheet do you go to if HALT switch is sensed

- b. What address is Fetch C

- 9. Check your answers to A and B in the appendix. Get help if you do not understand why you missed any of the one's you did.

### III. SELF EVALUATION

A. Given the following Micro instruction flow example, answer the questions

| SRC  | 09         |                      | 147                                                             |

|------|------------|----------------------|-----------------------------------------------------------------|

| GE T | INDEX      | DATA; MODIFY         | D                                                               |

| P2:  | D&R[PC     | c] plus 2            |                                                                 |

| P3:  | R[PC]      | ← D; CLKOFF          |                                                                 |

|      | GET<br>P2: | GET INDEX P2: D€R[PC | GET INDEX DATA; MODIFY P2: D&R[PC] plus 2 P3: R[PC] & D; CLKOFF |

- 1. What is the clock code?

- 2. If D=500 and R[PC] =500

What is the Data Display?

- 3. The SBM field will equal

- 4. What method will be used to address R[PC].

- 5. The PC will be written with the updated value and the next micro instruction clocked into the Register at the trailing edge of the \_\_\_\_\_clock specified.

### IV. ADDITIONAL READING

To assist in you understanding, the flow diagrams reading chapter two (2) of the KD11A Processor Maintenance Manual DEC11 - HKDAA A-D will be of some value. You should consider this for a more detailed understanding.

# WHAT'S NEXT

After completing this unit, you will be prepared to continue on to the remaining units concerned with the 11/40 flow diagrams armed with the necessary knowledge knowing how to "read the FLows".

| A   | FET 04                                                   | <sup>B</sup> 004 |                  |

|-----|----------------------------------------------------------|------------------|------------------|

|     | © MODIFY R[PC] ; OVERLAP                                 | (D) R [PC]       |                  |

|     |                                                          |                  |                  |

|     | $\stackrel{(E)}{=}$ P2: D, BA $\leftarrow$ R[PC] PLUS 2: |                  |                  |

| i i | DATI IF OVERLAP FETCH                                    |                  |                  |

|     | E BUT (INSTR 1)                                          | © BUT 37         | ⊕ <sub>100</sub> |

- A. Name of Micro instruction (Mnemonic)

- B. The ROM address of the Minstruction (9 bits (PUPP))

- C. What the µinstruction will do. I.E. modify the program counter and start a BUS Cycle if overlap.

- D. The Console Data Display. This is read R of PC. Therefore, this Data Display is the contents of R[PC].

- E. What happens and when. This particular one means, at the trailing of the P2 pulse specified D Reg. and BA Reg., get the results of R[PC] plus 2, and start a DATI BUS Cycle if you meet the conditions for an overlap fetch. This is read as, at P2 time D and BA gets R[PC] plus 2 and start a DATA IN if overlap.

- F. Branch Micro test name. This one, but (instr 1), means this is first time you look at the <u>machine</u> instruction to make micro program branch decision.

- G. But Number. Give you the octal  $\mu$ BF code, let you refer to this BUT by number.

- H. This is the base address that the micro test will put in jeopardy. It is possible that any or all of BITS (5:0) will be modified due to conditions being sampled (tested).

| 10 9<br>RIF1 RIFO | When SPI is active these bits (register immediate field) are used to provide the address for the general purpose registers. |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 11<br>RIFZ        | When SPI is active (register immediate used to provide the the general purpose                                              |

| 12<br>RIF3        | When SPI<br>(registe<br>used to<br>the gene                                                                                 |

| L13<br>SRI        | Allows RIF to be used (select the GPR using the RIF field)                                                                  |

| 14<br>SRBA        | Allows bits (3:0) of the BA Reg. to address the GPR's.                                                                      |

| 15<br>SRD         | Allow IR destination field to address the GPR's.                                                                            |

| 16<br>SRS         | Allows IR source field to address the GPR's                                                                                 |

Functional representation of GPR addressing.

| •  |      |

|----|------|

|    | UBF0 |

|    | UBF1 |

| 19 | UBF2 |

| 20 | UBF3 |

| 21 | UBF4 |

Micro branch field - better known as BUT. It's this field that will select one of many inputs to be routed through the but mux, such that, that condition could modify the UPF bit depending on the fact if it's true or not.

BUT's asks question for instance, a but 10 called but (halt) says but is the halt switch on?

BUT 17, BUT IR03, BUT is IR bit 3 on a 1?

| 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27    | 26    | 25    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|

| SBMH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SBMH0 | SBML1 | SBML0 |

| Constitution of the Party of th |       |       |       |

28 & 27 select the input to the high byte of the B MUX. Bits 26 & 25 select the input to the LO byte of the B MUX. Bits Select the B MUX field.

| 23 | S DM0 |

|----|-------|

| 24 | SDM1  |

of the 4 inputs to be routed through the D MUX. These bits select which Select the D MUX field.

|     |        |          |       | •     |

|-----|--------|----------|-------|-------|

| MUX | Ø      | BUS      | put   | ister |

| BA  | routes |          | outpr | Regi  |

| the | ų      | the      | ALU   | BA    |

| G   | s bi   | ther     | the   | the   |

| 3e1 | ľhi    | 91.<br>t | Σ     | S     |

t

SBAM 22

> the KD11A Processor Maintenance See table 3-1 on page 3-14 in Manual DEC11-HKDAA-A-D for a complete listing of multiplexer selections.

# MICRO INSTRUCTION FORMAT PDP11/40

Z

| - | Maritania (Maria) |       |

|---|-------------------|-------|

|   | 33                | SALUO |

|   | 34                | SALUL |

|   | 35                | SALUZ |

|   | 36                | SALU3 |

|   | 37                | SALUM |

SBC

| 32   | 31   | 30   | 29   |

|------|------|------|------|

| SBC3 | SBC2 | SBC1 | SBC0 |

These bits select which mode the ALU should function in and what it should do. I.E. Add, etc. see table 3-2, page 3-17 in the KD11-A Processor Maintenance Manual for complete list of ALU selections.

Select Binary Constants field This bit generates necessary constants needed by the 11/40. See SBC table about 6th page in PDP11/40 System Engineering Drawings for a complete list.

DAD

| 4.1 | DADO |  |

|-----|------|--|

| 4.2 | DAD1 |  |

| 43  | DAD2 |  |

| 44  | DAD3 |  |

Discrete alteration of data.

Does some special jobs in the logic for us. For instance, the micro program would go through the same sequence if the machine instruction was an Add or Sub. However, at that one micro instruction that the ALU actually operates on the two operands the DAD code allows the ALU to be told what to do (Add or Sub) by the OP code in the IR Register.

SPS

| 40   | 39   | 38   |

|------|------|------|

| SPS2 | SPS1 | SPS0 |

Select the processor status code. These bits control the gating and clocking of the processor status flip flops.

A complete table of "DAD" and "SPS" is found about the 6th page of the PDP11/40 System Engineering Drawings.

# MICRO INSTRUCTION FORMAT PDP11/40

|     |                        |                                                                                        | DATI<br>DATIP<br>DATO<br>DATOB |

|-----|------------------------|----------------------------------------------------------------------------------------|--------------------------------|

|     | 45<br>BG BUS           | bits. 146 0e of action                                                                 | 1000                           |

| BUS | 46<br>0 BUS            | BUS Control bits. Bits 47 and 46 specify type of data transaction                      | 0011                           |

|     | 47 46<br>Cl BUS CO BUS | BUS<br>Bits<br>spec<br>data                                                            | <b>1</b>                       |

|     |                        | Allows clocking either the ALU output or a general register ouput into the BA Register | Do To BA REG                   |

| CBA | 48<br>CLKBA            | Allows<br>either<br>output<br>registe<br>the BA                                        | TO CLKBA                       |

| CD  | 49<br>CLK D            | Allows clocking<br>the ALU output<br>into the D Register                               | CLKD TO TO P2                  |

| CB  | 50<br>CLK B            | Allows clocking<br>DMUX (15:00) into<br>the B Register                                 | CLKB To To B REG Pl + P3       |

|       | DATI<br>DATIP<br>DATO<br>DATOB |

|-------|--------------------------------|

| COBUS | 0-10-1                         |

| CIBUS | ООНН                           |

Bit says to <u>BEGIN</u> a BUS Cycle

This is a three bit code given as one octal digit in the ROM

listing. This code has a supplementary use - explained with tables.

CLKL1

CLKLO

-00

CLK CLK

CLKIR

CLK IR

WRH

To

GPR's

CIR

one of three clock Clock Control

Bit 56 and 55 lengths. bits select

with Unibus Data the machine instruction. instruction register Allows clocking the

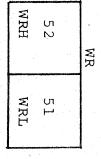

byte. a control signal for upper byte and lower purpose register. a selected general Allows the writing of DMUX information into Notice

6

This is a three bit code given as one octal digit in the ROM listing.

PI

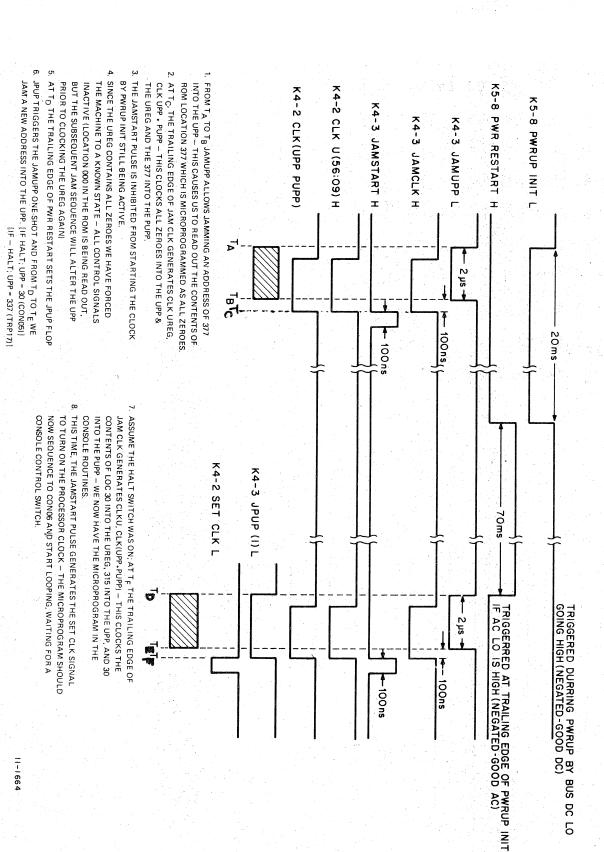

+ E B WRL