# VAX Architecture Handbook 1986

Digital believes the information in this publication is accurate as of its publication date; such information is subject to change without notice. Digital is not responsible for any inadvertent errors.

The following are trademarks of Digital Equipment Corporation:

| DEC       | PDP          | RT             |

|-----------|--------------|----------------|

| DECmate   | P/OS         | UNIBUS         |

| DECUS     | Professional | VAX            |

| DECwriter | Rainbow      | VMS            |

| DIBOL     | RSTS         | VT             |

| MASSBUS   | RSX          | Work Processor |

| MicroVAX  |              |                |

And the Digital Logo: digital

Copyright © 1986 Digital Equipment Corporation. All Rights Reserved.

## **CONTENTS**

| Preface                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 • VAX Architecture Design          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Introducing VAX Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Virtual Address Extension                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PDP-11 Computer Compatibility Option         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Memory Management                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Additional Literature                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Tuditional Interactic                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 2 • VAX Architecture Overview        | e de la companya de l |

| Processing Concepts                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Context Switching                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Priority Dispatching                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

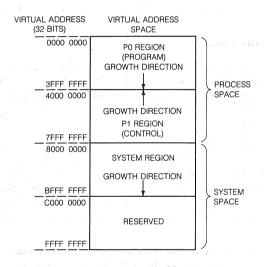

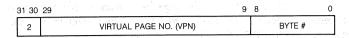

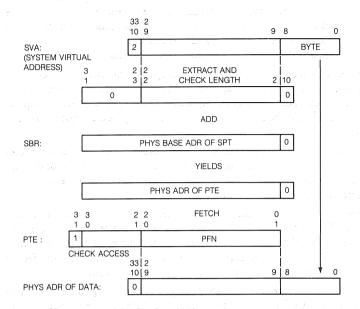

| Virtual Addressing                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

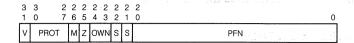

| Memory Management                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Instruction Set                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

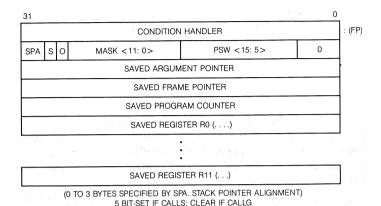

| Routine Call Capability                      | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Instruction Operand Processing               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Process Control Instructions                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| General Register Addressing                  | 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Data Types                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Stacks                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Condition Codes                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Exceptions and Interrupts                    | 2-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input/output Control                         | 2-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 3 • VAX Architecture Characteristics |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Programming Environment                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

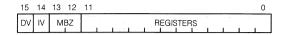

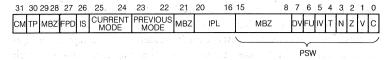

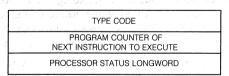

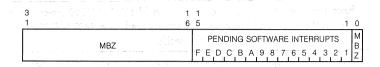

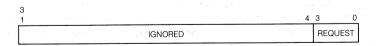

| Processor Status Longword                    | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Processor Access Modes                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Special Instructions                         | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Data Sharing                                 | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Data Acassa Symphyonization                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Registers                                   |

|---------------------------------------------|

| General Registers                           |

| Processor Registers                         |

| Input/output Registers3-13                  |

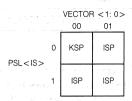

| Stacks                                      |

| Cache Memory                                |

| Restartability3-17                          |

| Interrupts and Errors                       |

|                                             |

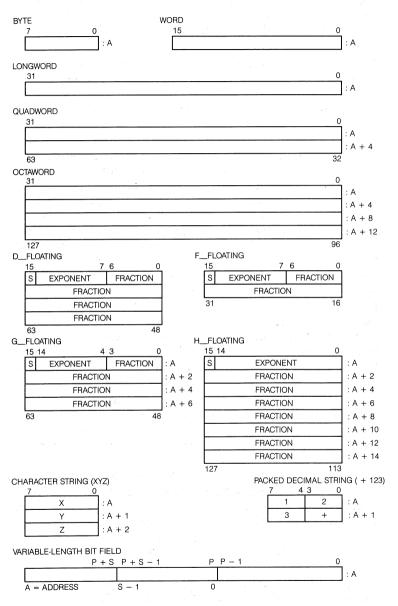

| Chapter 4 • Data Representation             |

| Character String Data4-1                    |

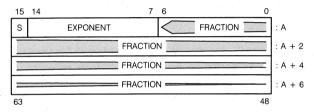

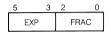

| Floating-point Data4-2                      |

| D floating Data4-2                          |

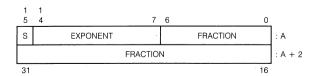

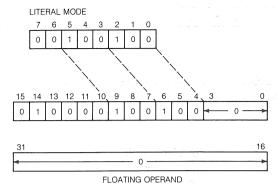

| F_ floating Data4-3                         |

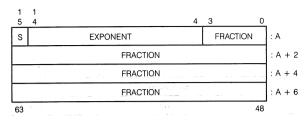

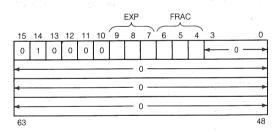

| G floating Data4-4                          |

| H floating Data4-5                          |

| Integer Data4-6                             |

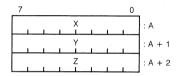

| Byte Data4-7                                |

| Word Data4-7                                |

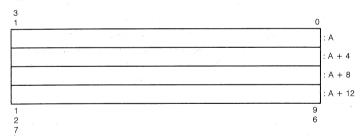

| Longword Data4-8                            |

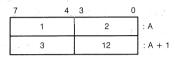

| Quadword Data4-8                            |

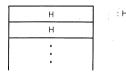

| Octaword Data 4-9                           |

| Numeric String Data4-10                     |

| Leading Separate Numeric String Data4-10    |

| Trailing Numeric String Data4-12            |

| Packed Decimal String Data4-16              |

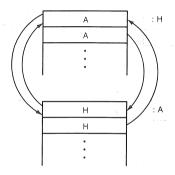

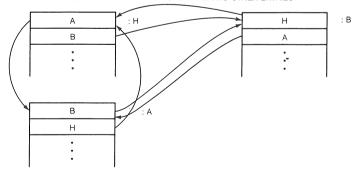

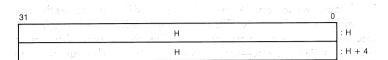

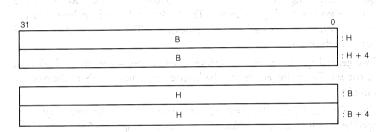

| Queue Data4-17                              |

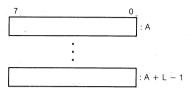

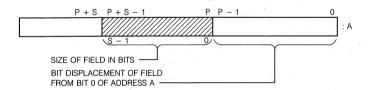

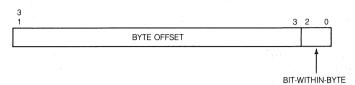

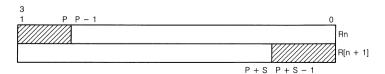

| Variable Length Bit Field Data4-21          |

| Data in Registers4-24                       |

|                                             |

| Chapter 5 • The Instruction Characteristics |

| Notation Convention5-1                      |

| Assembler Notation5-1                       |

| Operand Notation5-1                         |

| Operation Notation5-2                       |

| Range and Extent Notation                   |

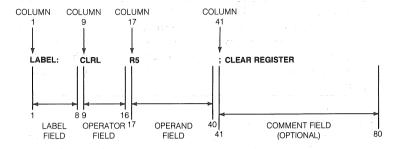

| MACRO Source Statement Format5-5            |

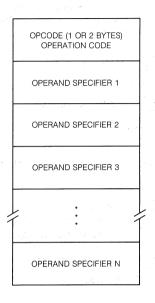

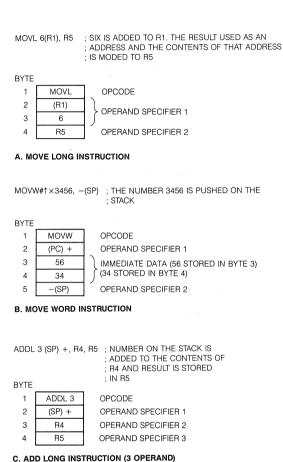

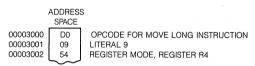

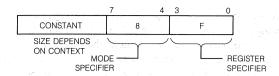

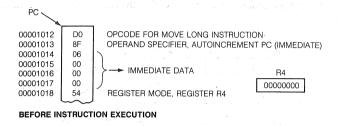

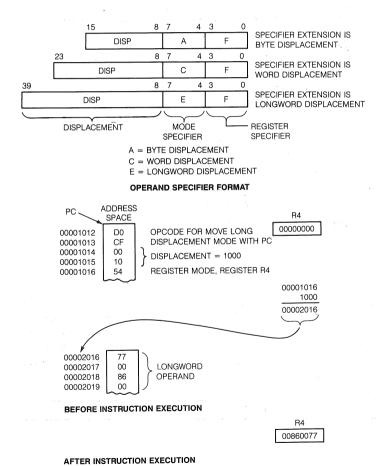

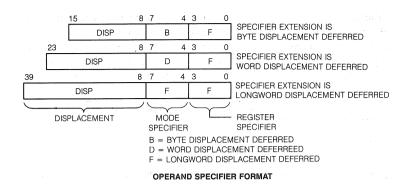

| Instruction Format5-6                       |

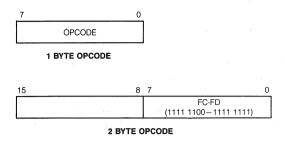

| Operator Field5-8                           |

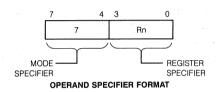

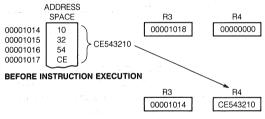

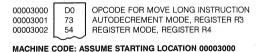

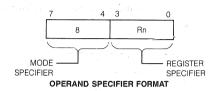

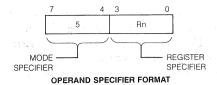

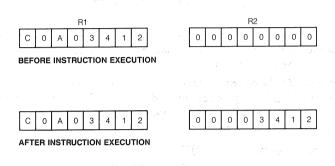

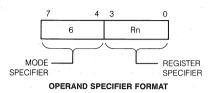

| Operand Field 5-9                           |

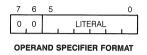

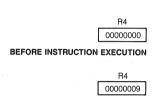

| General Mode Addressing Branch Mode Addressing  Chapter 6 • Functions of the Instruction Set  Address Instructions Arithmetic Instructions Character String Instructions Control Instructions Case Instructions Loop Control Instructions Subroutine Call Instructions Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instructions Index Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions Self-relative Queue Instructions | 5-41<br>6-1<br>6-2<br>6-3<br>6-4<br>6-4 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Chapter 6 • Functions of the Instruction Set  Address Instructions Arithmetic Instructions Character String Instructions Control Instructions Case Instructions Loop Control Instructions Subroutine Call Instructions Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                 | 6-1<br>6-2<br>6-3<br>6-4<br>6-4         |

| Address Instructions Arithmetic Instructions Character String Instructions Control Instructions Case Instructions Loop Control Instructions Subroutine Call Instructions Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                   | 6-2<br>6-2<br>6-3<br>6-4<br>6-4         |

| Arithmetic Instructions Character String Instructions Control Instructions Case Instructions Loop Control Instructions Subroutine Call Instructions Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                                                                    | 6-2<br>6-2<br>6-3<br>6-4<br>6-4         |

| Character String Instructions Control Instructions Case Instructions Loop Control Instructions Subroutine Call Instructions Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                                                                                            | 6-2<br>6-3<br>6-4<br>6-4                |

| Control Instructions Case Instructions Loop Control Instructions Subroutine Call Instructions Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                                                                                                                          | 6-3<br>6-4<br>6-4                       |

| Case Instructions Loop Control Instructions Subroutine Call Instructions Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                                                                                                                                               | 6-4<br>6-4<br>6-4                       |

| Loop Control Instructions Subroutine Call Instructions Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                                                                                                                                                                 | 6-4<br>6-4                              |

| Subroutine Call Instructions Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                                                                                                                                                                                           | 6-4                                     |

| Transfer Instructions Cyclic Redundancy Check Instruction Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                                                                                                                                                                                                                        |                                         |

| Cyclic Redundancy Check Instruction Decimal String Instructions  Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                                                                                                                                                                                                                                             | , -                                     |

| Decimal String Instructions Edit Instruction Floating-point Instructions Index Instruction Integer Instructions Logic Instructions Multiple Register Instructions Privileged Instructions Procedure Call Instructions Processor Status Longword Instructions Queue Instructions Absolute Queue Instructions                                                                                                                                                                                                                                                                                                                                                                  |                                         |