#

Architecture Handbook

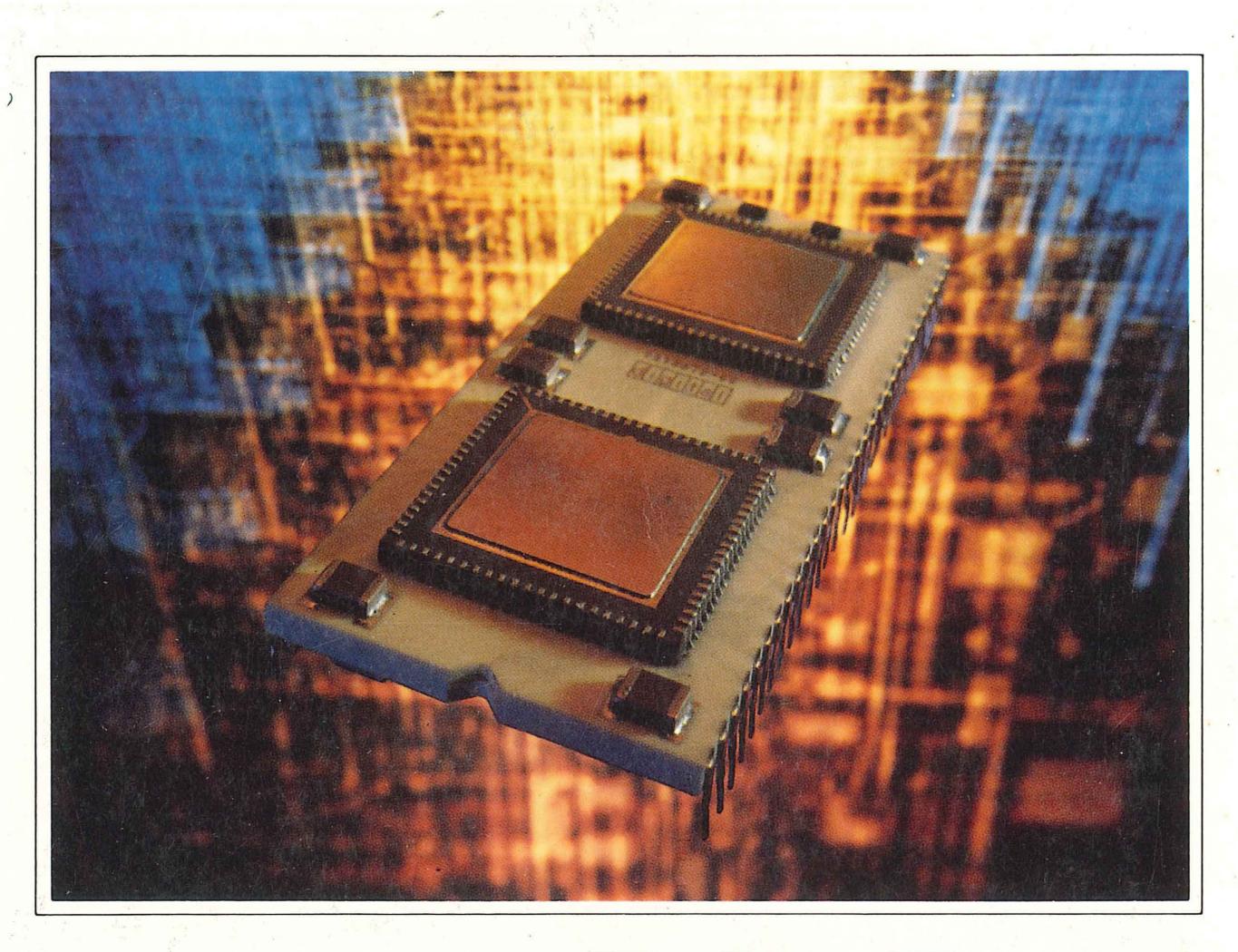

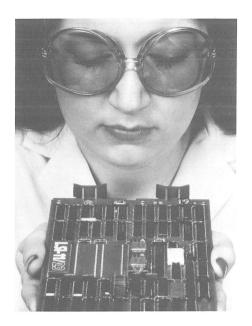

The J-11 chipset.

The PDP-11/70 system.

The tradition continues with the J-11, DIGITAL's newest high-performance microprocessor. It offers the architecture, power, and functions of the PDP-11/70 (the PDP-11 family performance leader) in a single 60-pin package. The J-11 will form the basis of a new line of DIGITAL products. These powerful systems will carry the PDP-11 architecture years into the future.

# PDP-11

Architecture Handbook

## Copyright© 1983 Digital Equipment Corporation. All Rights Reserved.

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

DEC, DECnet, DECsystem-10, DECSYSTEM-20, DECtape DECUS, DECwriter, DIBOL, Digital logo, IAS, MASSBUS, OMNIBUS PDP, PDT, RSTS, RSX, SBI, UNIBUS, VAX, VMS, VT are trademarks of Digital Equipment Corporation

> This handbook was designed, produced, and typeset by DIGITAL's New Products Marketing Group using an in-house text-processing system.

### **TABLE OF CONTENTS**

| CHAPTER 1 ARCHITECTURE AND THE PDP-11 FAMILY  |          |

|-----------------------------------------------|----------|

| INTRODUCTION                                  | . 1      |

| THE PDP-11 FAMILY CONCEPT                     | . 3      |

| PDP-11 ARCHITECTURE AND SYSTEM PERFORMANCE    | . 5      |

| EVOLUTION OF THE PDP-11                       | . 6      |

| PDP-11 MILESTONES                             | . 8      |

| EVOLUTION OF THE LSI-11                       | 11       |

| PDP-11 FAMILY ALBUM                           | 13       |

| CHAPTER 2 KEY ELEMENTS OF PDP-11 ARCHITECTURE |          |

| INTRODUCTION                                  | 27       |

| DATA REPRESENTATION                           | 27       |

| ADDRESSING AND REGISTERS                      |          |

| INSTRUCTION SETS                              |          |

| TRAPS AND INTERRUPTS                          | 30       |

| MAPPING TO MEMORY AND BUSSES                  | 30       |

| PDP-11 BUS STRUCTURES                         | 31       |

| OTHER TOPICS (APPENDICES)                     | 31       |

| CHAPTER 3 PDP-11 DATA REPRESENTATION          |          |

| INTEGER DATA TYPES                            | 35       |

| CHARACTER DATA TYPES                          | 36       |

| DECIMAL STRING DATA TYPES                     | 38       |

| FLOATING-POINT DATA FORMATS                   | 49       |

| PLOATING-FOINT DATAT ORIGINATO                |          |

| CHAPTER 4 ADDRESSING MODES                    |          |

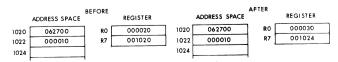

| REGISTER MODE                                 | 56       |

| REGISTER DEFERRED MODE                        | 57       |

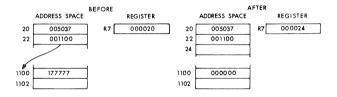

| AUTOINCREMENT MODE                            | 58       |

| AUTOINCREMENT DEFERRED MODE                   | 59       |

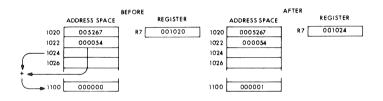

| AUTODECREMENT MODE                            | 59       |

| AUTODECREMENT DEFERRED MODE                   |          |

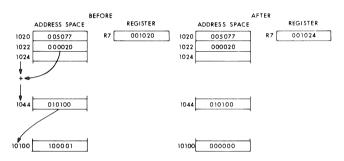

| INDEX MODE                                    | 61       |

| INDEX DEFERRED MODE                           | 01       |

| USE OF THE PC AS A GENERAL REGISTER           | 62       |

| PC IMMEDIATE MODE                             | 63       |

| PC ABSOLUTE MODE                              | 04<br>64 |

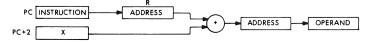

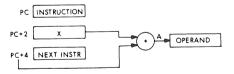

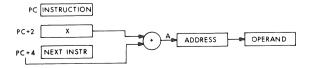

| PC RELATIVE MODE                              | 04       |

| PC RELATIVE DEFERRED MODE                     | 00       |

| SUMMARY OF ADDRESSING MODES                   |          |

| GRAPHIC SUMMARY OF PDP-11 ADDRESSING MODES    | บฮ       |

| CHAPIER 5 INSTRUCTION SET                     |              |

|-----------------------------------------------|--------------|

| SINGLE-OPERAND INSTRUCTIONS                   | . 73         |

| DOUBLE-OPERAND INSTRUCTIONS                   | . 74         |

| BRANCH INSTRUCTIONS                           |              |

| JUMP AND SUBROUTINE INSTRUCTIONS              | . 77         |

| TDADS AND INTERRIDES                          | <br>78       |

| TRAPS AND INTERRUPTS                          | . 70<br>70   |

| WISCELLANEOUS INSTRUCTIONS                    | . 70         |

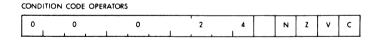

| CONDITION CODE OPERATION                      | . 19         |

| EXAMPLES                                      | . 01         |

| NSTRUCTION SET                                | . 83         |

| SPECIAL SYMBOLS                               |              |

| SUMMARY OF PDP-11 INSTRUCTION SET             |              |

| TABLE OF THE PDP-11 INSTRUCTION SET           | . 87         |

|                                               |              |

| CHAPTER 6 PDP-11 FLOATING-POINT               | 405          |

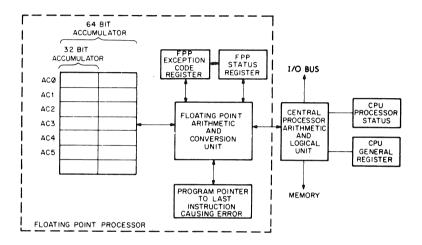

| NTRODUCTION                                   | . 125        |

| ARCHITECTURE                                  |              |

| OPERATION                                     | . 126        |

| FLOATING-POINT STATUS REGISTER (FPS)          |              |

| FLOATING EXCEPTION CODE AND ADDRESS REGISTERS | . 131        |

| FLOATING-POINT OPTION INSTRUCTION ADDRESSING  | . 132        |

| ACCURACY                                      | . 133        |

| FLOATING-POINT INSTRUCTIONS                   | . 134        |

|                                               |              |

| CHAPTER 7 COMMERCIAL INSTRUCTION SET          |              |

| CHARACTER STRING INSTRUCTIONS                 | . 164        |

| DECIMAL STRING DESCRIPTORS                    |              |

| DECIMAL STRING INSTRUCTIONS                   | 168          |

| NSTRUCTION SUSPENSION                         | 172          |

| TABLE OF INDIVIDUAL INSTRUCTIONS              | 17/          |

| TABLE OF INDIVIDUAL INSTRUCTIONS              | . 177        |

| CHAPTER 8 TRAPS AND INTERRUPS                 |              |

| PROCESSOR TRAPS                               | . 211        |

| TRAP INSTRUCTIONS                             | 212          |

| NTERRUPTS                                     |              |

| NIERROPIS                                     | . 213        |

| CHAPTER 9 MAPPING TO MEMORY AND BUSSES        |              |

| NTRODUCTION                                   | 222          |

| CONCEPTS                                      | 222          |

| MEMORY MANAGEMENT                             |              |

| VIEWONT WANAGEWENT                            | . ८८4<br>१२० |

| ACTIVE PAGE REGISTERS                         | . 20U        |

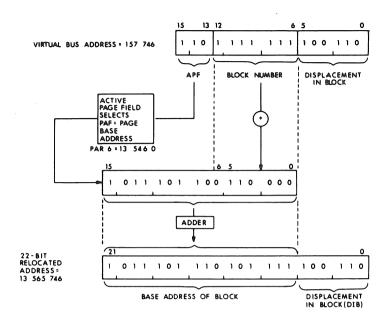

| PHYSICAL ADDRESS CONSTRUCTION                 |              |

| MAPPING                                       | . 240        |

| I/O EXTENDED ADDRESSING                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

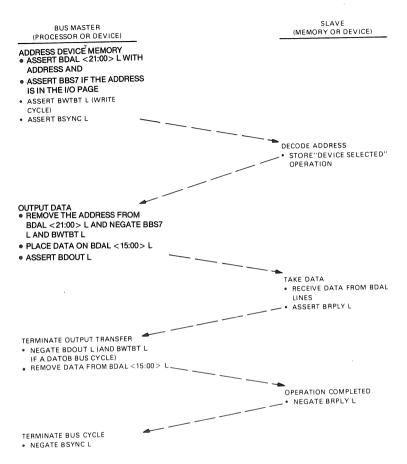

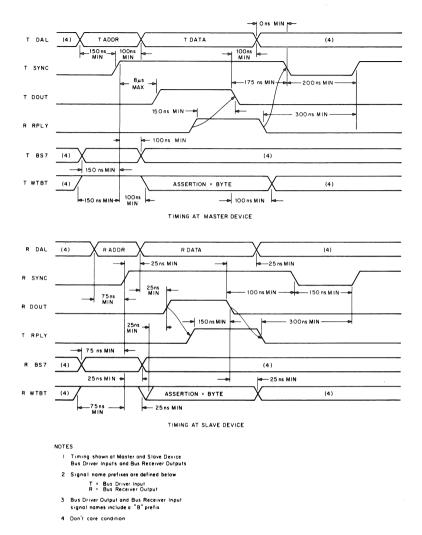

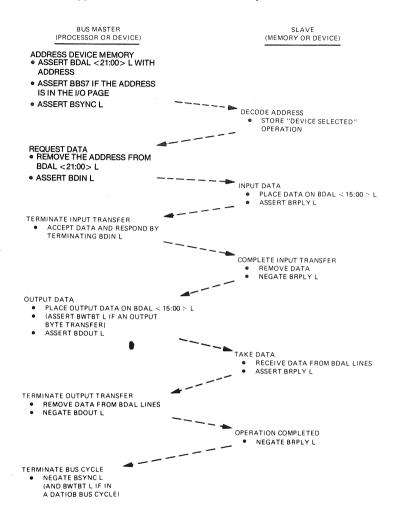

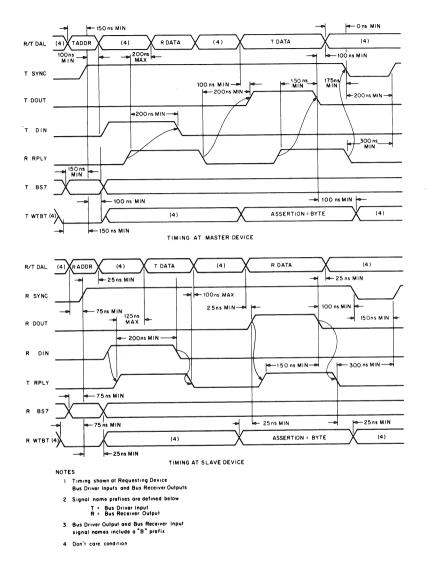

| CHAPTER 10 PDP-11 BUS STRUCTURES           INITIALIZATION         267           ARBITRATION         268           DATA         268           MISCELLANEOUS         271           BUS TIMING         271           BUS ERRORS         272 |

| APPENDIX A ASSIGNMENT OF ADDRESSES AND VECTORS . A-1                                                                                                                                                                                     |

| APPENDIX B PDP-FAMILY DIFFERENCES                                                                                                                                                                                                        |

| APPENDIX C THE FIS INSTRUCTION SET                                                                                                                                                                                                       |

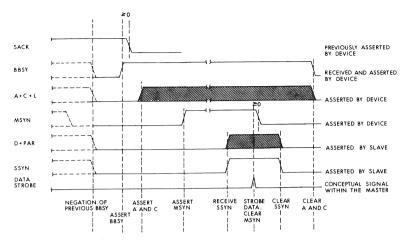

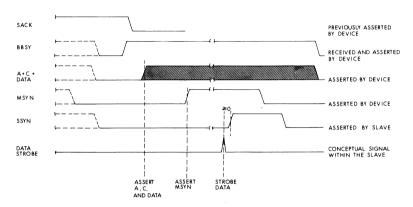

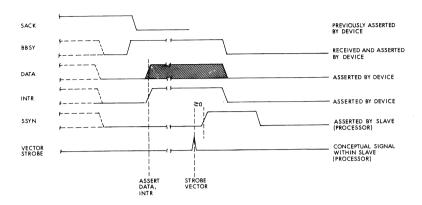

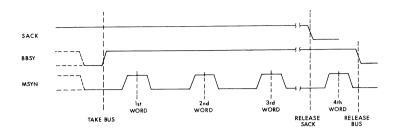

| APPENDIX D UNIBUS TIMING DIAGRAMS                                                                                                                                                                                                        |

| APPENDIX E LSI-11 BUS TECHNICAL SPECIFICATIONS E-1                                                                                                                                                                                       |

| APPENDIX F PROGRAMMING TECHNIQUES F-1                                                                                                                                                                                                    |

| GLOSSARYGLOSSARY                                                                                                                                                                                                                         |

| INDEX                                                                                                                                                                                                                                    |

DIGITAL's PDP-11 computer family was launched in 1970. Since that time, they have enjoyed unparalleled success—DIGITAL has sold more minicomputers and more 16-bit microcomputers than any other company. DIGITAL's leadership of the 16-bit marketplace is due to a number of factors:

- product range

- cost effectiveness

- compatibility

DIGITAL offers you a full range of products to meet your needs: from chipsets to boards to systems. With this broad product range, we can meet the needs of your application.

As technologies have improved, DIGITAL has offered more computing power in smaller and less expensive systems.

The key concept of the PDP-11 family is compatibility. The software, the operating systems, the I/O systems, and the peripherals are all largely compatible. The broadly-based compatibility of the PDP-11 family is a function of its common architecture.

The purpose of this book it to explain the architecture of DIGITAL's PDP-11 computers. This book is aimed at two distinct groups of readers: first, those who need to know the technical details of PDP-11 architecture; second, those who may be new to computers or inexperienced with PDP-11s and need a tutorial introduction to the PDP-11 family and its architecture.

Those readers in the more technical group may want to read about the evolution of the PDP-11 and LSI-11 computers, and the PDP-11 Milestones section of Chapter 1. Then, they should refer directly to the chapter(s) where they have specific questions. Those readers who frequently refer to Table 5-1—Instruction Set— will appreciate its black page tabs, which make it easy to find.

Readers who require tutorial information should read all of the first two chapters, using Chapter 2 as a reference guide. From the brief introductions in Chapter 2, the reader should be able to select those chapters and appendices of particular interest.

# CHAPTER 1 ARCHITECTURE AND THE PDP-11 FAMILY

### INTRODUCTION

### What is computer architecture?

Before we define computer architecture, let us review some basic computer terms. A program is a series of instructions that tell a computer how to operate on data. Most programmers today work in a high-level language such as BASIC, COBOL, or FORTRAN. Programs coded in these languages must be translated into instructions that the computer can understand. One high-level language statement is translated (or compiled) into many machine instructions. To have more control over the computer, and to gain a better appreciation of its operation, a programmer must use a language that is closer to the machine instructions used in the computer. Such a language is called an assembly language.

Each assembly language statement corresponds to one machine instruction (an elementary computer operation). The entire group of instructions that can be used in assembly language statements is called the **instruction set**.

Programs access individual data items, manipulate them, and move them into different areas of the computer. To provide fast, temporary storage and facilitate operations on these data, the assembly language programmer can use a number of locations called **registers**.

To find data or program instructions, the computer must remove information from its main storage area, called main memory. Each memory location has an address—a number used to find that information location. The methods used to arrive at this address are called **addressing techniques**.

A computer can find out about external events by its **interrupt structure**. This mechanism is also used for making an orderly transition between programs.

### Chapter 1 — Architecture and the PDP-11 Family

We have now introduced the main elements of computer architecture:

- Instruction sets

- Addressing techniques

- Registers

- Interrupt structures

These are the tools that the assembly language programmer manipulates to write programs. We can define computer architecture as the behavior of a computer seen by an assembly language program.

### The Importance of a Consistent Architecture

Why is computer architecture so important? When we hear about advances in the computer industry we usually hear about new technologies for building faster, smaller and less expensive computers. Technologies seem to overshadow computer architecture. But the most advanced computer technologies won't help a programmer if the computer's architecture—the programmer's tool kit—is awkward.

Let's make an analogy to music to illustrate the importance of a consistent architecture. There is a standard architecture for the modern piano. If you know how to play the piano, you can play any piano, because the architecture—the keyboard—is standard. Middle C is always in the same position; the number of keys, their placement, and their pitch are all specified and standard.

There is great latitude in the construction of pianos using this architecture, however. Different pianos may produce the same pitch when a key is struck, but the tone is a function of the construction. A spinet does not produce the same tone quality as a concert grand piano. This reflects the woods used in constructing the piano, as well as the size and shape of the sound board, and other factors. Also, the touch and action of pianos will vary with the quality of materials and construction.

What if a manufacturer decided to build an inexpensive electronic piano? To save production costs, he wants to use buttons instead of the traditional piano keys. Who will buy his new pianos? By changing the piano's architecture, he risks losing the market for the millions of people trained to play the piano.

Just as the manufacturers of pianos are committed to their architecture, so too is DIGITAL committed to its PDP-11 computer architecture.

Thousands of programmers trained on PDP-11s want to see its proven architecture maintained as computer technologies advance. Their programs will run, producing the same results on PDP-11 computers of different generations, whether built with transistors, or very large-scale integrated circuits, because the architecture has been maintained. When an architecture is maintained, existing programs will not require recoding; they will run on new machines that are smaller, faster, and cheaper. From a corporate viewpoint, this means major savings—a company can protect its investment in software while taking advantage of the latest computer technologies.

### THE PDP-11 FAMILY CONCEPT

The PDP-11 family of computers shares a common architecture. They are all based on a 16-bit word length, a common instruction set, and the same addressing techniques. They also share the same data management utilities, the same input/output (I/O) systems, and the same programming languages. If you have learned to program one computer in the PDP-11 family, you can easily program another member of the PDP-11 family. The software written for one member of the PDP-11 family will run on other family members. The peripherals and I/O systems for the PDP-11 family are also largely compatible. Because the PDP-11 family has been around since 1970, its hardware and software are proven, time-tested, and thoroughly debugged.

DIGITAL has shipped over 300,000 PDP-11 computers since 1970. The success of the PDP-11 family of computers is a function of their common architecture that provides compatibility across all models: from small, single-user, chip-based microcomputers to large minicomputers that support timesharing services. By providing its customers with a clear growth-path to expand their computer systems as their requirements expand, DIGITAL has built more minicomputers and more 16-bit microcomputers than any other manufacturer. Within the PDP-11 family of computers, you can upgrade or extend any DIGITAL system by adding memory, peripherals, or processors without worrying about major incompatibilities in your computing system. And your personnel who are already familiar with the PDP-11 environment will lose no time recoding or learning about another architecture.

### Compatibility

DIGITAL's PDP-11 architecture gives you compatibility. It is your assurance that no matter what system you choose or how you decide to mix and match software, peripherals, or CPUs, you will be using proven products that were designed from the beginning to be part of a fam-

ily. Your application or your business can grow while continuing to use existing software. You can start with a small system and migrate upward to more powerful PDP-11s or eventually choose to build a system with one of DIGITAL's super-minicomputers in the VAX-11 series. Your PDP-11s will function superbly as front ends or as distributed processing nodes in a VAX-11 environment.

Because of this common architecture, you can match a PDP-11 system to your job. A solution can be tailored to your needs, today. As your workload grows, you can expand your computing capability since nearly all of the peripherals and software will work with any PDP-11 processor.

### **Peripherals**

Your selection of PDP-11 peripherals is impressive. DIGITAL manufactures a full range of peripheral equipment designed to meet specific needs as well as to maintain PDP-11 family compatibility. I/O and storage devices range from low-cost cassette-tape devices through high-capacity Winchester disks, and from intelligent, rugged DECwriters for hard copy, to human-engineered video display terminals. You can also choose from a variety of peripheral products developed and supported by third parties. Either way, there is a complete spectrum of peripheral devices available to complement the software, and provide the complete answer to customer needs in all market areas: business, education, industry, laboratory, and engineering.

The DIGITAL Peripherals Handbook and the Terminals and Printers Handbook describe in detail the optional equipment available for use with the PDP-11 family members.

### Networking

DIGITAL's networking capabilities, both hardware and software, are unsurpassed in the industry. You can have a mix of PDP-11 systems doing different jobs, communicating among themselves or with other DIGITAL systems or with equipment from other manufacturers.

### **Software and Operating Systems**

The large installed base of PDP-11 computers means that software for your application will be easy to find. You can choose from proven software developed and supported by DIGITAL or you can choose from software supported by third parties. An important source of software is DECUS—The Digital Equipment Computer Users Society. DECUS is one of the largest and most active user groups in the computer industry, with over 60,000 members world-wide. Membership is free to owners of DIGITAL computers. The DECUS program library contains over

1700 software packages written and submitted by members and DIGITAL employees, and available for the cost of media and copying only.

The PDP-11 family of processors supports a complete range of compatible operating-systems:

- realtime multitasking

- multiuser, interactive timesharing

- small and midrange commercial

- multiuser data management

- development and runtime for microcomputers

For more information about PDP-11 software and operating systems, see the PDP-11 Software Handbook. It includes a general description of each operating system, the file structures, and data handling facilities, the user interfaces, the system utilities, and the language processors supported.

Today's PDP-11s provide a full product range—from chips to systems to networks. The differences among the various PDP-11 processors are primarily internal communications (bus) structure, size, and processing power. PDP-11 processors support multiple operating systems so that the right hardware, operating system, and application software can be combined to meet your exact requirements. The same software that runs on our smaller, low-priced PDP-11 systems will run on our larger models.

### PDP-11 ARCHITECTURE AND SYSTEM PERFORMANCE

Both the technology and the architecture of a computer system are important to its performance. The architecture, and particularly the Instruction Set Processor (ISP) of the PDP-11 family of computers have been designed with performance in mind. The PDP-11 architecture makes it possible to perform more functions with fewer instructions. This means that comparing the instruction execution speeds of computers from different vendors may be misleading. Even though a processor may execute individual instructions more slowly, it may execute an application more quickly because its instructions are more powerful. More powerful instructions give PDP-11 computers a significant advantage.

Several factors affecting performance were incorporated into the PDP-11 architecture:

Bit efficiency

- Simple, yet powerful instruction set

- Addressing capability

A bit-efficient architecture allows the computer to execute an algorithm with fewer instructions bits. Bit efficiency is a function of the number of bits in the instruction word and the number of operations performed for each instruction. A computer with a large instruction word may be more bit efficient than a computer with a small instruction word if the computer can do an equal number of operations with far fewer instructions.

The benefits of bit efficiency are small program size and high execution speed. Programs can be smaller because fewer bits are needed to perform a given operation. Compact programs are more likely to fit into high-speed, on-board memory. Also, fewer memory references are required to fetch program instructions.

The PDP-11 instruction set is powerful, yet simple to use and learn. It lets the programmer address different data types the same way. To save memory space and simplify control and communications, PDP-11 instructions allow byte and word addressing. Another mechanism for saving memory space and program code is the ability of single instructions (with double operands) to perform several operations. A full set of conditional branch instructions foster structured programming by helping avoid the use of jump instructions.

The PDP-11 architecture has an elegant addressing capability that is flexible and simple. It uses the same instruction to address a processor register, main memory, or an I/O device. No distinction is made between data and address locations, even in the processor registers. This can be helpful when manipulating arrays, for example. In a system with dedicated data and address registers, an array subscript must often be created in data registers before it can be copied to address registers to access the operand. This transfer from data to address requires additional program code which can reduce system performance. DIGITAL's PDP-11 addressing modes avoid this problem.

### **EVOLUTION OF THE PDP-11**

For the past 25 years, DIGITAL has refined the PDP-11 computer family. We have reduced the size and cost of new family members that provide the performance and functions usually found only in much more expensive computers. The PDP-11 family grew out of experience with the PDP-8—DIGITAL's first mass-produced minicomputer. The PDP-8—a 12-bit, single-address computer—was originally designed for process-control and laboratory applications. It was also used for mes-

sage switching and other realtime applications. The PDP-8 pioneered the idea of using a minicomputer for small, general-purpose time-sharing.

The first PDP-8 system was shipped in April 1965. Within 15 years, over 50,000 PDP-8 family computers were produced, and the design was improved ten times to use the latest technologies.

Out of the PDP-8 experience, DIGITAL engineers planned the next generation of minicomputers—the PDP-11 family—around these features:

- growth path within the family

- ease of programming

- faster interrupt handling

- more registers

- byte and string handling

- more physical memory

- flexible addressing modes

- support for applications based in read-only memory (ROM)

- better I/O processing

**Growth Path**—The PDP-11 family succeeded in this area beyond the goals of the original design group. Counting the VAX/VMS with PDP-11 compatibility mode, there are now twenty members of the PDP-11 family. The PDP-11 family offers a range of performance and memory—with compatibility—unprecedented in the industry.

**Ease of Programming**—The compatibility of PDP-11 family processors makes it very easy to switch from one processor to another.

Faster Interrupt Handling—This problem was solved by the UNIBUS interrupt vector design. This fast mechanism requires only four memory cycles from the time an interrupt request is issued until the first instruction of the interrupt routine begins execution. This fast context switching gives 16-bit PDP-11 computers better realtime performance than some 32-bit computers.

**More Registers**—Other minicomputers had skimped on registers; the PDP-11 architecture called for eight 16-bit registers. Later, six 64-bit registers were added as accumulators for floating-point arithmetic.

Byte and String Handling—The PDP-11 architecture provided for direct byte addressing from the beginning. In 1977, string handling was added with the Commercial Instruction Set (CIS).

More Physical Memory—As the PDP-11 family outgrew the original 16-bit address space, memory management was added, allowing 22-bit addressing (up to four Mbytes).

Flexible Addressing Modes—The PDP-11 architecture uses the autoincrement/autodecrement addressing mechanism in lieu of a hardware stack. This successful PDP-11 solution has been widely copied in the industry.

**Provision for ROM**—PDP-11s make extensive use of read-only memories for bootstrap loaders, program debuggers, and simple functions. Most code written for PDP-11s is reentrant without special effort by the programmer.

**Better I/O Processing**—The PDP-11's improved interrupt structure greatly enhances its I/O capabilities. The LSI-11 Bus includes block mode data transfer to reduce CPU overhead during I/O. All PDP-11 family computers provide Direct Memory Access (DMA) for high-priority communications with memory.

The design goals of the PDP-11 engineers were not all realized with their first production model. The PDP-11 architecture provided a solid foundation for family growth. As you can see from the list that follows, the PDP-11 architecture was extended by new instruction sets for floating point and commercial applications. PDP-11 processors were reengineered to have better performance, smaller packaging, and more attractive prices.

### **PDP-11 MILESTONES**

### 1970

- UNIBUS

- Byte (8-bit) or word (16-bit) addressing

- Consistent addressing

- Interrupt capabilities

- Extended Arithmetic Element (EAE)--hardware multiply and divide

- Eight General Purpose Registers (GPRs)

### 1972

- Floating-point processor

- 6 registers

- 46 instructions

- Fastbus (PDP-11/45)

### Chapter 1 — Architecture and the PDP-11 Family

- Memory Management (KT11C)

- Fully protected multiprogramming with three access modes:

- Kernel

- Supervisor

- User

- Second set of GPRs for a total of 16 (PDP-11/45)

- Programmed interrupt request

### 1973

- Extended Instruction Set (EIS) for multiply and divide

- Floating Instruction Set (FIS)

### 1975

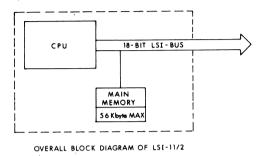

- LSI-11 "computer-on-a-board"--first 16-bit microcomputer

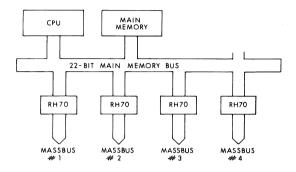

- 22-bit addressing for processor, peripherals (PDP-11/70)

- 32-bit wide DMA bus (PDP-11/70)

### 1976

• Fast, all bipolar memory (PDP-11/55)

### 1977

- LSI-11/2 offers LSI-11 performance in half the space (a double-height board 5.2 x 8.5 inches or 13 x 22 cm)

- Commercial Instruction Set (CIS):

- Character sets and strings

- Packed and zoned decimal strings

- Variable length strings

- Writable Control Store (WCS) extends function code to invoke userwritten microcode (PDP-11/60)

- Remote diagnosis (PDP-11/70)

### 1978

Virtual Address eXtensions (VAX)—a 32-bit super-minicomputer including PDP-11 compatibility mode

### Chapter 1 — Architecture and the PDP-11 Family

### 1979

LSI-11/23 offers 2.5 times the operating speed of the LSI-11/2 in the same board area

### 1980

- PDP-11/44 offers new levels of performance in its price range:

- Winchester disk support

- Up to four Mbytes of main memory

### 1981

- FALCON SBC-11/21--designed for dedicated, ROM-based, real-time applications--is the smallest 16-bit single-board microcomputer in the industry

- LSI-11/23 offers memory management--22-bit addressing of up to four Mbytes of main memory--and RSX-11M support for realtime applications

- PDP-11/23 PLUS supports up to one Mbyte of parity MOS memory

- Supports RSX-11M-PLUS

- CIS option for COBOL-81

- PDP-11/24--the newest and smallest UNIBUS processor

- Supports up to four Mbytes memory

- Winchester disk support

### 1982

- Professional 300 series personal computers

- Based on PDP-11 architecture

- Multitasking operating system

- Software development on PDP-11s or VAXs

- MICRO/T-11--DIGITAL's first 16-bit microprocessor on a single 40pin chip

- PDP-11 instruction set

- MICRO/J-11 offers the performance of the 11/70 in a 60-pin package

- On-chip memory management addresses up to 4 Mbytes

- 46 floating-point instructions standard

- MICRO/PDP-11--for customers who need a low-cost, Winchester-based, PDP-11 system

- 10 Mbyte Winchester system disk

- All PDP-11 software available

### **EVOLUTION OF THE LSI-11**

### Introduction

In recent years, minicomputers have been adapted to a wide variety of applications. They have displaced larger computer systems in many traditional markets. At the same time, they have opened up many new markets, primarily because of their low cost, small size, and ease of use. Still, in spite of this remarkable success, minicomputers are not without competition.

In cost-sensitive areas, the minicomputer is being eased out of its dominant position by a new generation of VLSI (Very-Large-Scale Integration) microcomputers. These new "processors on a chip" have found a warm reception from designers seeking inexpensive computing power. That warm reception sometimes cools, however, when the user finds himself with a collection of components, instead of a complete computing system. The discovery that he is largely on his own when it comes to software and debugging support has a similarly chilling effect. The entry into the world of programming PROMs, using FORTRAN cross-assemblers and simulators, and writing even simple software routines from scratch can be a traumatic experience indeed. Still, the advantages of LSI microcomputers are very real, and many users have found the difficulties worthwhile. However, some users wonder why they cannot have the best of both worlds: the low cost and small size of the microcomputer, and the ease of software development and performance of the minicomputer systems with which they are familiar.

Therefore, the appearance of new LSI microcomputer systems that are fully compatible with a line of 16-bit minicomputers was a significant event. The first of these new microcomputers was the DIGITAL LSI-11, a complete 4K PDP-11 on a 21.6 X 26.7 cm (8.5 X 10.5 inch) board. Priced to compete with other LSI microcomputers, it offered true minicomputer performance with the highest levels of support. While not intended to be yet another low-end minicomputer, the LSI-11 brought many minicomputer strengths to its new microcomputer applications.

To provide minicomputer performance at a microcomputer price, the LSI-11 was designed to optimize system costs, rather than component costs. A one-chip central processor, then, was not necessarily superi-

or to a four-chip one--the choice was made on the basis of total system cost and performance. On this basis, a microprogrammed processor was selected, permitting the inclusion of features like a "zero cost" realtime clock and automatic dynamic memory refresh. The built-in ASCII programmer's console was also made feasible by the microprogramming feature.

Awareness of system costs and performance were the primary motivations in designing the LSI-11. System issues included:

- Cost of ownership

- Ease of interconnection

- Preservation of customer's training and software investment

- Availability of proven peripherals and software

All these issues dictated PDP-11 compatibility. The LSI-11 microcomputers use the PDP-11 architecture, including the PDP-11 instruction set and addressing modes. They use a bus structure based on the PDP-11 UNIBUS, but smaller and less expensive—the LSI-11 Bus.

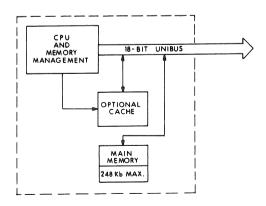

DIGITAL's next advance in LSI technology was the LSI-11/2, which offered the performance of the LSI-11 in one half the board size. The LSI-11/23 maintained the LSI-11/2's board size but more than doubled its operating speed. Next came the FALCON Single Board Computer (SBC-11/21), which was the industry's smallest 16-bit computer on a board.

### Recent Trends in PDP-11/LSI-11 Development

The most recent announcements in the LSI-11/PDP-11 family have focused in three areas: personal computers, chipsets, and microcomputer systems. DIGITAL's range of personal computers extends from the-powerful, PDP-11 based Professional 300 series to word processing and accounting with the DECmate II and to systems running industry-standard software with the Rainbow 100. (DECmate II and Rainbow 100 are not PDP-11 – based products.)

DIGITAL's 16-bit chipset offerings provide levels of price and performance to meet any application. From the low-cost MICRO/T-11 micro-processor in a 40-pin chip, to the ultimate in 16-bit, single-package microprocessor performance--the MICRO/J-11.

DIGITAL is also presenting a family of systems between the personal computers and the LSI-11/PDP-11 computers--the MICRO/PDP-11. An aggressively-priced member of our proven PDP-11 family, the multi-

user MICRO/PDP-11 features compact microcomputer packaging for the office environment. The single-user MICRO/PDP-11 is optimized for the technical environment.

### **Future Directions**

The evolution of PDP-11 systems offers a striking demonstration of the impact of technology and architecture on a computer family. While maintaining a consistent architecture, PDP-11 computers have incorporated increasingly sophisticated technology to provide better performance at lower cost. DIGITAL is continuing to develop its 16-bit products. We will continue to lead this market by lowering the cost and extending the range of PDP-11 computing. Simplicity and reliability of design will continue to lower our cost of ownership.

### THE PDP-11 FAMILY ALBUM

DIGITAL is the only major vendor to sell products with compatible hardware and software at the chip, board, box, and system levels. The latest generation of PDP-11 family members are described in this section. Products are divided into these categories:

- Microprocessor chipsets

- Microcomputer boards

- Personal computers

- Microcomputer systems

- Minicomputer (UNIBUS) systems

### Chipsets

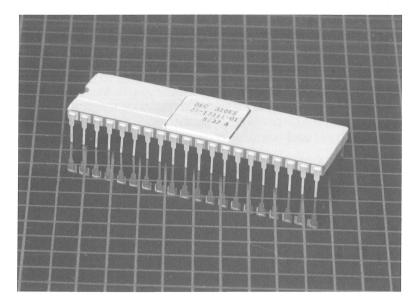

The MICRO/T-11 is DIGITAL's first single-chip microprocessor. This chip complements DIGITAL's board, box, and system products by offering customers any level of integration. The MICRO/T-11 is a 16-bit microprocessor in a 40-pin chip. Through the use of a programmable mode register, MICRO/T-11 can be adapted to a wide variety of applications. By selecting either static or dynamic memory and either 8-bit or 16-bit mode, the designer determines the functions of mode-dependent pins. OEMs will find DIGITAL's MICRO/T-11 chip products to be a solution that meets size requirements while utilizing the PDP-11 base-level instruction set and powerful interrupts. The ability to migrate from PDP-11 products down to the chip level is an advantage for designers familiar with the PDP-11 instruction set and development tools. Key features include:

- 16-bit microprocessor in a single 40-pin chip

- Selectable 8-bit or 16-bit data bus

- Dynamic RAM refresh capability

- PDP-11 instruction set and addressing modes

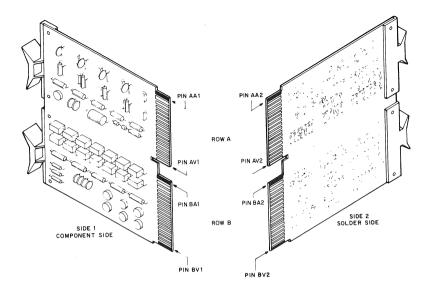

Figure 1-1 The MICRO/T-11 Chip

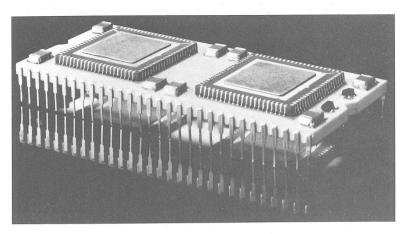

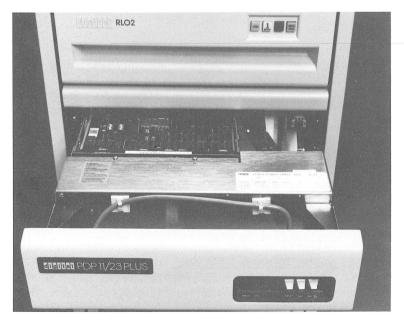

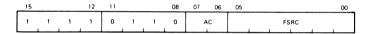

The MICRO/J-11 offers the performance and architecture of the PDP-11/70 in a single 60-pin package. Based on CMOS technology, the MICRO/J-11 has 16-bit I/O, a 32-bit internal data path, and can address up to 4 Mbytes of memory with on-chip memory management. The MICRO/J-11 implements the full PDP-11 instruction set including hardware multiply/divide (EIS), FP11 floating-point (46 instructions), and MICRO Online Debugging Task (ODT). Key features include:

- 16-bit I/O

- 32-bit internal data path

- On-chip memory management to address up to 4 Mbytes memory

- Full PDP-11 instruction set

- 46 floating-point instructions standard

- Extended instruction set standard

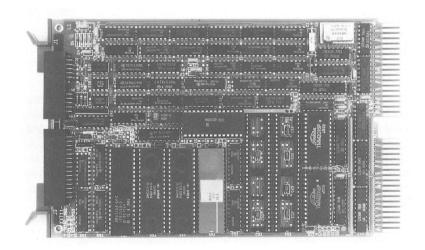

Figure 1-2 The MICRO/J-11 Chipset

### Boards

The **LSI-11/23** offers 2.5 times the operating speed of the LSI-11/2 in the same board area. The LSI-11/23 approaches the performance of mid-range minicomputers in a single board. Its 22-bit addressing capability lets the LSI-11/23 address four Mbytes of main memory. Its comprehensive memory management feature provides memory relocation, segmentation, and protection for this extended address range. Key features include:

- Extended LSI-11 Bus for 22-bit addressing

- RSX-11M-PLUS support for realtime applications

- Full memory management

The FALCON SBC-11/21--the smallest 16-bit single-board microcomputer in the industry--was designed for dedicated, ROM-based, real-time applications. The FALCON offers more on-board RAM and ROM memory than any other DIGITAL microcomputer. It features two asynchronous serial I/O ports with eight programmable baud rates, 24 parallel I/O lines, and a crystal-controlled realtime clock. The FALCON packs all this computing power onto a 44 square inch board. Key features are:

- Most on-board RAM and ROM of any DEC microcomputer

- Two asynchronous serial I/O ports (selectable baud rates)

- 24 parallel I/O lines

- Crystal-controlled realtime clock

Chapter 1 — Architecture and the PDP-11 Family

Figure 1-3 The LSI-11/23 Board

Figure 1-4 The FALCON SBC-11/21 Single Board Computer

### Personal computers

Recently, DIGITAL introduced a complete range of personal computers:

- Professional 300 series with multitasking operating system and software development on PDP-11s or VAXs

- DECmate II for word processing and general accounting

- Rainbow 100 for CP/M™ applications

CP/M is a trademark of Digital Research, Inc.

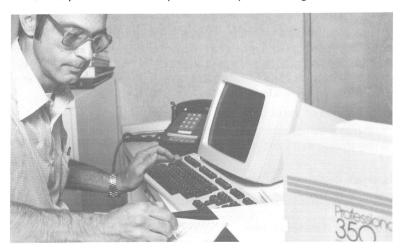

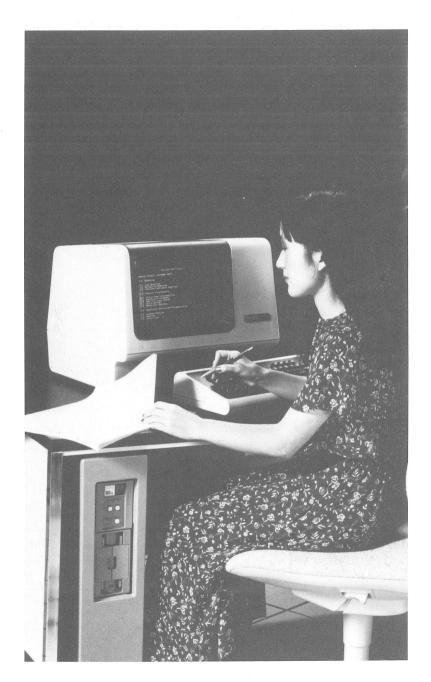

The **Professional 300** series are full-fledged members of the PDP-11 family. The microprocessor chip used in the Professional 325 and 350 is the F-11, the same chip used in the LSI-11/23 and the PDP-11/23 PLUS. This gives the user true minicomputer performance in a desktop personal computer. As a PDP-11 family member, the Professional 300 personal computers incorporate the RSX-11M-PLUS operating system into their operating system. The Professional 300 personal computers can transfer files to any DIGITAL computers running RSX-11M, RSX-11M-PLUS, or VAX/VMS (using optional communications software). Also, applications for the Professional may be developed on a PDP-11 or VAX host system for debugging on the Professional 350. The Professional computers are very easy to use, thanks to their menus, help service, file and disk services, and editor. The optional Telephone Management System for the Professional 350 allows automatic personal and computer-to-computer dialing.

Figure 1-5 The Professional 350 Personal Computer

### Microcomputer systems

The MICRO/PDP-11 is a system for technical and commercial customers who need more performance than a personal computer, but lower cost than an LSI-11 or PDP-11 system. Unlike typical desktop microcomputer systems, the MICRO/PDP-11 provides ample performance to handle small business, departmental, or technical applications. It shares much of the hardware and software found in DIGITAL's larger minicomputer systems. A full-fledged PDP-11 processor, the MICRO/PDP-11 is based on the PDP-11/23 PLUS processor. It includes a 10 MByte, 51/4 inch (13.1 cm) Winchester disk and 800 Kbyte, dual 51/4 inch dual diskette subsystem for backup and media interchange.

Users can choose from a wide range of PDP-11 operating systems to match their needs-RSTS/E, RSX-11M-PLUS, CTS-300, RT-11, Micro-Power/Pascal, UNIX™, and DSM-11.

UNIX is a trademark of Bell Laboratories.

The powerful PDP-11/23 PLUS CPU supports full 22-bit, 4 Mbyte addressing, which means that large applications will run on the MICRO/PDP-11. For extra computing power in specialized applications, two optional microcoded chips are available: one for floating-point data, and one for the Commercial Instruction Set (CIS). For even faster floating-point performance, a separate floating-point processor is available.

Attractive packaging in three configurations—table top, floor stand, and rack mount—allow wide flexibility of installation. Its modular construction permits easy assembly and disassembly with simple tools.

Unlike most microcomputer systems in its price range, the MICRO/PDP-11's communication capabilities are extensive and can easily be enhanced to match the growth of a business. The MICRO/PDP-11 can be fully integrated into a distributed processing environment utilizing DECnet hardware and software.

Key features of the MICRO/PDP-11 include:

- 10 Mbyte Winchester system disk

- 800 Kbytes in dual floppy diskettes

- All PDP-11 software available

- PDP-11/23 PLUS CPU quad module with:

- full memory management

- line frequency clock

- two serial lines

- user-friendly boot/diagnostics

- Floating-point and CIS options

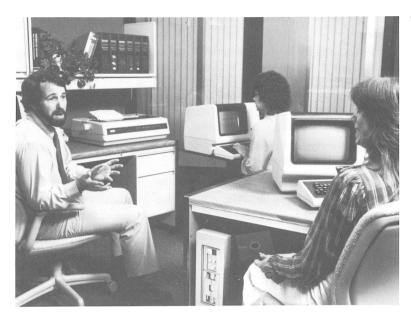

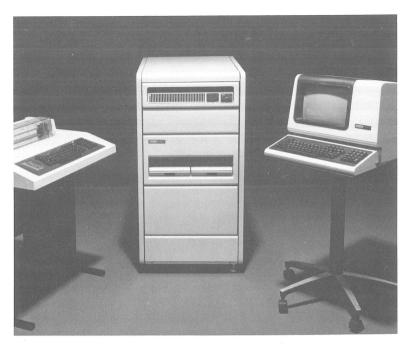

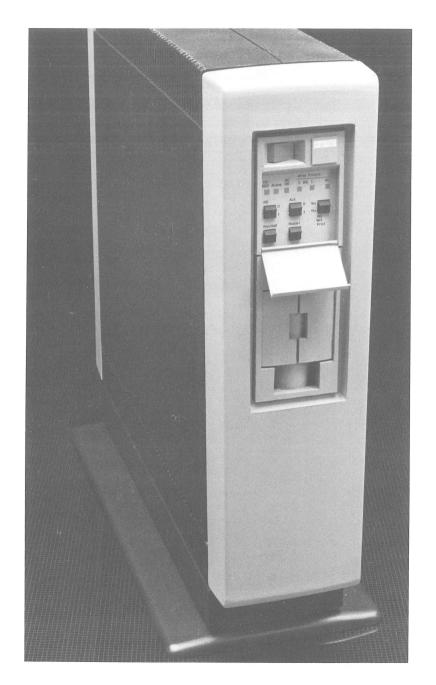

Figure 1-6 The MICRO/PDP-11 System

The PDP-11/23 PLUS gives minicomputer performance at a microcomputer price. Its 22-bit addressing supports up to one Mbyte of parity MOS memory (although it can address four Mbytes). A Commercial Instruction Set option, designed to work with COBOL 81, is standard on commercial systems. A microcoded floating-point option increases computational speed, and if your application demands more, a hardware floating-point option provides even greater performance. The system distribution panel makes installation or relocation easy. The PDP-11/23 PLUS is available with a wide assortment of peripherals, interconnect options, video and hardcopy terminals, and a broad choice of system software to fit your applications.

The compatibility of DIGITAL software from the most powerful PDP-11 system downward to the least expensive means that PDP-11/23 PLUS users can run the RSX-11M-PLUS, RSX-11M, and RSTS/E operating systems used on the most powerful PDP-11s, as well as RT-11. And users can work with the same command language, the same query and report writer, and the same forms manager used on larger PDP-11s.

DECnet Phase III features—adaptive routings, multidrop terminal sup-

port, and network command terminals—are available on the PDP-11/23 PLUS

These features make the PDP-11/23 PLUS an ideal candidate for distributed processing applications in which it can serve as a departmental computer running four to six local terminals. The PDP-11/23 PLUS can communicate with a corporate, divisional, or plant host system through DECnet or through DIGITAL's Internet software that links it with non-DIGITAL computer systems.

Although DIGITAL will install it for you, you can save money by installing the PDP-11/23 PLUS yourself.

Key features of the PDP-11/23 PLUS include:

- Extended LSI-11 Bus for 22-bit addressing

- RSX-11M-PLUS support for real-time applications

- Full memory management

- CIS option for COBOL-81

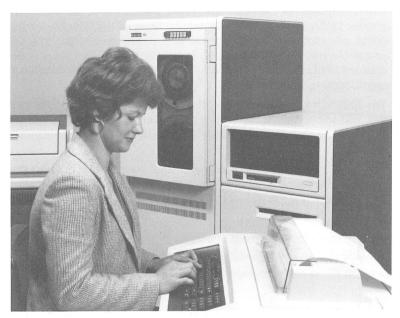

Figure 1-7 The PDP-11/23 PLUS System

### Minicomputer (UNIBUS) systems

The PDP-11/24—the newest and smallest UNIBUS processor offers midrange capacity at a small-system price. The PDP-11/24 uses LSI technology to provide better performance and memory management capabilities previously available only on larger PDP-11 systems. The 22-bit addressing allows users to address up to 4 Mbytes of main memory permitting more resident tasks, more users, and faster response.

Designed for compactness and reliability, the entire CPU fits on a single board. And the PDP-11/24 is the smallest system that supports UDA50/RA80 Winchester disk technology.

With Winchester technology, very reliable, high-density, nonremovable RA80 disks provide 121-Mbyte storage capacity. The UDA50 UNIBUS disk controller optimizes disk requests so that the hardware automatically schedules requests to multiple RA80s, and handles complete error recovery and buffering between the device and the system.

In addition to its impressive disk throughput performance, the RA80's average seek time is exceptional for a product in its price and capacity range.

A microcoded floating-point option for the PDP-11/24 increases computational speed, and if your application demands more, a hardware floating-point option provides even greater performance. A Commercial Instruction Set option, designed to speed the compilation and execution of COBOL 81, is standard on commercial systems. Key features of the PDP-11/24 include:

- Supports up to four Mbytes memory

- Single-board CPU

- Winchester disk support

- CIS and floating-point options

The **PDP-11/44** offers new levels of performance in its price range. Its outstanding features include a high-speed CPU that can access up to four Mbytes of main memory. A large, eight-Kbyte cache memory with a 275-nanosecond cycle time accelerates program execution and increases system throughput. In addition, the cache helps isolate main memory from CPU fetches, making more I/O bandwidth available to direct memory access (DMA) devices.

The PDP-11/44 meets rigorous reliability and maintainability standards. Its Error Checking Code (ECC) memory detects and corrects errors. A built-in microprocessor controls the ASCII console, provides extensive system diagnostics, and can control a dual TU58 cartridge

Figure 1-8 The PDP-11/24 System

tape subsystem for loading diagnostic programs should the standard load medium be unavailable. System cabling and mounting are designed for easy access. Remote diagnosis allows problems to be pinpointed quickly, and the correct replacement parts to be dispatched.

Because disk performance can play a key role in a computer's overall performance, particularly in those applications when I/O is large in relation to the amount of computation, the PDP-11/44 supports the new DIGITAL Storage Architecture (DSA). The DSA describes new disks, an intelligent controller, connections, and software protocols for attaching to DIGITAL systems. The disk subsystems of the DSA feature:

- Low cost of ownership per megabyte

- More data storage per square foot of floor space

- Choice of Winchester or removable disks

- Optimized I/O throughput

- Industry's most comprehensive data integrity features

- High availability

Figure 1-9 The PDP-11/44 System

The high performance of the DSA disk products is due both to the technology of the disks themselves and to their intelligent controller, the UDA50. It interfaces DSA disk subsystems to the UNIBUS, and supports up to four disk drives, connected radially. The UDA50 contains a high-speed, 16-bit processor that can handle data rates up to 3 Mbytes per second. The UDA50 permits high-density recording by providing powerful error correcting. It unburdens the host system of the overhead associated with error handling and I/O throughput optimization. Its seek ordering algorithm minimizes seek distances, reduces seek latency, and provides substantial throughput improvement over first-in-first-out (FIFO) servicing. The UDA50 permits overlapped seeks, initiating simultaneous seek operations to all disks with I/O requests to reduce effective seek time in multi-drive subsystems. It allows one disk to transfer data concurrently with ongoing operations on other disks.

The DSA disk drives that are supported by the UDA50 include:

- RA80-121 Mbyte fixed media

- RA60—205 Mbyte removable media

- RA81—456 Mbyte fixed media

### Chapter 1 — Architecture and the PDP-11 Family

The fixed-media of the RA80 and RA81 disk drives incorporate Winchester technology. The high density surfaces of the Winchester disk drives are accessed by twin heads which improve access time and permit the transfer of more data per seek operation. The sealed head disk assembly results in a virtually contaminant-free environment with significantly greater reliability.

The PDP-11/44 systems support the optional Commercial Instruction Set, and an optional floating-point processor. A 64-Kbyte chip memory is included on larger configurations, and is optionally available on others.

PDP-11/44 systems are available with a full complement of mass storage and interconnect options, and a wide choice of system software.

Key features of the PDP-11/44 include:

- Winchester disk support

- Up to four Mbytes of main memory

- Reliability and maintainability features

- Eight-Kbyte cache memory with 275-nanosecond cycle time

## CHAPTER 2

# **KEY ELEMENTS OF PDP-11 ARCHITECTURE**

#### INTRODUCTION

This chapter is a brief introduction to the main elements of PDP-11 architecture. As we introduce each topic in this chapter, we will refer you to a specific chapter for details. Key elements of PDP-11 architecture include:

- Data representation

- · Addressing and registers

- The PDP-11 instruction sets

- Traps and interrupts

- Mapping of memory and busses

- PDP-11 bus structures

## **DATA REPRESENTATION**

The PDP-11 architecture accommodates a variety of data types, which may be separated into categories according to the groups of instructions that manipulate them. They are:

- Integer data

- Floating point data

- String data

Integer data types are manipulated by the basic PDP-11 instruction set. The string data types are manipulated by the Commercial Instruction Set, which is offered as an option on some PDP-11 processors. Floating-point data types are manipulated by the Floating-Point Instruction Set (FP-11) which runs on a Floating-Point Processor (FPP). An FPP may be either a separate processor or a microcode option.

Data representation is treated in detail in Chapter 3.

**Integer data types** include 8-bit bytes and 16-bit words. Integer data types are stored in memory in binary form, which is represented entirely in ones and zeroes. (Computers use binary representation because it is simple: a one can be represented by the presence of a charge or a switch set on, while a zero can be the absence of charge or a switch set off. Thus, a large number could be represented by a series of switches set on or off to represent binary digits.) In an integer data word or byte, the leftmost, or most significant bit (MSB) can be used as a sign bit. The MSB is always zero for positive values and one for negative values.

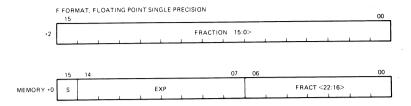

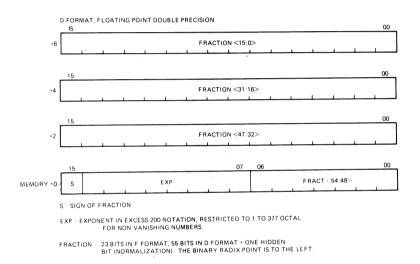

Floating point data types are the computer's way of handling very large or small numbers. They represent approximations to quantities using a scientific notation consisting of a sign, the exponent of a power of two, and a fraction between .5 (inclusive) and 1.0 (exclusive). The FP11 instruction set provides two types of floating point data, one 32-bits long and the other 64-bits long. The 32-bit data are called single-precision floating, or just floating; the 64-bit data are called double-precision floating or just double.

The instructions that manipulate floating point data are explained in Chapter 6.

String data types may be divided into two categories:

- Character string data

- Decimal string data

Character string data have their own data type in the Commercial Instruction Set (hereafter called CIS). A character string consists of a contiguous sequence of bytes in memory specified by beginning address and length. This data type is useful when representing names, data records, or text. The manipulations done on character strings include copying, searching, concatenating, and translating. A character string that contains ASCII codes for decimal digits is called a numeric string.

The CIS is treated in detail in Chapter 7.

**Decimal string data** have two data types: numeric strings and packed strings. Both have similar arithmetic and operational properties; they differ primarily in their representation of signs and the placement of digits in memory. Decimal strings are used to represent numbers in decimal form (which may not be used for computation), as opposed to binary integer form.

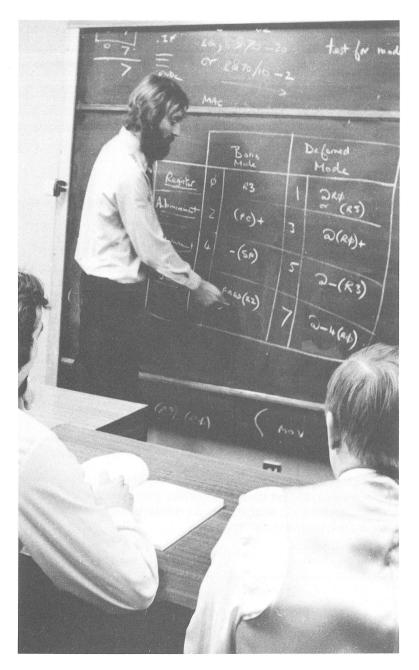

#### ADDRESSING AND REGISTERS

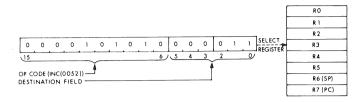

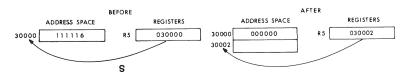

Within the processor there are locations called **general purpose registers** (GPRs) that can be used for temporary data storage, addressing, and as accumulators during computations. Eight 16-bit general purpose registers are available for use with the PDP-11 instruction set, but some of these registers have special uses. For example, one register is designated the Program Counter (PC); another is the Stack Pointer (SP).

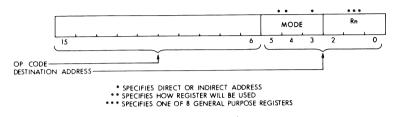

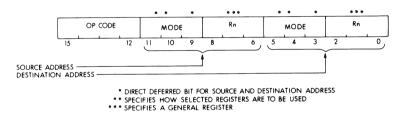

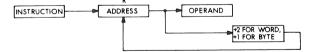

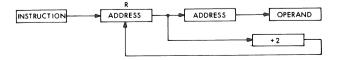

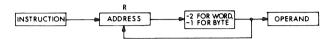

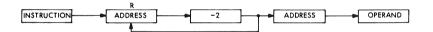

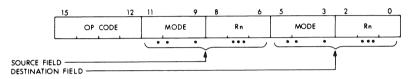

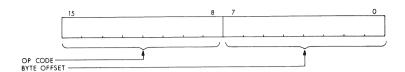

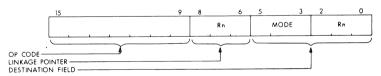

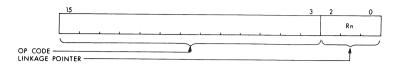

Any operation performed by the computer can be specified by an instruction. Each instruction specifies:

- Function to be performed (operation code)

- General purpose register to be used in locating the data (operand)

Addressing mode to specify how the registers are used

The datum being manipulated by an instruction is called the instruction operand. An instruction operand can be located in main memory, in a general register, or in the instruction itself. The method for specifying an operand's location is called the operand addressing mode. These addressing modes use the registers in a variety of ways to locate the operand or its address. Addressing and registers are explained further in Chapter 4.

# **INSTRUCTION SETS**

There are three instruction sets available on PDP-11 processors:

- PDP-11

- Floating-point

- Commercial

The PDP-11 instruction set is standard on all PDP-11 family processors; the Commercial Instruction Set and the Floating-Point Instruction Set are optional on certain processors.

## PDP-11 Instruction Set

The PDP-11 instruction set offers a wide selection of operations and addressing modes. There are seven categories of PDP-11 instructions:

- Single-operand

- Double-operand

- Branch

- Jump and Subroutine

- Trap

- Miscellaneous

- Condition code

To save memory space and simplify control and communications, PDP-11 instructions allow byte and word addressing in both single-operand and double-operand formats. Double-operand instructions let you perform several operations with a single instruction. Branch, jump, and subroutine instructions each provide a means for diverting program flow to a specified location. Trap instructions specify another form of change in program flow, but to a predetermined location. Condition code instructions set or clear the condition codes (four bits in the Processor Status Word [PSW] indicating the results of previous instructions).

See Chapter 5 for more information on the PDP-11 instruction set.

## Floating-Point Instruction Set

Floating point data types are manipulated by the Floating-Point Instruction Set (FP-11), which runs on an optional floating-point processor, which may be either a separate processor or microcode. (A microcoded floating point processor is standard on the J-11 chipset.)

The Floating-Point Instruction Set is described in Chapter 6.

#### Commercial Instruction Set

COBOL processing makes extensive use of string data types, which are manipulated by the Commercial Instruction Set (CIS). The CIS is offered as an option on some PDP-11 processors.

The CIS is discussed in Chapter 7.

#### TRAPS AND INTERRUPTS

## **Processor Traps**

PDP-11 processor traps are triggered by power failures and certain hardware and software errors. Processor traps protect the programmer and the processor. They save the current PC and Processor Status Word (PSW) and pass control to a trap-handling routine. This saves the programmer work. They also protect the processor and the operating system, if the programmer inadvertantly codes an illegal instruction, or an instruction which might violate the integrity of the operating system. A trap causes the processor to execute instructions pointed to by a certain permanently assigned address. **Trap instructions** are used to make an orderly transition to the trap routine and save the context of the CPU.

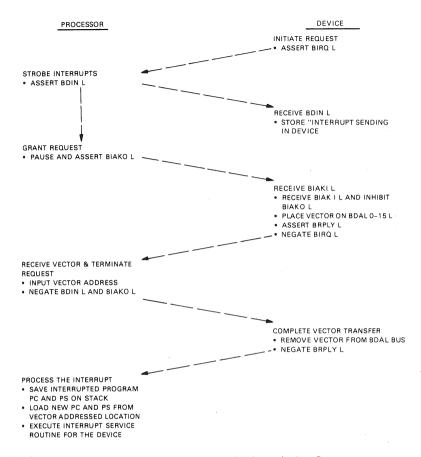

# Interrupts

Interrupts are used by certain system devices to reduce their wait for CPU service. PDP-11 processors offer the programmer fast interrupt handling. Only four memory cycles are required from the time an interrupt request is issued until the first instruction of the interrupt routine begins execution. By using interrupts, the processor is relieved of doing routine control functions for peripheral devices. Instead, the processor can ignore the peripheral, which may be reading a tape or doing some time-consuming operation, until the peripheral is finished and has data ready for the CPU. Then the device will use an interrupt to get the CPU's attention before it can execute the next instruction.

Traps and interrupts are examined in Chapter 8.

#### MAPPING TO MEMORY AND BUSSES

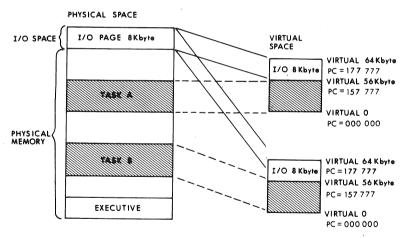

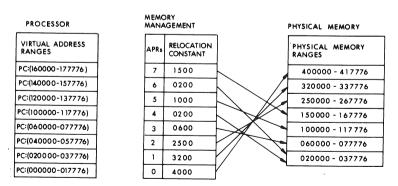

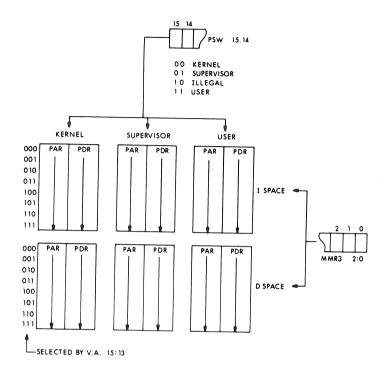

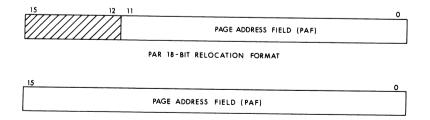

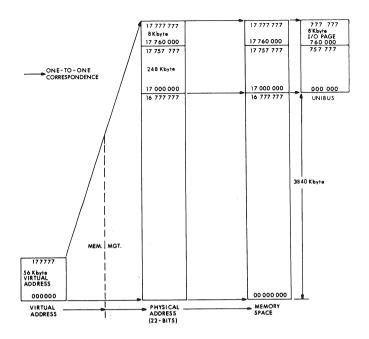

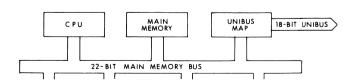

Memory management matches the virtual addresses generated by the

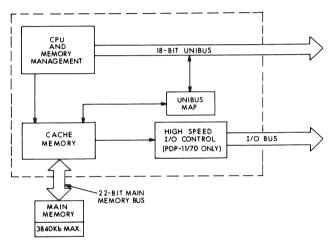

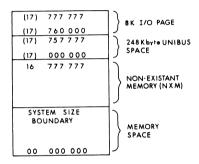

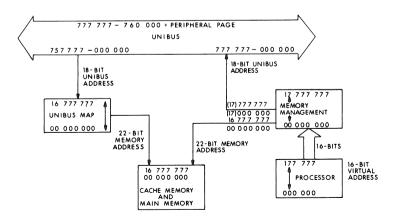

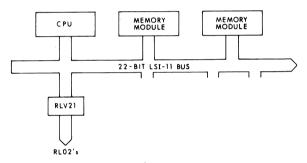

CPU with physical addresses in memory and with physical I/O bus addresses. It also protects operating system software and shared routines from modification and allocates protected memory space for each user. The UNIBUS map is a hardware device separate from the memory management unit. The UNIBUS map converts 18-bit UNIBUS addresses to 22-bit memory addresses. There is no map on the extended LSI-11 Bus. Processors and peripherals can generate and present 22-bit addresses directly to the extended LSI-11 Bus.

Memory management and bus mapping are described in Chapter 9.

## PDP-11 BUS STRUCTURES

The two PDP-11 physical I/O busses—the UNIBUS and the LSI-11 Bus—are both covered in Chapter 10. The brief, tutorial overview of the UNIBUS and LSI-11 Bus found in that chapter is augmented by appendices that contain timing diagrams and technical specifications.

## **UNIBUS**

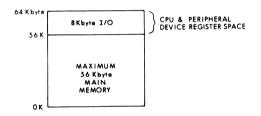

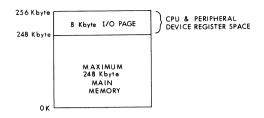

The UNIBUS, DIGITAL's unique data bus, was the first data bus in the history of the minicomputer industry to enable devices to send, receive, or exchange data without processor intervention or intermediate buffering in memory. The UNIBUS forms the hardware and software backbone of the PDP-11/24 and PDP-11/44 processors. Memory elements on the UNIBUS have ascending addresses starting at zero, while registers storing I/O data or the status of individual peripheral devices have addresses in the highest 8 Kbytes of addressing space. Peripheral devices may have one or more addresses.

#### LSI-11 Bus

The LSI-11 Bus is the low-end member of DIGITAL's bus family. Most DIGITAL microcomputers use the LSI-11 Bus or the extended LSI-11 Bus. The LSI-11 Bus operates very much like the UNIBUS, but to make it more cost-effective for microcomputer applications, it has fewer signal lines. Both the LSI-11 Bus and the UNIBUS are treated in Chapter 10.

# OTHER TOPICS (APPENDICES)

Other topics related to PDP-11 architecture are included in appendices. The topic of each appendix is listed and briefly discussed below.

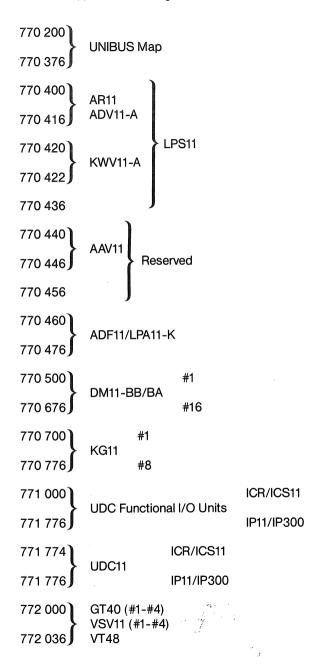

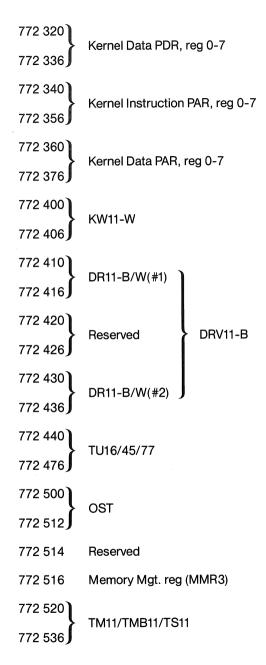

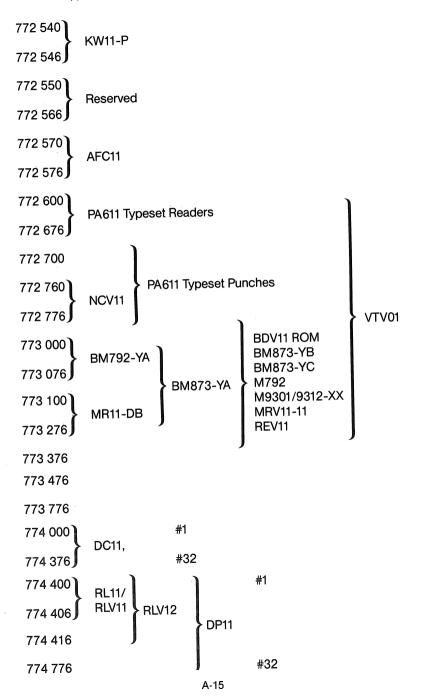

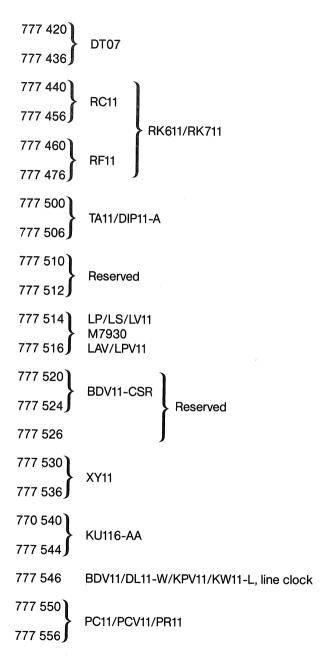

# Assignment of Bus Addresses and Vectors

Appendix A covers both the LSI-11 Bus and the UNIBUS. Topics covered include:

• I/O Page Device Addresses

- Interrupt and Trap Vectors

- Priority Ranking for Floating Vectors

- Floating CSR Address Devices

- Device Addresses

## PDP-11 Family Differences

Appendix B contains a family differences table that shows in detail the issues involved in software migration between PDP-11 family members. Any program developed using PDP-11 operating systems with higher level languages will migrate with very little difficulty. Certain assembly language applications may require slight modifications for a smooth migration.

## The Floating Instruction Set

The Floating Instruction Set (FIS) is a software option for the LSI-11/2 processor. The FIS consists of four special floating instructions that accelerate floating point calculations. The FIS is covered in Appendix C.

# **UNIBUS Timing Diagrams**

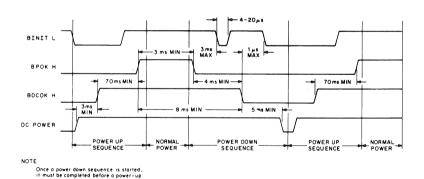

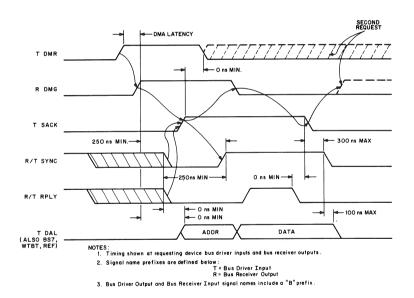

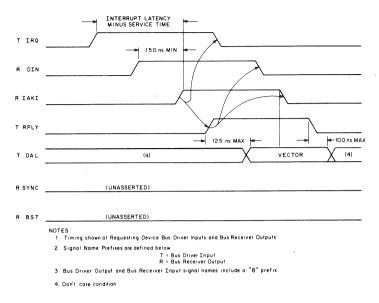

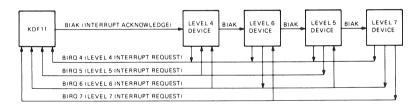

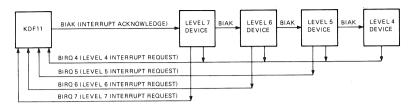

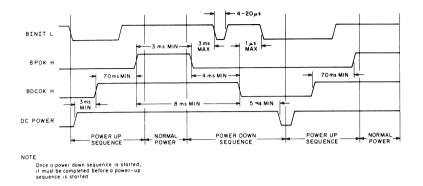

UNIBUS timing diagrams and other technical details are given in Appendix D.

# **LSI-11 Bus Technical Specifications**

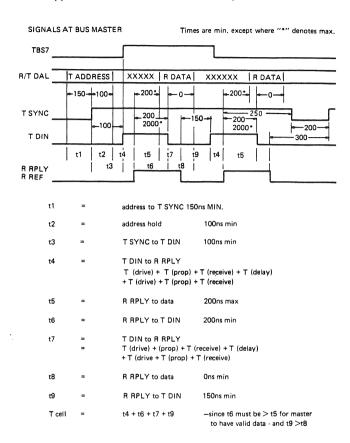

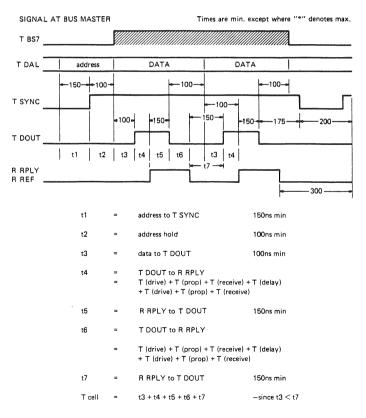

Topics covered in Appendix E include LSI-11 Bus timing diagrams, and bus pin-out descriptions.

# **Programming Techniques**

PDP-11 processors offer the programmer a combination of flexibility and power. The instruction set, addressing modes, and programming techniques play together to help you develop new software or use existing software. Programming techniques that pertain to architecture are included in this handbook. These include:

- Stacks

- Subroutine linkage

- Reentrancy

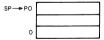

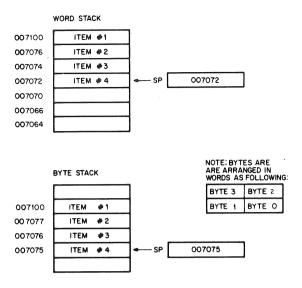

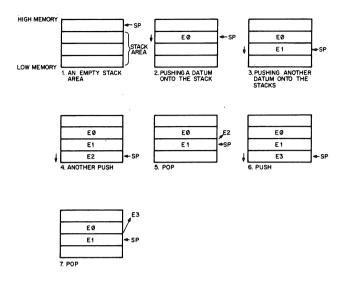

Stacks are a basic element of the PDP-11 architecture. They are areas of memory set aside by the programmer or the operating system for temporary storage and linkage. A stack is handled on a last-in/first-out (LIFO) basis: items are retrieved in the reverse of their storage order. A PDP-11 stack starts at the highest location reserved for it and expands downward to lower addresses as items are added.

Often, one of the general purpose registers must be used in a subroutine or interrupt service routine and then returned to its original value.

# Chapter 2 — Key Elements of PDP-11 Architecture

A stack can be used to store the contents of the registers involved. A stack is also useful to store the **linkage** information between a **subroutine** and its calling program. In many cases, operations performed by the subroutine can be applied directly to data located on or referenced by the stack without actually moving the data into the subroutine.

**Reentrancy** is the ability to share a single copy of a program among different users or different tasks. This makes more efficient use of memory. Reentrant routines differ from ordinary subroutines in that it is not necessary for reentrant routines to finish processing a given task before they can be used by another task.

PDP-11 programming techniques and examples are covered in Appendix F.

## Glossary

For definitions of terminology used in this book, refer to the Glossary. The Glossary is at the end of the book, between Appendix F and the Index.

# CHAPTER 3 DATA REPRESENTATION

Data representation is an important aspect of computer architecture. To deal efficiently with different kinds of information, a computer architecture must allow for a range of data types. The programmer's choice of data type should be a function of the application rather than the computer. However, some computers must use nonstandard addressing techniques with certain data types. These computers require more memory and will execute applications more slowly when using these "problem" data types. PDP-11 architecture avoids these compromises. You can use the data type that best suits your application without worrying about nonstandard addressing techniques.

Another feature of the PDP-11 family's data types is upward compatibility. The PDP-11 data types are a subset of the VAX-11 data types. This can be very convenient if you want to transfer your PDP-11 application to an environment with 32-bit addressing.

The PDP-11 data types may be separated into categories according to the groups of instructions that operate on them. They are:

- Integer data

- Character string data

- Decimal string data

- Floating point data

Integer data types are supported by the basic PDP-11 instruction set. The string data types are used by the Commercial Instruction Set, which is offered as an option on some PDP-11 processors. Floating point data types are manipulated by the Floating-Point Instruction Set (FP-11) which runs on a Floating-Point Processor (FPP) which may be either a separate processor or microcode.

The Commercial Instruction Set (CIS-11) is treated in detail in Chapter Seven. The floating point instructions are described in Chapter 6 (The Floating Point Processor—FP-11) and in Appendix C (The Floating Instruction Set—FIS).

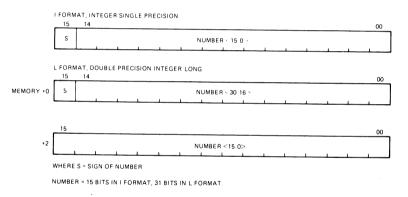

## INTEGER DATA TYPES

Integer data types include 8-bit bytes, and 16-bit words. Integer data types are stored in memory in binary form, which is represented entirely in ones and zeroes. As unsigned quantities, integers extend upward from 0. As signed quantities, the integers are represented in two's complement form. This means that a negative number is one greater than the bit-by-bit complement of its positive counterpart. Thus, posi-

tive numbers have a 0 most significant bit (MSB). The MSB or sign bit is always 1 for negative values.

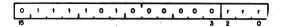

## **Byte**

A byte is eight contiguous bits starting on an addressable byte boundary or located in a register, Rn <7:0>. The bits are numbered from the right 0 through 7. The byte is specified by its address A. When interpreted as a signed quantity, a byte is a two's complement integer with bits increasing in significance from 0 through 6, and with bit 7 designating the sign. The value of the integer is in the range - 128 through 127.

For the purposes of addition, subtraction, and comparison, PDP-11 instructions also provide direct support for the interpretation of a byte as an unsigned integer with a value in the range 0 through 255.

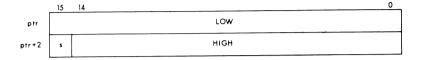

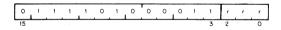

#### Word

A word, two contiguous bytes, starts on an arbitrary word boundary or is located in a register Rn < 15:0 >.

Words are specified by their address A, the address of the byte containing bit 0. When interpreted as a signed quantity, a word is a two's complement integer with bits increasing in significance from 0 through 14, and with bit 15 designating the sign. The value of the integer is in the range — 32768 through 32767. For the purposes of addition, subtraction, and comparison, PDP-11 instructions also provide direct support for the interpretation of a word as an unsigned integer with a value in the range 0 through 65535.

## **CHARACTER DATA TYPES**

There are three different character data types. The "character" is a single byte, and is an abbreviated string of length 1. The "character string" is a contiguous group of bytes in memory. The third is a "character set."

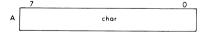

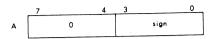

The character is an 8-bit byte:

The character is used as an operand by CIS-11 instructions. When it appears in a general register, the character is in the low-order half; the high-order half of the register must be zero. When it appears in the instruction stream, the character is in the low-order half of a word; the high-order half of the word must be zero. If the high-order half of a word which contains a character is nonzero, the effect of the instruction which uses it will be UNPREDICTABLE.

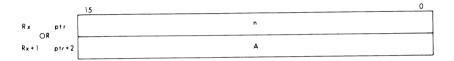

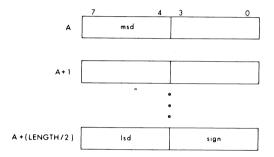

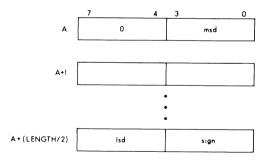

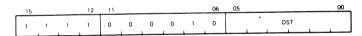

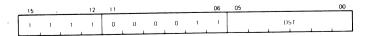

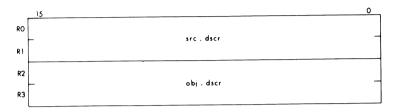

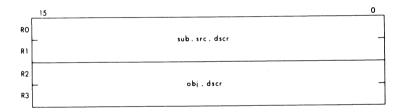

A character string is a contiguous sequence of bytes in memory that begins and ends on a byte boundary. It is addressed by its most significant character (lowest address). The highest address is the least significant character. It is specified by a two-word descriptor with the attributes of length and lowest address. The length is an unsigned binary integer which represents the number of characters in the string and may range from 0 to 65,535. A character string with zero length is said to be vacant: its address is ignored. A character string with nonzero length is said to be occupied.

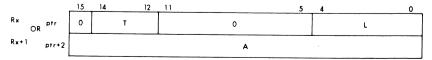

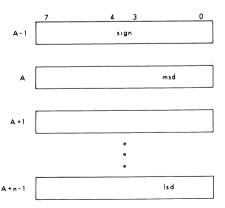

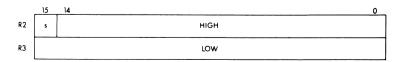

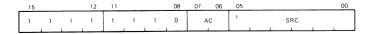

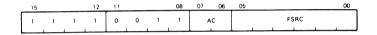

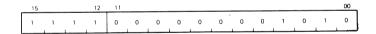

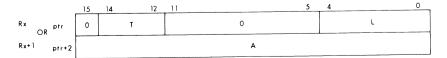

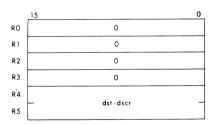

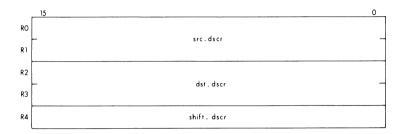

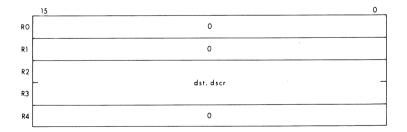

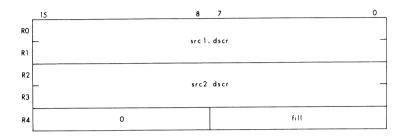

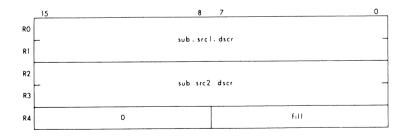

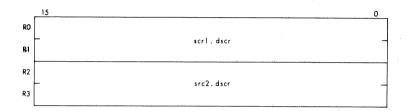

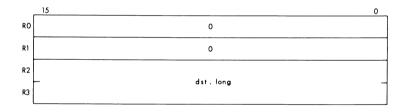

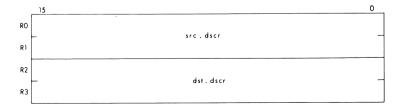

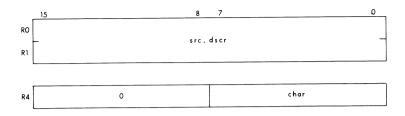

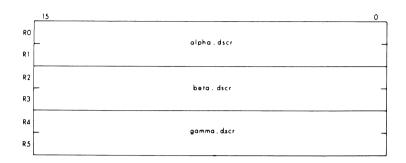

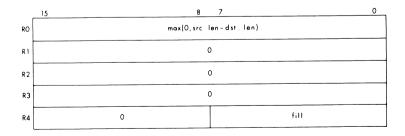

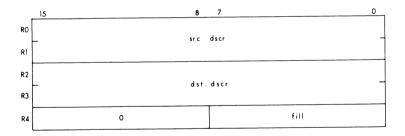

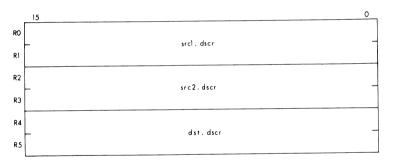

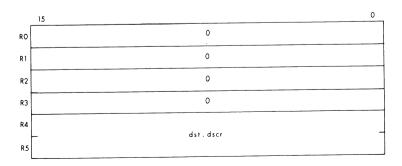

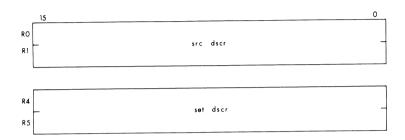

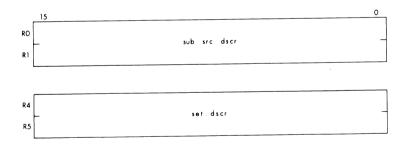

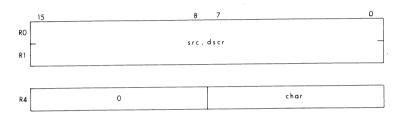

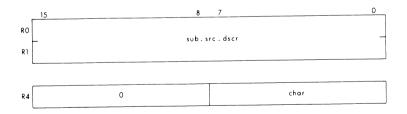

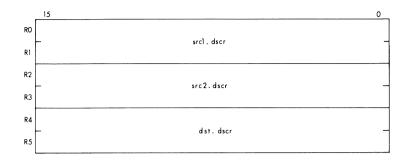

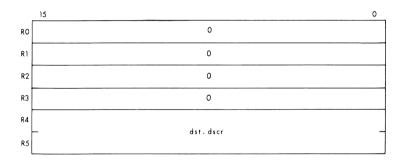

The character string descriptor is used as an operand by CIS-11 instructions. It appears in two consecutive general registers, or in two consecutive words in memory pointed to by a word in the instruction stream. The following figure shows the descriptor for a character string of length "n" starting at address "A" in memory:

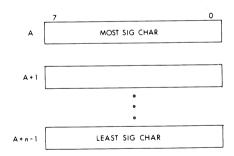

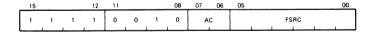

The following figure shows the character string in memory:

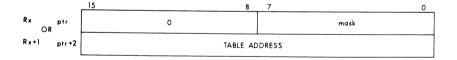

A "character set" is a subset of the 256 possible characters that can be encoded in a byte. It is specified by a descriptor which consists of the address of a 256-byte table and an 8-bit mask. The address is of the zeroth byte in the table. Each byte in the table specifies up to eight orthogonal character subsets of which the corresponding character is a member. The mask selects which combinations of these orthogonal subsets constitute the entire character set. In effect, each bit in the mask corresponds to one of eight orthogonal subsets that may be en-

coded by the table. The mask specifies the union of the selected subsets into the character set. Typical sets would be: uppercase, lowercase, nonzero digits, end of line, etc.

Operationally, a character (char) is considered to be in the character set if the evaluation of (M[table.adr + char] AND mask) is not equal to zero. The character is not in the character set if the evaluation is zero. Each byte in the table indicates which combination of up to eight orthogonal character subsets (i.e., one for each of the eight bit vectors 00000001° 00000010° 00000100° 00001000° 00010000° 00100000° 010000002 and 100000002) the corresponding character is a member. The mask specifies which union of the eight orthogonal character subsets constitute the total character set. For example, if the eight-bit vector 000000012 appearing in the table corresponds to the character subset of all uppercase alphabetic characters, 00000010₂ appearing in the table corresponds to the character subset of all lowercase alphabetic characters, and 000001002 appearing in the table corresponds to the decimal digits, then using the mask 000000112 with this table specifies the character set of all alphabetic characters, and using the mask 000001112 specifies the character set of all alphanumeric characters.

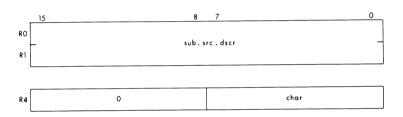

The character set descriptor is used as an operand by CIS-11 intructions. It appears in two consecutive general registers, or in two consecutive words in memory pointed to by a word in the instruction stream. If the high-order half of the first descriptor word is nonzero, the effect of an instruction which uses a character set will be UNPRE-DICTABLE.

#### **DECIMAL STRING DATA TYPES**

Two classes of decimal string data types—numeric strings and packed strings—are defined. Both have similar arithmetic and operational properties; they primarily differ in the representation of signs and the placement of digits in memory.

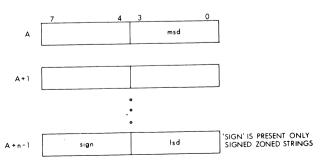

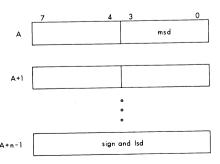

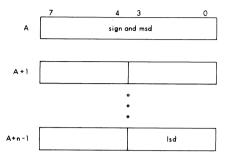

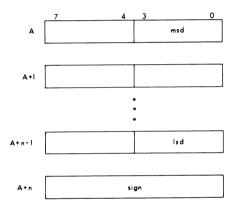

The numeric string data types are signed zoned, unsigned zoned, trailing overpunch, leading overpunched, trailing separate and leading separate. The packed string data types are signed packed and unsigned packed. Instructions which operate on numeric strings permit each numeric string operand to be separately specified; similarly,

packed string instructions permit each packed string operand to be separately specified. Thus, within each of the two classes of decimal strings, the operands of an instruction may be of any data type within the appropriate class.

Decimal strings exist in memory as contiguous bytes which begin and end on a byte boundary. They represent numbers consisting of 0 to 31  $_{\rm 10}$  digits, in either sign-magnitude or absolute-value form. Sign-magnitude strings (SIGNED) may be positive or negative; absolute-value strings (UNSIGNED) represent the absolute value of the magnitude. Decimal numbers are whole integer values with an implied decimal radix point immediately beyond the least significant digit; they may be conceptually extended with zero digits beyond the most significant digit.

A four-bit binary coded decimal representation is used for most digits in decimal strings. A four-bit half byte is called a "nibble" and may be used to contain a binary bit pattern which represents the value of a decimal digit. The following table shows the binary nibble contents associated with each decimal digit:

| digit | nibble | digit | nibble |

|-------|--------|-------|--------|

| 0     | 0000   | 5     | 0101   |

| 1     | 0001   | 6     | 0110   |

| 2     | 0010   | 7     | 0111   |

| 3     | 0011   | 8     | 1000   |

| 4     | 0100   | 9     | 1001   |

Each decimal string data type may have several representations. These representations permit a certain latitude when accepting source operands. Decimal string data types have a PREFERRED representation, which is a valid source representation and which is used to construct the destination string. Additional ALTERNATE representations are provided for some decimal data types when accepting source operands.

Decimal strings used as source operands will not be checked for validity. Instructions will produce UNPREDICTABLE results if a decimal string used as a source operand contains an invalid digit encoding, invalid sign designator, or, in the case of overpunched numbers, an invalid sign/digit encoding.

When used as a source, decimal strings with zero magnitude are unique, regardless of sign. Thus, both positive and negative zero have identical interpretations.

Conceptually, decimal string instructions first determine the correct result, and then store the decimal string representation of the correct

result in the destination string. A result of zero magnitude is considered to be positively signed. If the destination string can contain more digits than are significant in the result, the excess most significant destination string digits have zero digits stored in them. If the destination string cannot contain all significant digits of the result, the excess most significant result digits are not stored; the instruction will indicate decimal overflow. Note that negative zero is stored in the destination string as a side effect of decimal overflow where the sign of the result is negative and the destination is not large enough to contain any nonzero digits of the result.

If the destination string has zero length, no resulting digits will be stored. The sign of the result will be stored in separate and packed strings, but not in zoned and overpunched strings. Decimal overflow will indicate a nonzero result

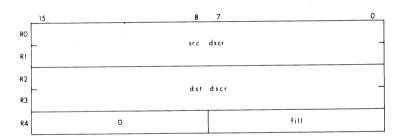

# **Decimal String Descriptors**

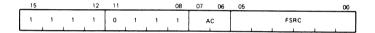

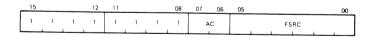

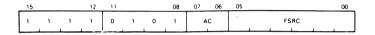

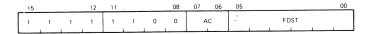

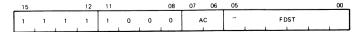

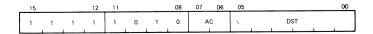

Decimal strings are represented by a two-word descriptor. The descriptor contains the length, data type, and address of the string. It appears in two consecutive general registers (register form of instructions), or in two consecutive words in memory pointed to by a word in the instruction stream (in-line form of instructions). The unused bits are reserved by the architecture and must be 0. The effect of an instruction using a descriptor will be unpredictable if any nonzero reserved field in the descriptor contains nonzero values or a reserved data type encoding is used. The design of the numeric and packed string descriptors are identical:

#### First Word

Number of digits specified as an unsigned binalength <4:0>

rv integer

data type Specifies which decimal data type representa-

<14:12> tion is used

Second Word

Specifies the address of the byte which contains address the most significant digit of the decimal string

<15:0>

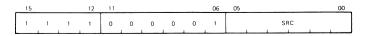

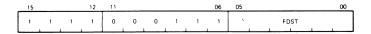

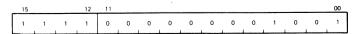

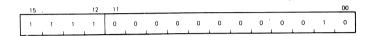

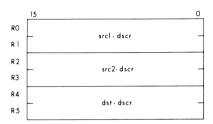

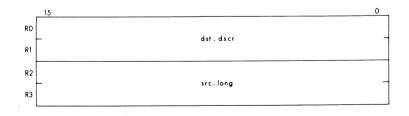

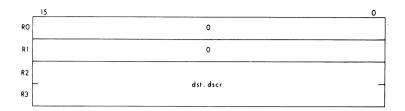

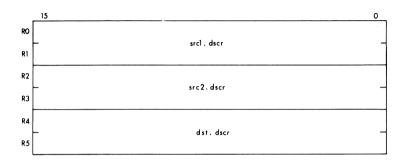

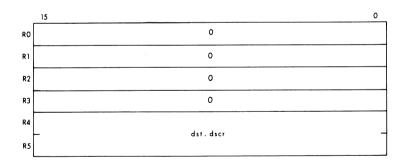

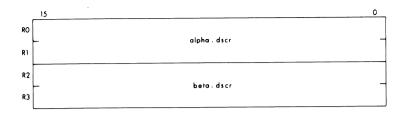

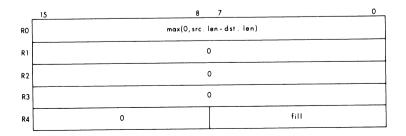

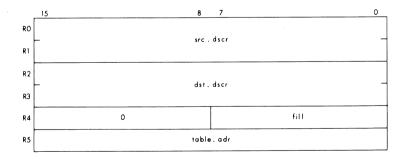

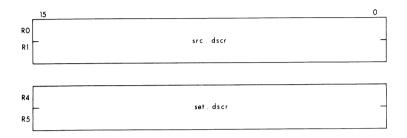

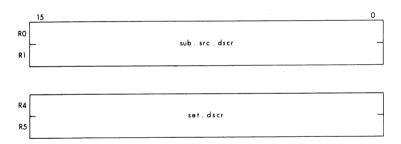

The following figure shows the descriptor for a decimal string of data type "T" whose length is "L" digits and whose most significant digit is at address "A":

The encodings (in binary) for the NUMERIC string data type field are:

| 000 | signed zoned         |

|-----|----------------------|

| 001 | unsigned zoned       |

| 010 | trailing overpunch   |

| 011 | leading overpunch    |

| 100 | trailing separate    |

| 101 | leading separate     |

| 110 | —reserved to DIGITAL |

| 111 | —reserved to DIGITAL |

|     |                      |

The encodings (in binary) for the PACKED string data type field are:

| 000 | -reserved to DIGITAL |

|-----|----------------------|

| 001 | —reserved to DIGITAL |

| 010 | —reserved to DIGITAL |

| 011 | —reserved to DIGITAL |

| 100 | —reserved to DIGITAL |

| 101 | —reserved to DIGITAL |

| 110 | signed packed        |

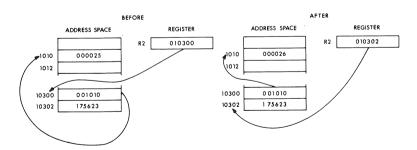

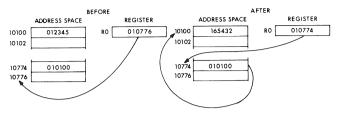

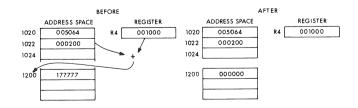

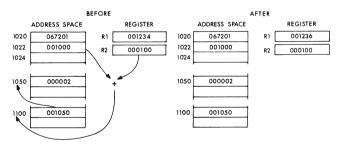

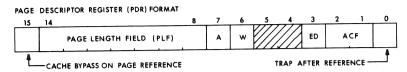

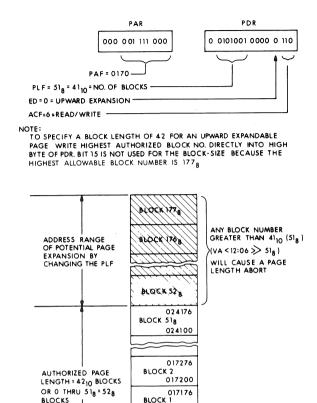

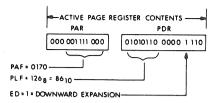

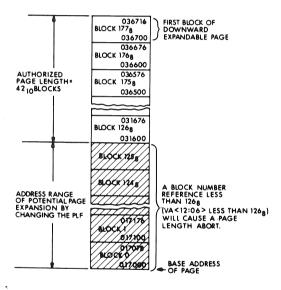

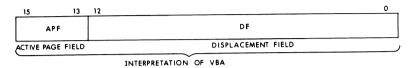

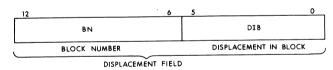

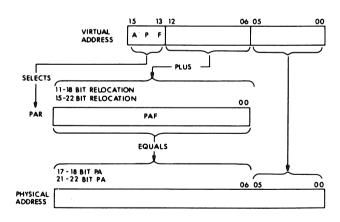

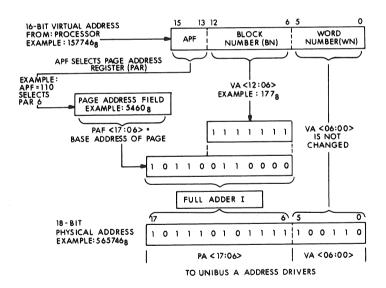

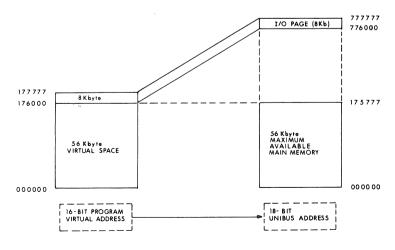

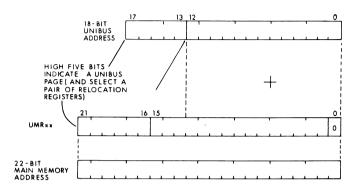

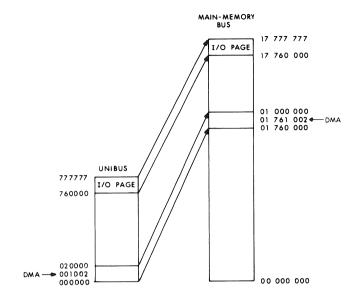

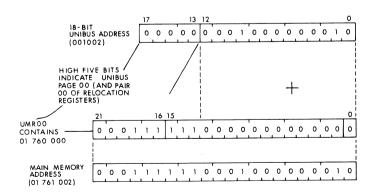

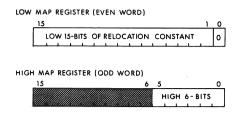

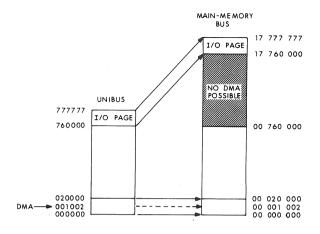

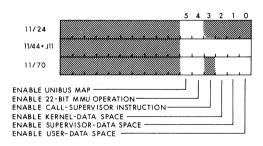

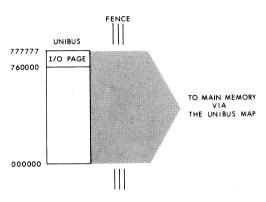

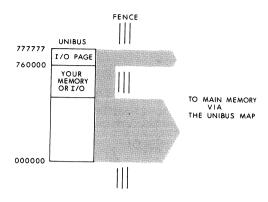

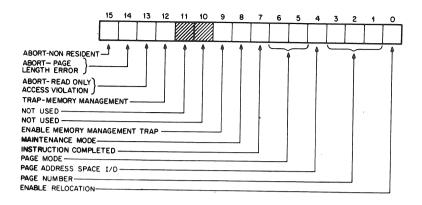

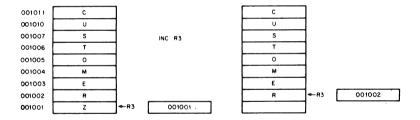

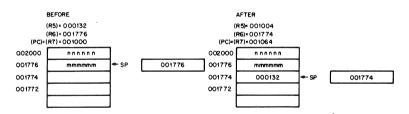

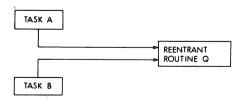

| 111 | unsigned packed      |