# PDP-11

Microcomputer Interfaces Handbook

## PDP-11

Microcomputer Interfaces Handbook

digital

DIGITAL Facility, Hudson, Massachusetts

### **CORPORATE PROFILE**

Digital Equipment Corporation designs, manufactures, sells and services computers and associated peripheral equipment, and related software and supplies. The Company's products are used world-wide in a wide variety of applications and programs, including scientific research, computation, communications, education, data analysis, industrial control, timesharing, commercial data processing, word processing, health care, instrumentation, engineering and simulation.

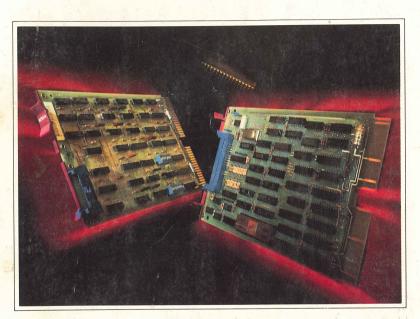

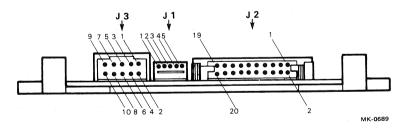

Cover— Flanked by two DIGITAL interface board modules— the IBV11-A instrument bus interface and the DPV11-DA serial synchronous line interface— is DIGITAL's first available serial line communications chip interface— the DC319-AA DLART. The DLART represents DIGITAL's latest advancement and commitment to an even lower level of integration than board-level components, while still providing proven PDP-11 architecture. System and hardware designers, as well as other customers will find this new level of integration an attractive alternative for application designs based on chip-level microcomputer-based products, including implementation of DIGITAL's new family of chip-level processors— the T-11, the F-11, and the J-11.

UNIVERSITY OF NEW ENGLAND

# PDP-11

Microcomputer Interfaces Handbook

### Copyright© 1983 Digital Equipment Corporation. All Rights Reserved.

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

DEC, DECnet, DECsystem-10, DECSYSTEM-20, DECtape

DECUS, DECwriter, DIBOL, Digital logo, IAS, MASSBUS, OMNIBUS

PDP, PDT, RSTS, RSX, SBI, UNIBUS, VAX, VMS, VT

are trademarks of

Digital Equipment Corporation

This handbook was designed, produced, and typeset by DIGITAL's New Products Marketing Group using an in-house text-processing system.

### **CONTENTS**

### PART 1 INTRODUCTION

| LSI-11 FAMILY CHARACTERISTICS                    |

|--------------------------------------------------|

| SPECIFICATIONS                                   |

| DESCRIPTION OF OPTION CATEGORIES 5               |

| CONFIGURATION                                    |

|                                                  |

| PART 2 LSI-11 BUS INTERFACE DESCRIPTIONS         |

| AAV11-A 4-Channel 12-Bit D/A Converter           |

| AAV11-C 4-Channel 12-Bit D/A Converter           |

| ADV11-A Analog-to-Digital Converter              |

| ADV11-C Analog-to-Digital Converter              |

| AXV11-C Analog Input/Output Board 70             |

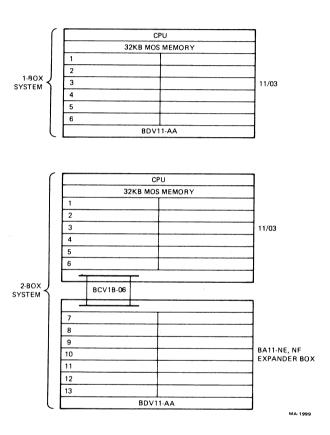

| BA11-M Expansion Box                             |

| BA11-N Mounting Box                              |

| BA11-S Mounting/Expander Box                     |

| BA11-VA Expansion Mounting Box                   |

| BDV11 Diagnostic, Bootstrap, Terminator          |

| DC319-AA DLART Asynchronous Receiver/Transmitter |

| DCK11-AA,-AC Program Transfer Interface          |

| DCK11-AB,-AD Direct Memory Access Interface 190  |

| DDV11-B Backplane                                |

| DLV11 Serial Line Unit                           |

| DLV11-E Asynchronous Line Interface              |

| DLV11-F Asynchronous Line Interface              |

| DLV11-J Four Asynchronous Serial Interfaces      |

| DMV11 Synchronous Line Controller                |

| DLV11-KA EIA to 20 mA Converter                  |

| DPV11-DA Synchronous Serial Line Interface 520   |

| DRV11 Parallel Line Unit                         |

| DRV11-B Direct Memory Access Interface           |

| DRV11-J High-Density Parallel Interface          |

| DRV11-P LSI-11 Bus Foundation Module             |

| DUV11 Line Interface                             |

| DZV11 Asynchronous Multiplexer                   |

| H780 Power Supply                                |

| H780 Power Supply                                |

| H9270 Backplane                                  |

<sup>\*</sup> This interface product appears out of the alphanumeric sequence in this handbook because it was included just prior to publication.

| H9273-A Backplane                                                 | 372 |

|-------------------------------------------------------------------|-----|

| H9275-A Backplane                                                 |     |

| H9276 Backplane                                                   | 383 |

| H9281 Backplane                                                   |     |

| IBV11-A Instrument Bus Interface                                  | 393 |

| KPV11-A, -B, -C Power-Fail/Line-Time Clock/Terminator             | 415 |

| KWV11-A Programmable Realtime Clock                               | 420 |

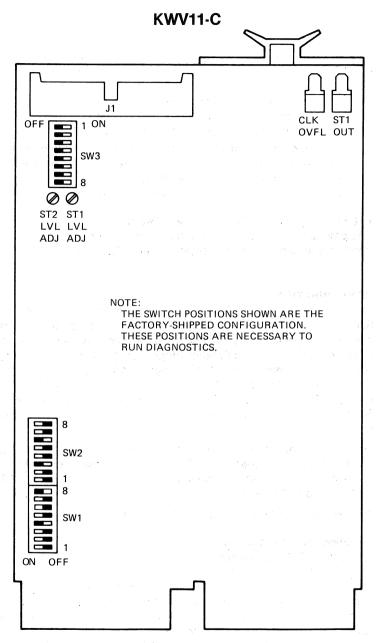

| KWV11-C Programmable Realtime Clock                               | 426 |

| LPV11 Printer Option                                              | 449 |

| REV11-A Terminator, REV11-C DMA Refresh, Bootstrap                | 457 |

| RLV12 Disk Controller                                             | 556 |

| RXV11 Floppy Disk Option                                          | 459 |

| RXV21 Floppy Disk Option                                          | 465 |

| TU58 Cartridge Tape Drive                                         |     |

| VK170-CA Serial Video Module                                      | 495 |

| W9500 Series High-Density Wire-Wrappable Modules                  | 504 |

|                                                                   |     |

|                                                                   |     |

|                                                                   |     |

| APPENDIX A ASSIGNMENT OF                                          |     |

| ADDRESSES AND VECTORS                                             | 567 |

|                                                                   |     |

| APPENDIX B ASYNCHRONOUS SERIAL LINE UNIT (SLU)                    |     |

| COMPARISONS                                                       | 585 |

|                                                                   |     |

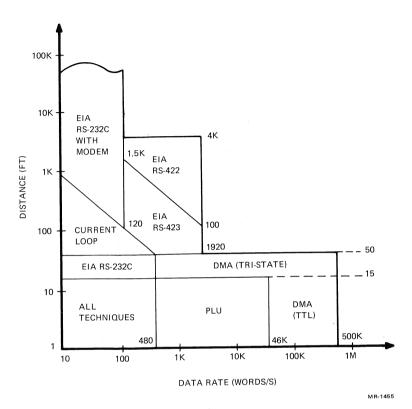

| APPENDIX C COMPARISON OF DATA TRANSMISSION                        |     |

| TECHNIQUES                                                        | 593 |

|                                                                   |     |

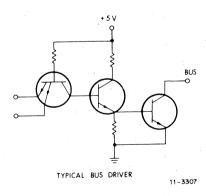

| APPENDIX D BUS RECEIVERS AND BUS DRIVERS                          | 596 |

|                                                                   |     |

| APPENDIX E CABLING SUMMARY                                        | 500 |

| AFFERDIA E CADEINO SCININATTI I I I I I I I I I I I I I I I I I I | 555 |

| APPENDIX F LSI-11 DOCUMENTATION                                   | 601 |

|                                                                   |     |

| NDEX                                                              | 612 |

|                                                                   |     |

<sup>\*</sup> This interface product appears out of the alphanumeric sequence in this handbook because it was included just prior to publication.

### **PREFACE**

The 1983-84 Microcomputer Interfaces Handbook is the companion publication to the 1982 Microcomputers and Memories Handbook.

Designed in the form of a catalog, the purpose of this handbook is to provide DIGITAL customers with quick and handy reference material on DIGITAL microcomputer interface options that connect to the LSI-11 bus. Though user applications may vary widely, the detailed logic, configuration, and installation information presented in this handbook should be sufficient to satisfy their needs. In most cases throughout this handbook, the interfaces have a detailed introductory section, a features section, specifications, configuration, and descriptive narrative— especially on the newer interface products. The major product sections in the handbook include: Interface Options, Communications Options, Peripherals, Backplanes, Enclosures (boxes), Cabinets, Power Supplies, Cables and Connectors, Intergrated Circuits, and miscellaneous options available for DIGITAL'S diverse family of both board-level and systems-based microcomputers.

A major goal of this handbook is to present the most recently introduced interface products and still provide needed but basic information on the older interface products. Detailed passages on 11 new interface products are currently found in this handbook, including a new family of analog I/O boards— the AAV11-C, the ADV11-C, and the AXV11-C; the KWV11-C programmable realtime clock; the H9275-A and H9276 backplanes; the BA11-S mounting/expander box; the DPV11-DA synchronous serial line interface; the DMV11 synchronous line controller; the RLV12 disk controller; and for the first time, we are including a section on the new serial line communications chip interface— the DC319-AA DLART. Passages on the DPV11-DA, the DMV11, and the RLV12 appear at the end of Part 2 of this handbook. These three interface products are out of alphanumeric sequence because they were included (immediately) prior to the time of publication.

Since this handbook was last published, many DIGITAL microcomputer interface products that were written about extensively then are currently not necessarily the most technically advanced or newest ones available. For example, in a case where a customer who still uses the AAV11-A four-channel 12-bit D/A converter, a DIGITAL interface introduced a few years back, information pertaining to this interface was found in the first few pages of the 1981 Microcomputer Interfaces Handbook. In this handbook, however, an abbreviated version briefly introduces and describes its features and benefits, and lists its specifications. Appendix F in the back of this handbook lists all the documention and order numbers needed to supplement these older

products. For users requiring extensive information on some of these microcomputer interfaces, this appendix lists all the necessary reference material, at several levels of technicality, including user documents, configuration guides, and data sheets.

A section devoted to mass storage peripherals will be covered in a future handbook. For users desiring information on DIGITAL's memory offerings and detailed information on LSI-11 bus signals, please consult the 1982 Microcomputers and Memories Handbook. The order code for the Microcomputer and Memories Handbook is EB-20912-20.

### part1 introduction

This handbook is a reference guide for interface and peripheral hardware options that can be installed on the LSI-11 bus. It includes descriptions, specifications, configuration information, programming information as applicable to the options, and functional theory. Because the hardware options described in this handbook are designed to interface with a processor via the LSI-11 bus, the user should be familiar with the contents of the 1982 Microcomputer and Memories Handbook.

The 1983-84 Microcomputer Interfaces Handbook is organized into two parts. Part 1 contains general information about microcomputer interfaces. Part 2 contains descriptions of the interface options in alphanumeric sequence.

Digital Equipment Corporation designs and manufacturers the options described in this handbook. Our general design criterion is to provide maximum system throughput for options when they are installed on the LSI-11 bus. LSI-11 bus-compatible processors, interfaces, and peripherals are designed to work together to provide a broad spectrum of system-compatible hardware options. Memory and peripheral devices can be used with various LSI-11 bus configurations and the system can later be expanded or modified to meet new system requirements. This hardware flexibility, when coupled with DIGITAL software and support, provides a single source for all present and future microcomputer processing needs.

### **LSI-11 FAMILY CHARACTERISTICS**

LSI-11 bus systems include various processors, memory and peripheral device options, and software. Some of the characteristics of the LSI-11 bus systems are:

- Low-cost powerful components for integration into any small- or medium-sized computer system.

- Direct addressing of all memory locations and peripheral device registers.

- Efficient processing of 8-bit bytes (characters) without the need to rotate, swap, or mask.

- Asynchronous bus operation that allows system components to run at their highest possible speed; replacement with faster devices means faster operation without other hardware or software changes.

- A module component design that provides ease and flexibility in configuring systems.

- Inherent direct memory access capabilities for high data rate devices.

- A bus structure that provides position-dependent priority for peripheral device interfaces connected to the I/O bus.

- Vectored interrupts that allow service routine entry without device polling.

### **Processors**

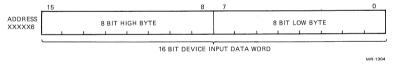

The processor is connected to the LSI-11 bus (backplane) as a subsystem that executes programs and arbitrates usage of the LSI-11 bus for peripherals. It contains multiple, high-speed, general-purpose registers that can be used as accumulators, address pointers, index registers, and other specialized functions. The processor can perform data transfers directly between peripheral input/output (I/O) devices and memory without disturbing the processor registers. Data transfers include both 16-bit word and 8-bit byte data.

### LSI-11 Bus

System components, including the processor, memory, and peripherals, are interconnected and communicate with each other via the LSI-11 bus. The form of communication is the same for all devices on the bus; instructions that communicate with memory can communicate with peripheral devices. Each device, including memory locations and peripheral device registers, is assigned an individual byte or word address on the LSI-11 bus.

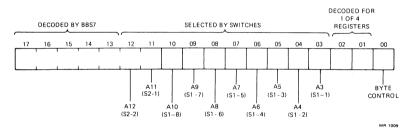

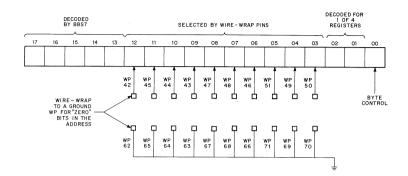

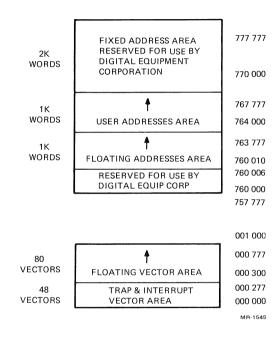

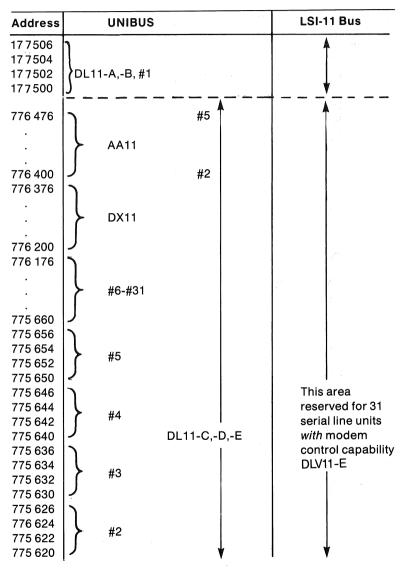

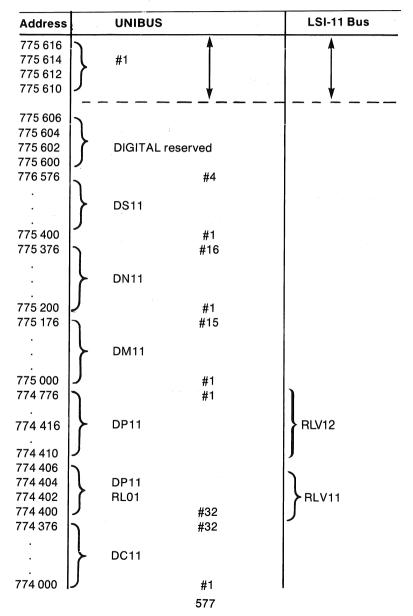

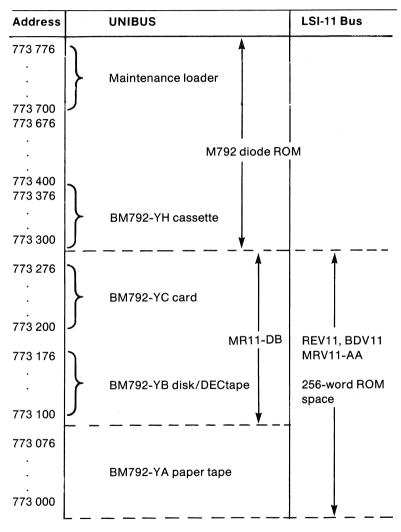

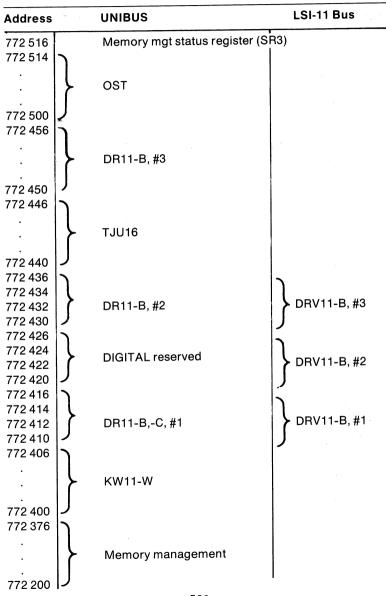

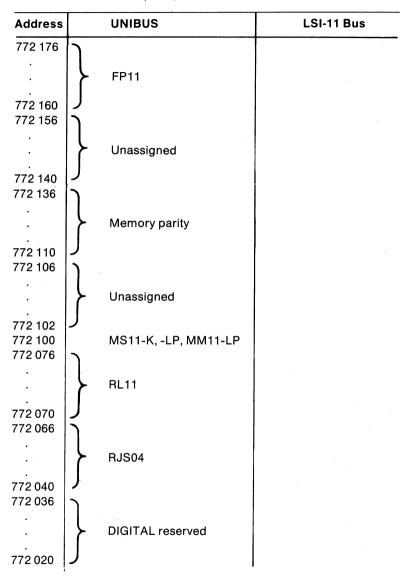

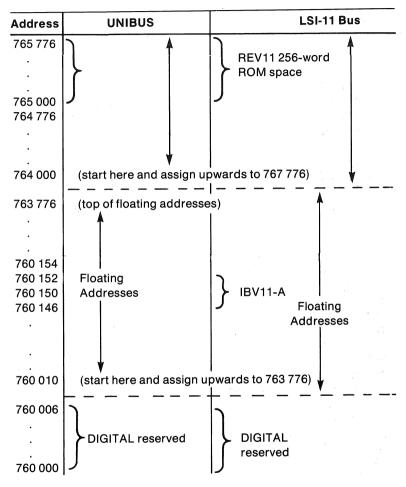

The LSI-11 bus supports 16-, 18-, and 22-bit addresses. However, processors and peripherals having a 22-bit addressing capability are completely PDP-11 hardware- and software-compatible within the 18-bit or 16-bit limitation. Simarily, 18-bit addressing devices are downward-compatible to 16-bit addressing. By PDP-11 convention, all peripheral device addresses are located within the upper 4K address space in the system, whether 16-bit or 18-bit addresses are used. This 4K address space is called the I/O page or "bank 7."

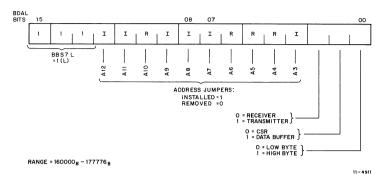

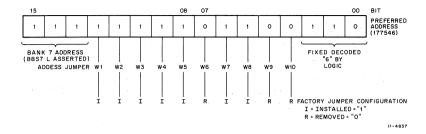

Whenever the I/O page is addressed, the processor must assert the BBS7 L bus signal. All peripheral devices use this signal line during addressing rather than decoding address bits < 15:13 > or < 17:13 > . An active (asserted) BBS7 L signal will always indicate an address in the I/O page, enabling peripheral device addressing.

Peripheral device addresses within the I/O page are decoded by each peripheral device. Each peripheral device will include one or more "device register(s)." These registers can be accessed under program con-

trol in exactly the same manner as memory locations. Unique addresses within the I/O page are encoded on address bits < 15:00 >.

### NOTE

Address bits, for the purpose of this discussion, are logical states present on LSI-11 bus signal lines BDAL<17:00>L during the addressing portion of a bus cycle.

Refer to the appropriate processor handbook for a complete description of bus transactions, including bus cycles, addressing, etc.

### **Device Registers**

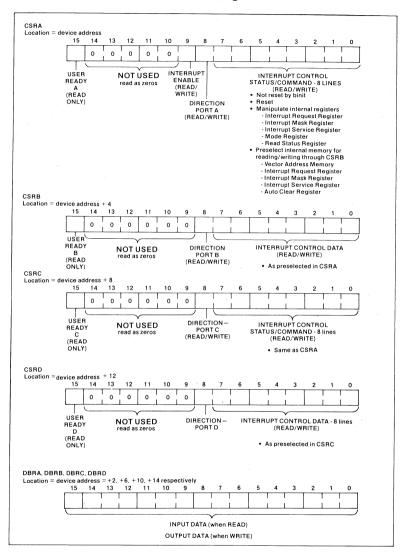

All peripheral devices are defined by one or more device registers that are addressed as part of the main memory. These registers are generally designated control and status registers.

Control and status registers (CSRs) contain all the necessary information to establish communications with the device. Some devices will require fewer than 16 status bits, while other devices could require more than 16 bits and therefore will require additional registers. The bits of the CSR have predetermined assigned functions. Typical bit functions include interrupt enable, error, done or ready, and enabled.

Data buffer registers (DBRs) are for temporarily storing data to be transferred into and out of the processor. The number and type of data registers is a function of the individual peripheral device requirements.

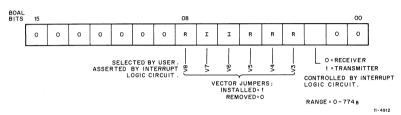

### Interrupts

Interrupts allow devices to obtain processor service when they are "ready" for service, or "done" with a specific operation. The interrupt structure allows the processor to execute other programs while one or more peripherals are "busy." When a peripheral requires service it requests an interrupt. The processor completes execution of the present instruction, saves PC and PS words on the stack, and acknowledges the interrupt. The highest priority peripheral device currently requesting interrupt service responds by inputting its interrupt vector address to the processor. The processor uses this vector address as a pointer to two memory locations containing the PC (starting address) and PS for the peripheral device interrupt service routine. Program control is transferred from the interrupted program to the routine associated with the requesting peripheral device. Note that no device polling is required, since the interrupt vector is unique for that device. Once the

device service routine execution has been completed, control is returned either to the previously interrupted program or to another peripheral device requesting interrupt service.

### **Memory Address**

Memory addresses are generally limited to the address space other than the I/O page. However, the I/O page can contain read-only memory (ROM) for disk bootstraps, paper tape loaders, diagnostics, etc. or read/write memory for DMA buffers. The system designer must use care in assigning memory addresses within the I/O page to avoid conflicts with peripheral device addresses used for actual system hardware, or addresses that system software may attempt to access for peripheral devices not actually installed in the system. See Appendix A for the standard assignments of the addresses in the I/O page.

### **SPECIFICATIONS**

All the LSI-11 bus modules will operate under the following conditions:

Temperature 5° to 60° C (41° to 140° F) Humidity 10 to 95% (no condensation)

When operating at the maximum outlet temperature (60° C or 140° F), adequate air flow must be maintained to control the inlet to outlet temperature rise across the modules to 5° C (9° F) maximum. The air flow should be directed to flow across the modules.

All the individual module specifications are included in the detailed descriptions of the peripheral or option. A summary of the module characteristics is provided in Table 2; these characteristics are defined as follows:

- The option designation is the alphanumerical code assigned to the option.

- 2. The module number is the number assigned to the interface modules that are connected to the LSI-11 bus. This number is printed on the module handle and can be used as a quick reference to determine what specific options are installed in any system. The module numbers are listed numerically in Table 3 so that the user can identify the options installed by using the module numbers.

- 3. The module description identifies the category of the option.

- 4. The power requirements specify the power by the option when connected to the bus backplane. These requirements are used to determine the total power supply loading within a single system.

- The bus loads for ac and dc loading are provided so that the user can calculate the total ac and dc loading for any system.

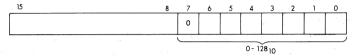

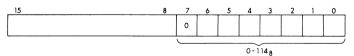

- 6. The interface modules are standarized as either a double or a quad and all are extended length. The double size module is 13.2 cm (5.2 in.) high, 22.8 cm (8.9 in.) long, and 1.27 cm (0.5 in.) wide. The quad size module is 26.5 cm (10.5 in.) high, 22.8 cm (8.9 in.) long, and 1.27 cm (0.5 in.) wide (Figure 1).

### **DESCRIPTION OF OPTION CATEGORIES**

The LSI-11 bus peripherals and options are classified into general categories that pertain to their performance and function. This listing indicates the wide span of equipment capability available to the user.

### Interface Options

AAV11-A

The AAV11-A is a 4-channel, 12-bit digital-to-analog converter module that includes control and interfacing circuits. It has four D/A converters, a dc-dc converter that provides power to the analog circuits, and a precision voltage reference. Each channel has its own holding register that can be addressed separately and provides 12 bits of resolution. Bits 0, 1, 2, and 3 of the fourth holding register are brought out to the I/O connector so that they can be used as a 4-bit digital output register.

AAV11-C

The AAV11-C is a 4-channel, 12-bit digital-to-analog converter module that has four individually addressable, separately controlled digital-to-analog converters (DACs), each with 12 bits of resolution. Each DAC can be written or read in either word or byte format. One of the DACs also has four digital output bits for creating control signals to an analog instrument. The D/A converters accept data from a program controlled interface in either a binary notation for unipolar output, or offset binary for bipolar output.

ADV11-A

The ADV11-A is a 12-bit successive approximation analog-to-digital converter that samples analog data at specified rates and stores the digital equivalent value for processing. The mul-

tiplexer can accommodate up to 16 single-ended or 8 quasi-differential inputs. The converter uses a patented auto-zeroing design that measures the sampled data with respect to its own offset and therefore cancels out its own offset error.

External event inputs can originate at the user's equipment or from the Schmitt trigger output of the KWV11-A clock. Three reference signals are provided for self-testing any channel input. These signals consist of two dc levels and one bipolar triangular waveform. This output can be used with DIGITAL diagnostic software to produce a data base for extremely precise analog linearity testing.

ADV11-C

The ADV11-C is a dual-height LSI-11 bus module that performs analog-to-digital conversions. It may be configured to provide either 16 single-ended, 16 pseudo-differential, or eight true-differential analog input channels with input full scale ranges of either 0 to 10V or -10V to 10V. This board is designed to interface analog instrumentation to the LSI-11 bus, and is suitable for use in a wide variety of industrial and laboratory LSI-11 microcomputer applications such as data acquisition/display, process control, and signal analysis.

The ADV11's precision instrumentation amplifier, under software control, may be programmed to amplify input signals by factors of 1, 2, 4, or 8 before being digitized by the A/D converter. This programmable gain feature provides effective input signal full scale ranges of 10V, 5V, 2.5V, and 1.25V, respectively, especially useful for maintaining maximum resolution of input signals that fall below 50% of the 12-bit A/D converter's 10V range.

AXV11-C

The AXV11-C is a cost-effective analog I/O interface board that has 16 single-ended analog input channels. The AXV11-C offers all the features of the ADV11-C plus two analog output channels,

each with 12-bit D/A converters. Each D/A converter generates an output signal with full 12-bit accuracy and resolution. The D/A's accept data in either binary, offset binary, or two's complement notation.

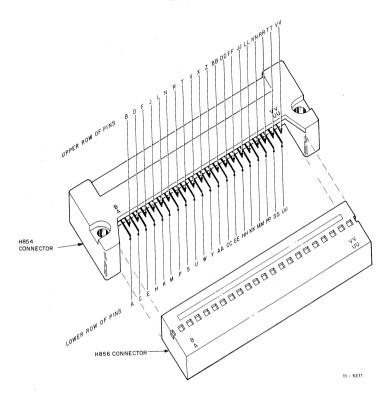

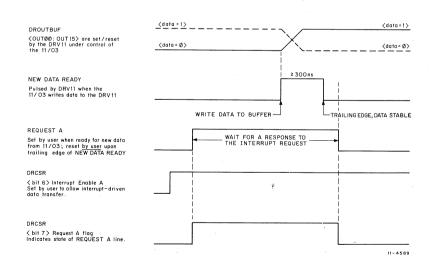

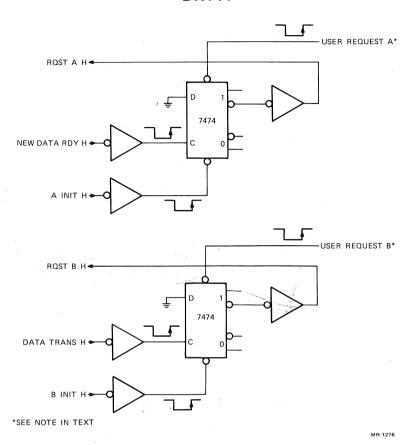

DRV11

The DRV11 is a parallel interface module that is used to interconnect the LSI-11 bus with general-purpose, parallel line TTL or DTL devices. It allows program-controlled data transfers at rates up to 40K words per second and uses LSI-11 bus interface and control logic to generate interrupts and process vector handling. The data are handled by 16 diode-clamped input lines and 16 latched output lines. There are two 40-pin connectors on the module for user interface applications.

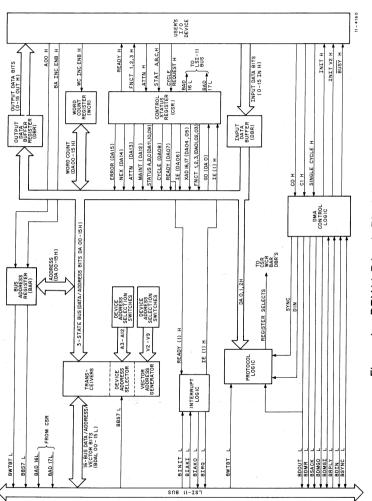

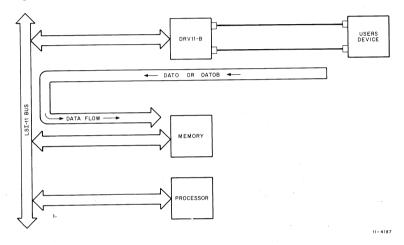

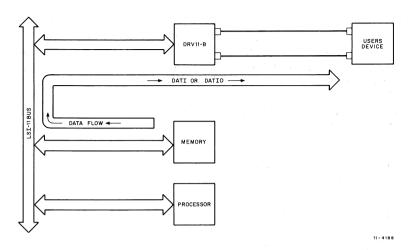

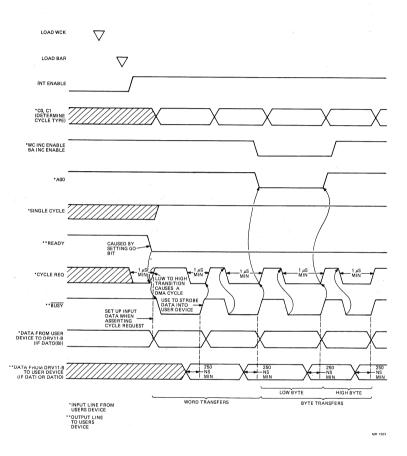

DRV11-B

The DRV11-B is an interface module that uses direct memory access (DMA) to transfer data directly between the system memory and an I/O device. The interface is programmed by the processor to move variable length blocks of 8- or 16-bit data words to or from specified locations in the system memory. Once programmed, there is no processor intervention required. The module can transfer up to 250K 16-bit words per second in the single-cycle mode and up to 500K 16-bit words per second in the burst mode. It also allows read-modify write operations.

DRV11-J

Sixty-four input/output data lines are now available on a double-height module for the LSI-11/2, LSI-11/23, PDP-11/03, and PDP-11/23. The DRV11-J also includes an advanced interrupt structure with bit interruptability up to 16 lines, programmable interrupt vectors, and program selection of fixed or rotating interrupt priority within the DRV11-J. The DRV11-J's bit interrupts for real-time response make it especially useful for sensor I/O applications. It can also be used as a general-purpose interface to custom devices, and two DRV11-Js can be connected back-to-back as a link between two LSI-11 buses.

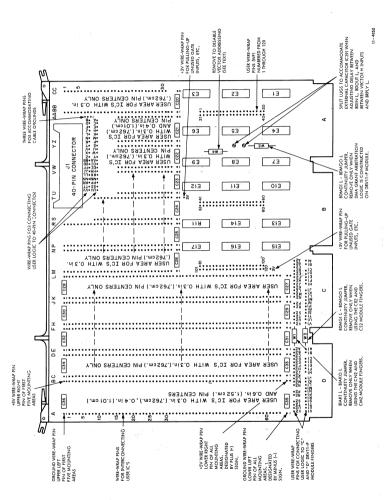

DRV11-P

The DRV11-P is a foundation wire-wrap interface module with a 40-pin I/O connector. Approximately 25 percent of the module is occupied by bus transceivers, interrupt vector generation logic, device comparator logic, protocol logic, and interrupt logic. The remaining 75 percent is for user applications; this portion has plated-through holes for securing ICs and wire-wrap pins for interconnecting the user's curcuits. The plated-through holes can accept 6-, 8-, 14-, 18-, 20-, 22-, 24-, and 40-pin dual-in-line integrated circuits or discrete components.

IBV11-A

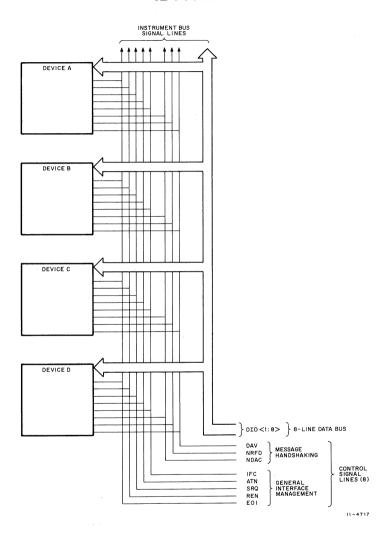

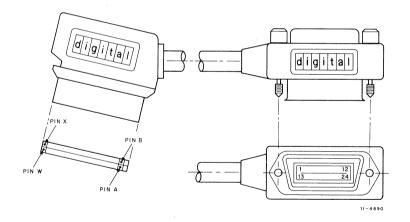

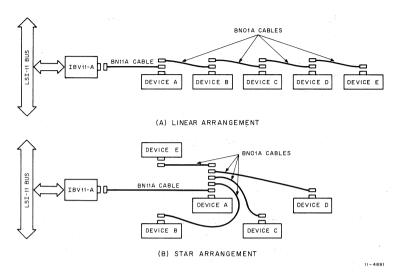

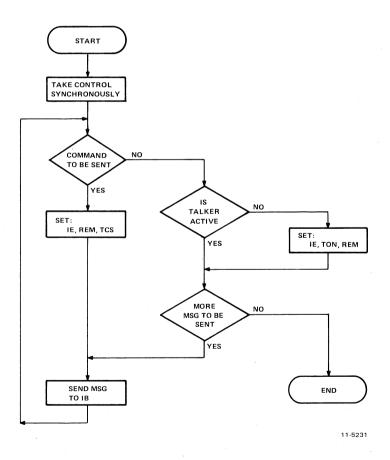

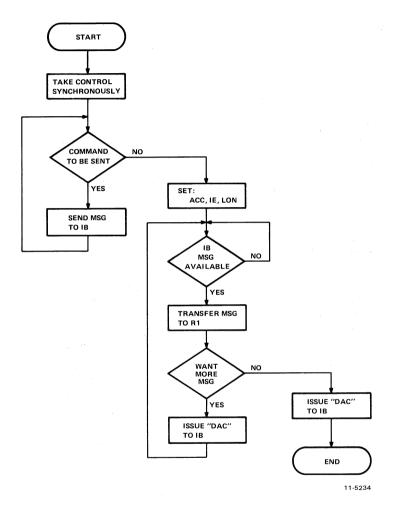

The IBV11-A is an interface module that interconnects the LSI-11 bus with the instrument bus described in IEEE standard 488 1975, "Digital Interface for Programmable Instrumentation." The IBV11-A makes a processor-controlled programmable instrument system possible. The module can accommodate up to 15 IEEE-488 devices and is PDP-11 software-compatible.

KWV11-A

The KWV11-A is a programmable real-time clock/ counter that provides a means of determining time intervals or counting events. It can be used to generate interrupts to the processor at predetermined intervals or establish timing between input and output events. It can also initialize the ADV11-A analog-to-digital converter by a clock counter overflow or by firing a Schmitt trigger. The clock counter has a resolution of 16 bits and can be driven by any one of five crystal-controlled frequencies (100 Hz to 1 MHz), from a line frequency input, or from a Schmitt trigger fired by an external input. The module can operate in any of four programmable modes: single interval, repeated interval, external event timing, and external event timing from zero base.

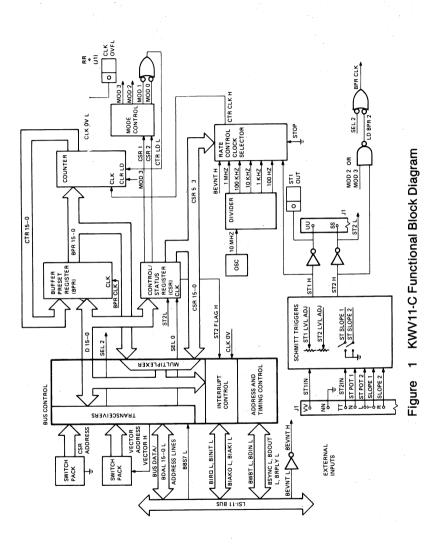

KWV11-C

The KWV11-C, like the KWV11-A, is a programmable real-time clock/counter that provides a variety of means for determining time intervals or counting events. It can generate interrupts to the

processor at predetermined intervals or establish timing between input and output events. It is used to start the ADV11-C analog-to-digital converter or the AXV11-C analog I/O module, either by clock counter overflow or by the firing of a Schmitt trigger. The KWV11-C's two Schmitt triggers each have integral slope and level controls. The Schmitt triggers permit the user to start the clock, initiate A/D conversions, or generate program interrupts in response to external events.

### **Communications Options**

DLV11

The DLV11 is a serial line unit (SLU) that interfaces with asynchronous serial I/O devices. The module has jumper-selectable baud rates (50-9600) and serial word format that includes the number of stop bits, number of data bits, and even, odd, or no parity bit. The DLV11 can support 20 mA current loop interfaces or EIA "data leads only" interfaces.

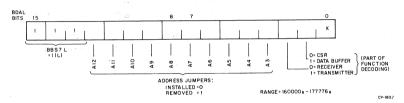

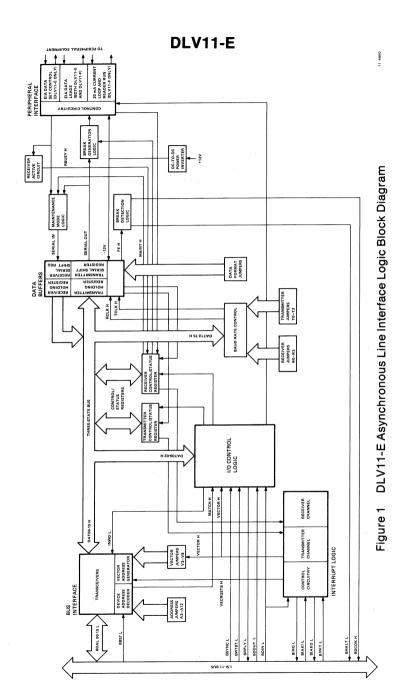

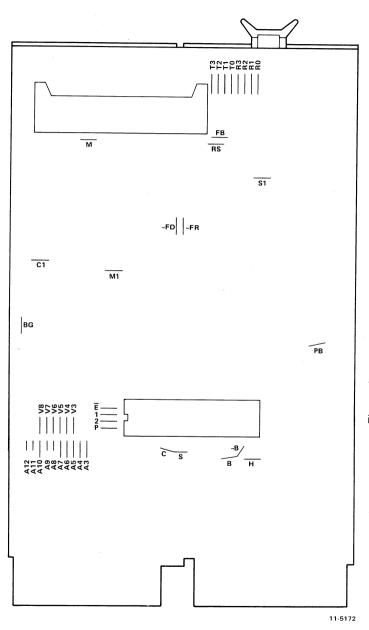

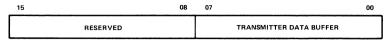

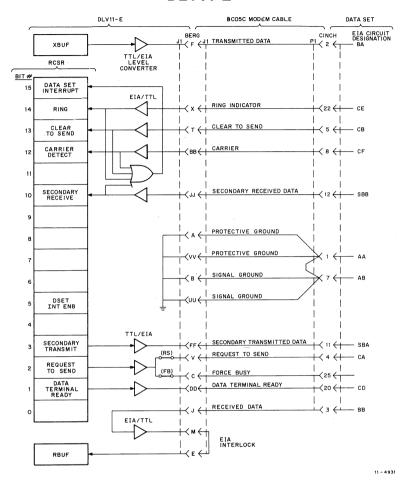

DLV11-E

The DLV11-E is an asynchronous line interface module that interconnects the LSI-11 bus to standard serial communications lines. The module receives serial data, converts it to parallel data, and transfers it to the LSI-11 bus. Also, it accepts parallel data from the LSI-11 bus, converts it to serial data, and transmits it to the peripheral device. The module has jumper-selectable or software-selectable baud rates (50-19,200), and jumper-selectable data bit formats. The DLV11-E offers full modem control for EIA/

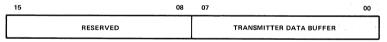

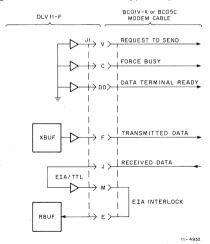

DLV11-F

The DLV11-F is an asynchronous line interface module that interconnects the LSI-11 bus to several types of standard serial communications lines. The module receives serial data, converts it to parallel data, and transfers it to the LSI-11 bus. It also accepts parallel data from the LSI-11 bus, converts it to serial data, and transmits it to

the peripheral device. The module has jumper-selectable or software-selectable baud rates (50-19,200) and jumper-selectable data bits. The DLV11-F supports either 20 mA current loop or EIA standard lines, but does not include modem control.

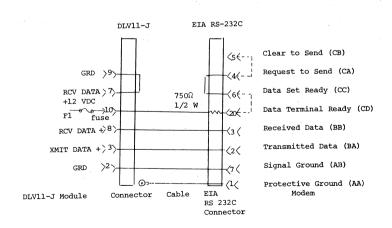

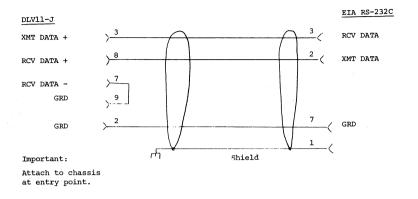

DLV11-J

The DLV11-J contains four independent asynchronous serial line channels used to interface peripheral devices to the LSI-11 bus. Each channel transmits and receives data from the peripheral device over EIA data leads (lines that do not use a control line). The module can be used with 20 mA current loop devices if a DLV11-KA adapter is used. The DLV11-J has jumper-selectable baud rates from 150 to 38.4 K baud.

DUV11

The DUV11 synchronous line interface module establishes a data communication line between the LSI-11 bus and a Bell 201 synchronous modem or equivalent. The module is fully programmable with respect to sync characters, character length (to to 8 bits), and parity selection. The receiver logic accepts serial data for the LSI-11 bus. The transmitter logic converts the parallel LSI-11 bus data into serial data for the transmission line. The interface logic converts the TTL logic levels to the EIA voltage levels required by the Bell 201 modems and also controls the modem for half-duplex or full-duplex operation.

DZV11

The DZV11 is an asynchronous multiplexer interface module that interconnects the LSI-11 bus with up to four asynchronous serial data communications channels. The module provides EIA interface voltage levels and data set control to permit dial-up (auto-answer) options with full-duplex modems such as Bell models 103, 113, 212, or equivalent. The DZV11 does not support half-duplex operations or the secondary transmit and receive operations available in some modems such as Bell 202. The DZV11 has applications in

data concentration and collection systems where front-end systems interface to a host computer and for use in a cluster controller for terminal applications.

### **Peripherals**

LPV11

The LPV11 printer option consists of an interface module, an interface cable, and either an LP05 or LA180 line printer. The interface module provides programmed control of data transfers and provides printer strobe signals appropriate for either printer. The LA180 DECprinter is a high-speed printer that prints 180 characters per second and the LP05 printer can print 240 or 300 lines per minute, depending on which model is selected.

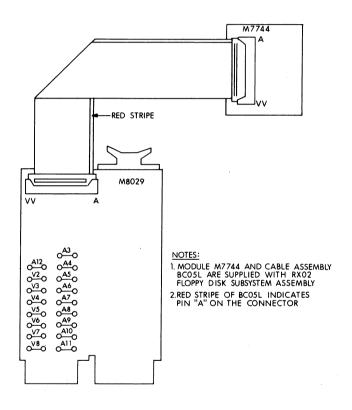

RXV11

The RXV11 option consists of an interface module, cable assembly, and either a single or dual drive RX01 floppy disk. This option is a random access mass storage device that stores data in fixed-length blocks on a preformatted flexible diskette. Each diskette can store and retrieve up to 256K, 8-bit bytes of data. The RXV11 system is rack mountable in the standard 48.3 cm (19 in.) cabinet.

RXV21

The RXV21 floppy disk option is a random access mass memory device that stores data in fixed-length blocks on a preformatted, flexible diskette. Each diskette can store and retrieve up to 512K 8-bit bytes of data. The RXV21 system is rack-mountable and consists of an interface module, an interface cable, and either a single or dual RX02 floppy disk drive. The interface module converts the RX02 I/O bus to the LSI-11 bus structure. It controls the RX02 interrupts to the processor, decodes device addresses for register selection, and handles the data interchange between the RX02 and the processor via DMA transfers. Power for the interface module is supplied by the LSI-11 bus.

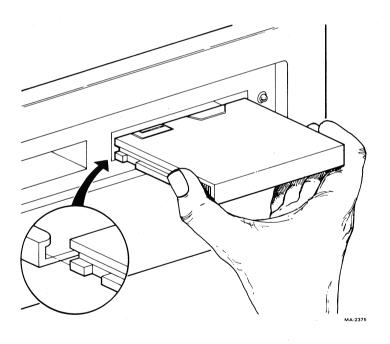

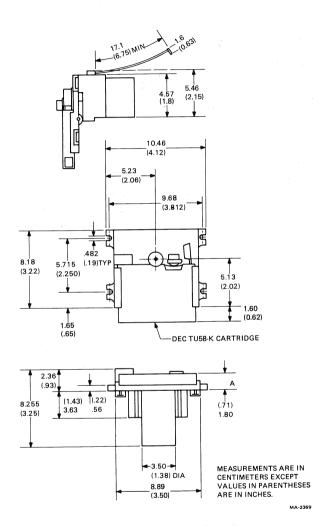

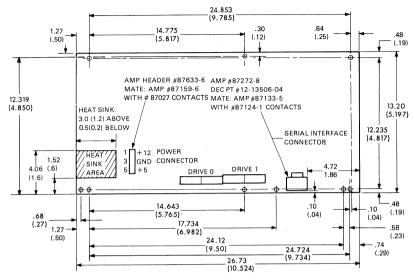

**TU58**

The TU58 is a low-cost intelligent mass memory device that offers random access to block-formatted data on pocket-size cartridge media. It is ideal as inexpensive archive mass storage or as a software update distribution medium. A dual drive TU58 offers 512 Kb of storage space, making it one of the lowest cost complete mass storage subsystems available. For mounting flexibility, the TU58 is offered both as a component level subsystem and as a fully powered 5½″ rackmount subsystem.

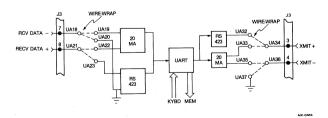

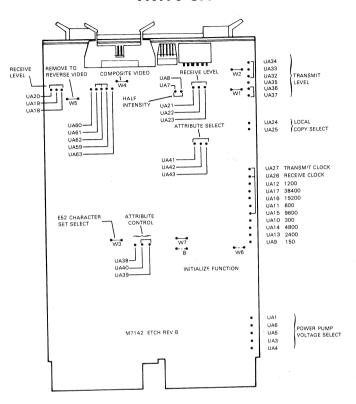

VK170-CA

The VK170 module forms an integral part of a terminal. The module accepts serial ASCII encoded data to be stored in a refresh memory to generate a display for a video monitor. The VK170 also accepts parallel data from a keyboard (on strobe demand) to generate serial ASCII output. The VK170 is an extended-length, double-height board. Mounting holes are provided for stand-off mounting via handle rivets and two holes located near the module fingers.

### **Backplanes**

The following backplane options are available for the LSI-11 bus:

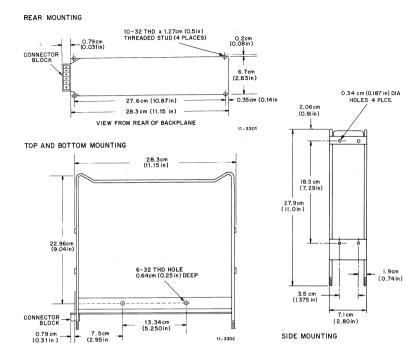

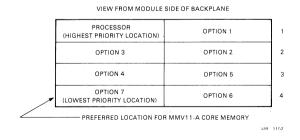

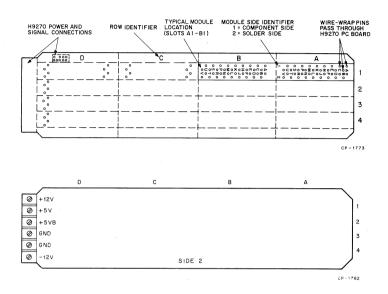

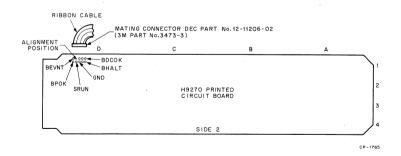

H9270

A 4  $\times$  4 (four rows of four slots each) backplane with card guide assembly. LSI-11 bus in rows A-B and C-D. Accepts 8 double-height modules or 4 quad-height modules or combinations of both.

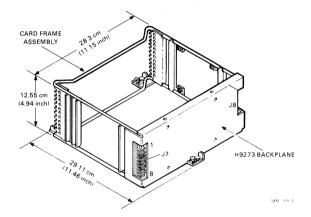

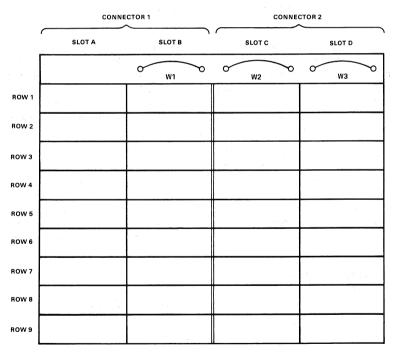

H9273-A

A 9  $\times$  4 (nine rows of four slots each) backplane with card guide assembly. LSI-11 bus in rows A-B only. Special interconnect bus in rows C-D. Accepts double-height or quad-height modules.

H9275-A

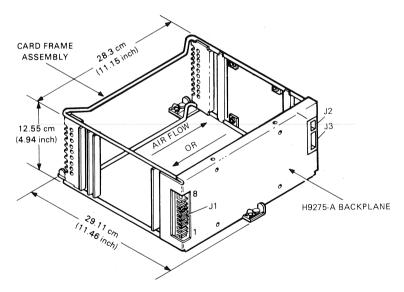

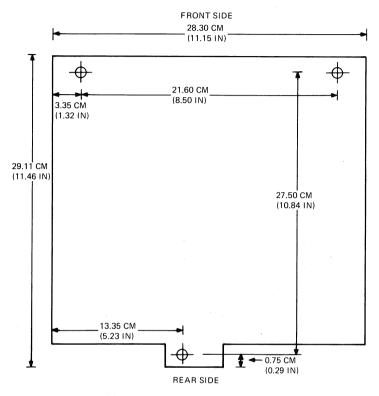

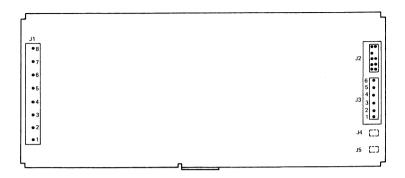

A 9  $\times$  4 (nine rows of four slots each) backplane with card guide assembly. LSI-11 bus in rows A-B and C-D. Accepts up to 18 dual-height modules or nine quad-height modules or a mixture of both. Supports 4 megabyte (22-bit) addressing capability.

H9276

A 9  $\times$  4 (nine rows of four slots each) backplane. Extended LSI-11 bus in rows A-B. C-D rows are

special interconnect bus rows. Accepts both double- and quad-height LSI-11 modules for use in a 22-bit addressing system. Can be used as a mounting box or as an expander box.

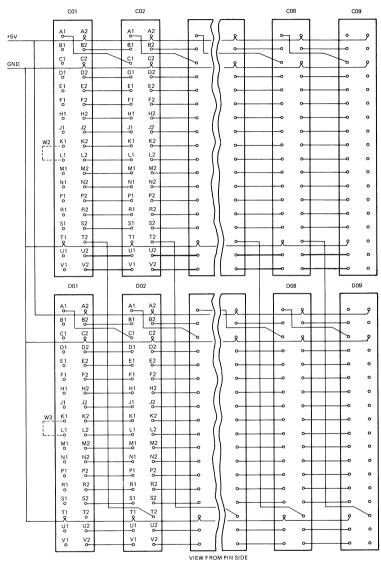

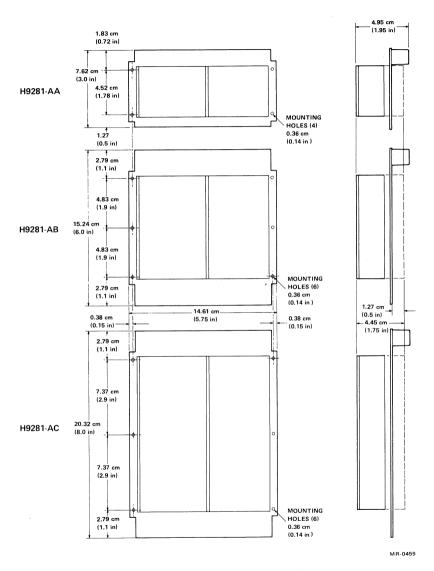

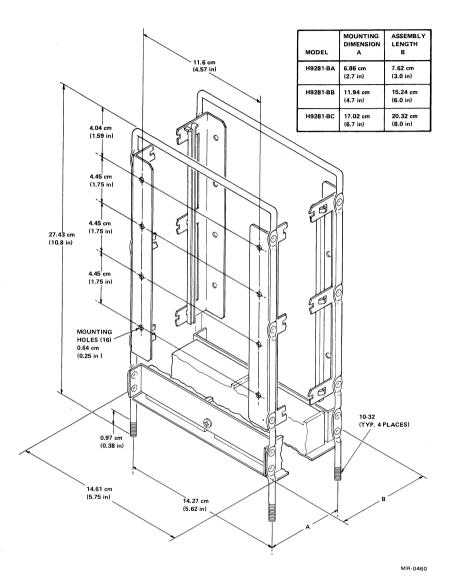

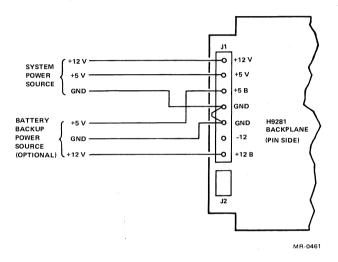

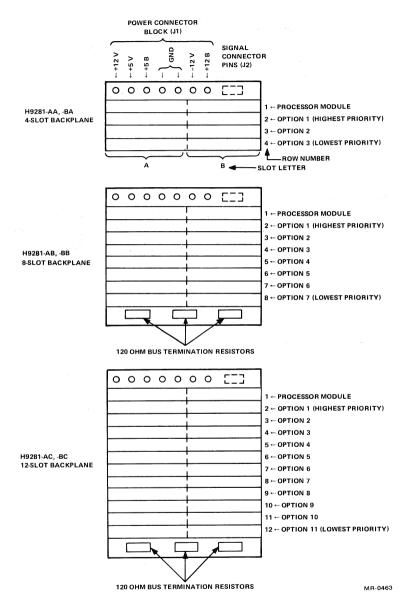

H9281

A 2-slot backplane available in 4-, 8-, or 12-slot options. Accepts double-height modules only.

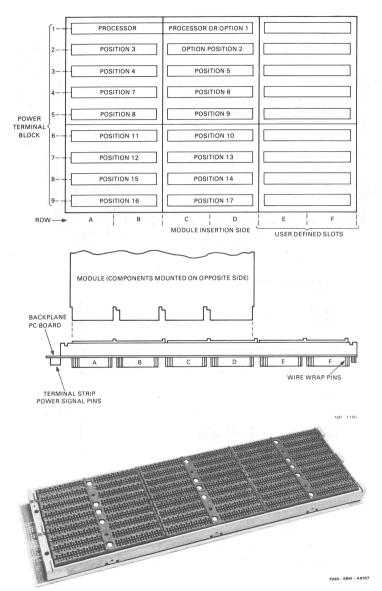

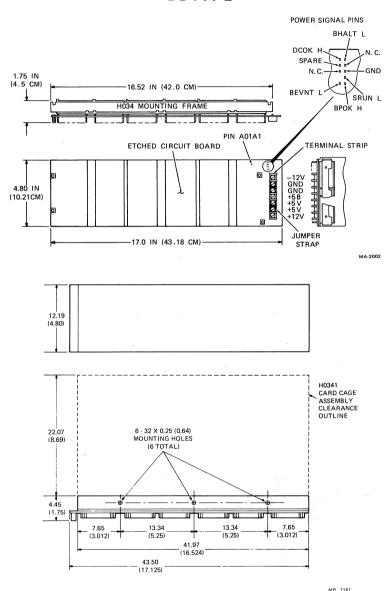

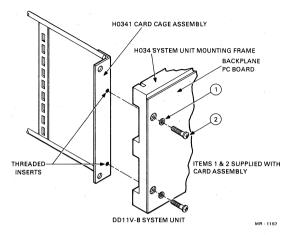

DDV11-B

A 9  $\times$  6 (nine rows of six slots each) backplane. LSI-11 bus in rows A-B and C-D. Rows E-F are unbussed except for + 5V and ground. Accepts 18 double-height or 9 quad-height modules or combinations of both.

### **Enclosures**

H909-C

A 13.3 cm (5.25 in) high, 48.3 cm (19 in) wide enclosure which can be mounted in a 48.3 cm (19 in) rack or as a stand-alone. Accommodates the DDV11-B backplane or a 9  $\times$  6 system mounting unit or houses non-standard mounting arrangement. Includes cooling fan, cord guide, cable restraints, front bezel, and connector block.

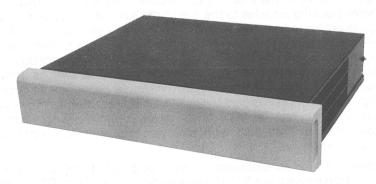

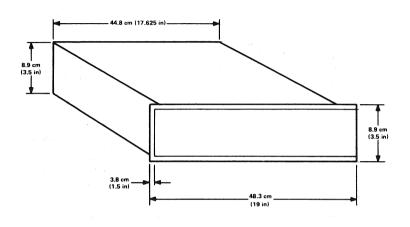

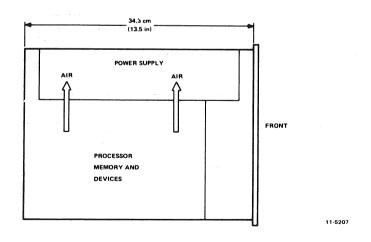

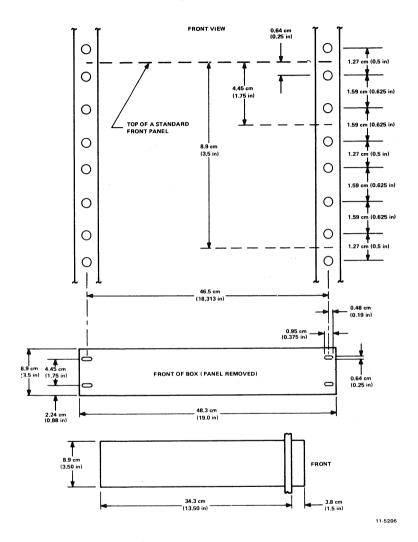

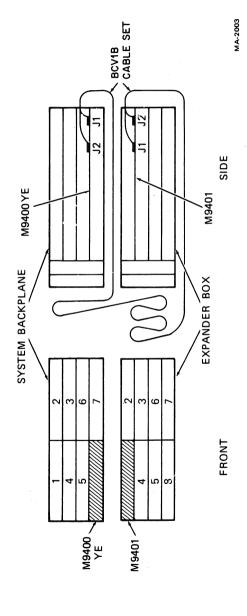

**BA11-M**

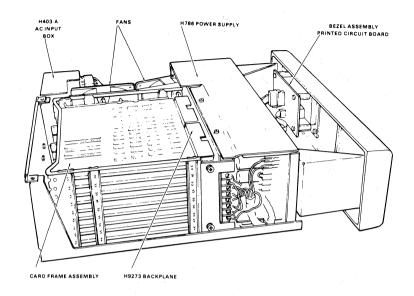

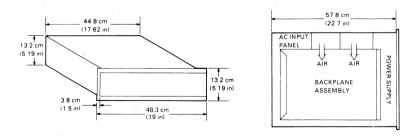

A 8.9 cm (3.5 in) high, 48.3 cm (19 in) wide expansion box which can be mounted in 48.3 cm (19 in) rack. Includes H9270 backplane, H780 power supply, blank front panel or bezel, and cooling fan.

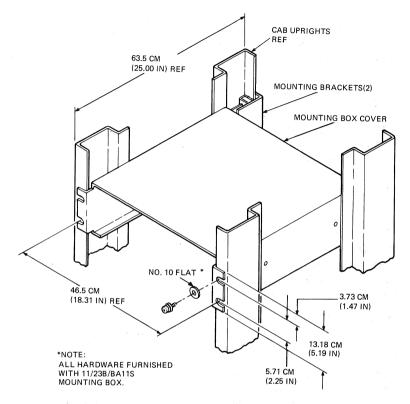

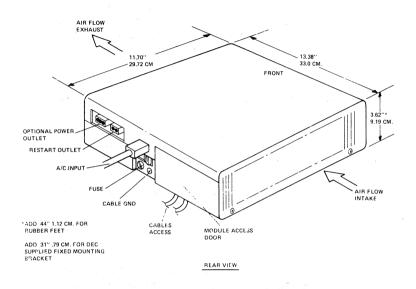

**BA11-N**

A 13.2 cm (5.19 in) high, 48.3 cm (19 in) wide mounting box which can be mounted in a 48.3 cm (19 in) rack. Includes H9273-A backplane, H786 power supply, H403-A ac input panel, blank front panel or bezel, and cooling fan.

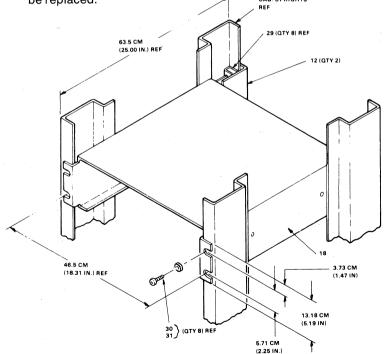

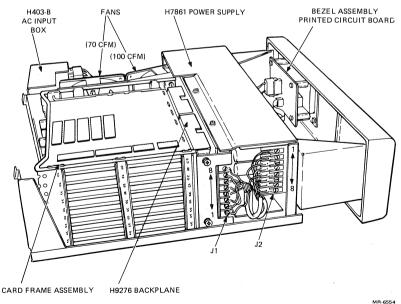

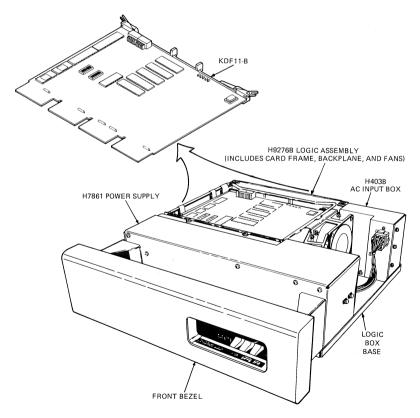

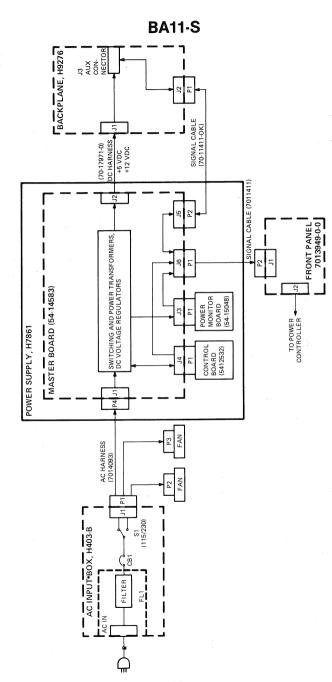

**BA11-S**

A 13.2 cm (5.19 in) high, 48.3 cm (19 in) wide mounting or expander box. It can be installed in a standard 48.3 cm (19 in) rack. Includes H9276 backplane, H7861 power supply, H403-B ac input box, a blank front bezel or bezel assembly with switches and indicators, and two cooling fans.

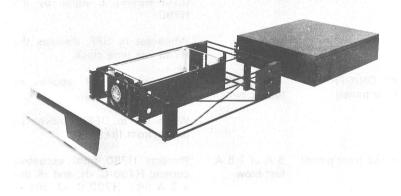

BA11-VA

The BA11-VA is a small form-factor package providing mounting space and power for four LSI-11/2 or LSI-11/23 family modules. This package, plus the high functionality of DIGITAL's microcomputer products, allows LSI-11 microcomputer applications to be implemented within a space smaller than that required for many 8-bit systems.

### **Power Supplies**

H780

Provides  $+5V \pm 4\%$ , 18 A (max) and  $+12V \pm 3\%$ , 3.5 A (max) at 110 Vac and features line-time clock, and power-fail/automatic restart. Available primary power of 115 or 230 Vac and with or without master and slave console

### **Cables and Connectors**

Various preassembled cables in different lengths are available for use with interface and communications options. See Appendix E for commonly used cables.

### **Wire-Wrappable Modules**

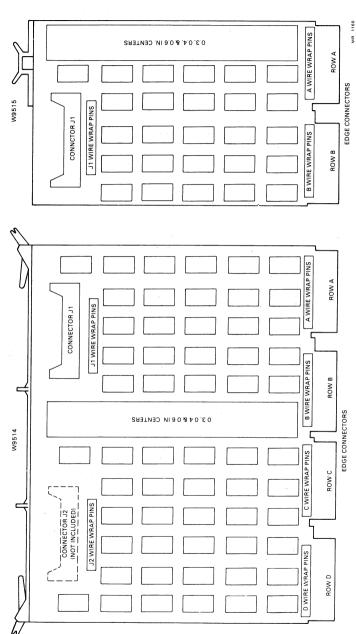

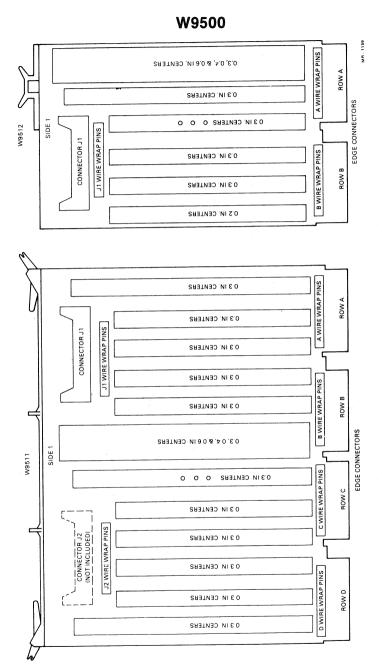

W9500 Series: LSI-11 Bus-Compatible Wire-Wrappable Modules (W9511, W9512, W9514 AND W9515) — The LSI-11 bus-compatible wire-wrappable modules consist of quad-height and double-height modules. Two LSI-11 bus-compatible modules are available without DIP sockets.

W9511

Quad-height, extended-length, single-width module with extractor handle. No DIP sockets included. One 40-pin male cable connector premounted on board and space for additional 40-pin connector provided.

Power and ground connections are  $V_{\mbox{\tiny CC}}$  —

BA2, CA2, DA2

GND —AT1, BT1, CT1, DT1, AC2, BC2, CC2,

DC2

W9514

Same as W9511 except with 58 pre-mounted DIP sockets

Power and ground connections are the

same as W9511

W9512 Double-height, extended-length, single-

width module with Flip-Chip handle. No DIP sockets included. One 40-pin male con-

nector premounted on board.

Power and ground connections are

GND-AT1, BT1,AC2, BC2

W9515 Same as W9512 except with 25 pre-mount-

ed DIP sockets.

Power and ground connections are the

same as W9512

### **Integrated Circuits**

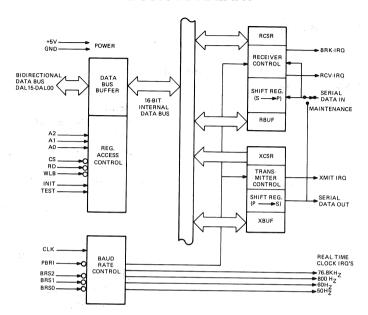

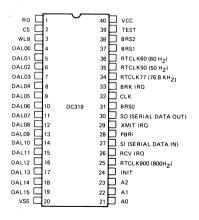

DC319-AA DLART The DC319-AA DLART is a DL-compatible, asynchronous receiver/transmitter designed for data communications with Digital's microprocessor family. Programmed by the CPU to operate either in 8-bit or 16-bit mode with asynchronous baud rates ranging from 300 to 38.4K, the DLART accepts data characters from the CPU in parallel format and converts them into a continuous serial data stream for transmission. Simultaneously, the DLART can receive serial data streams and convert them into parallel data characters for the CPU

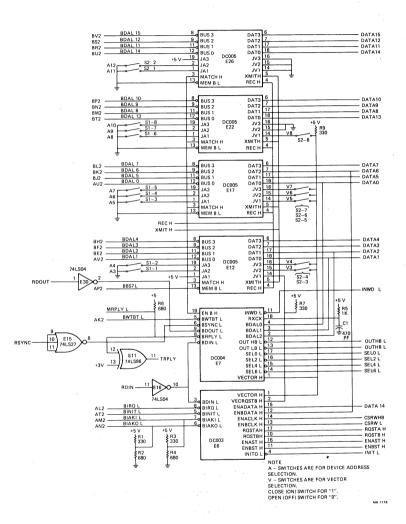

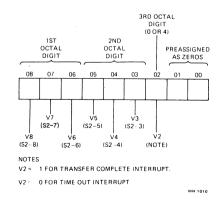

DCK11-AA, -AC

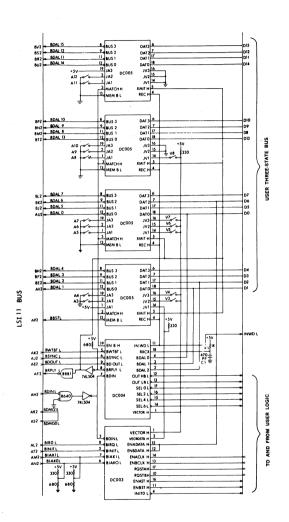

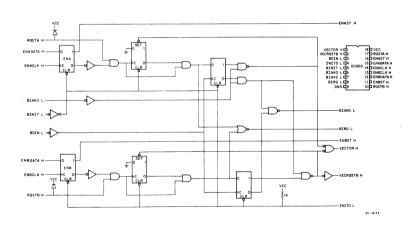

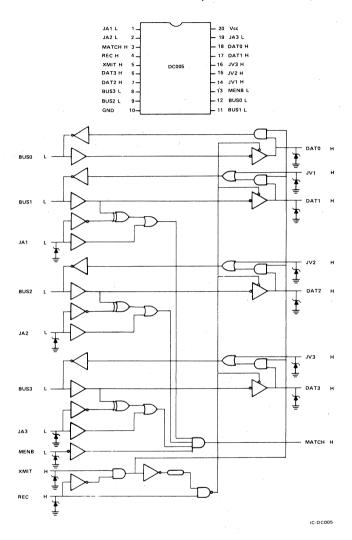

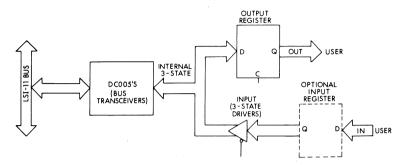

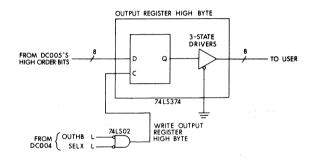

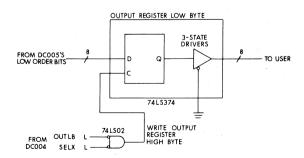

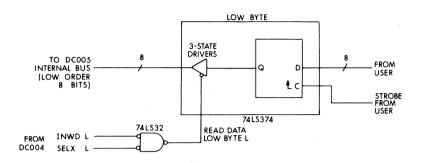

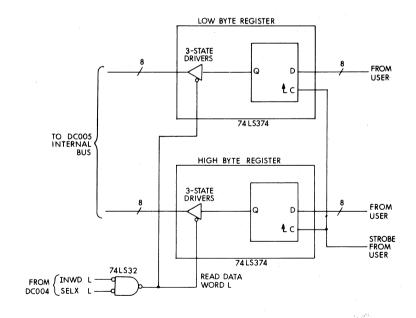

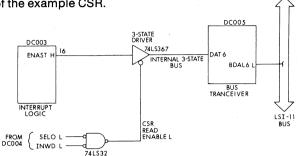

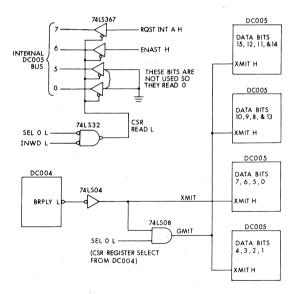

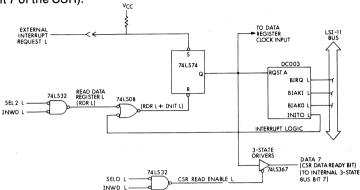

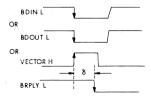

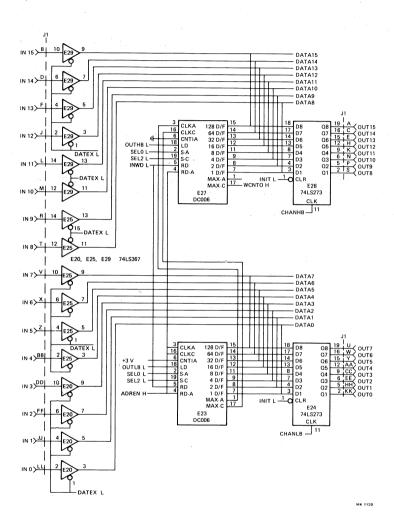

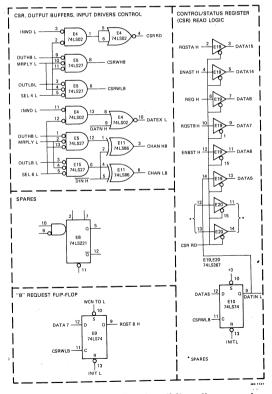

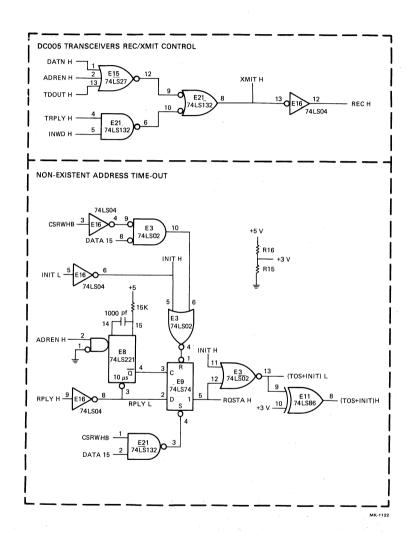

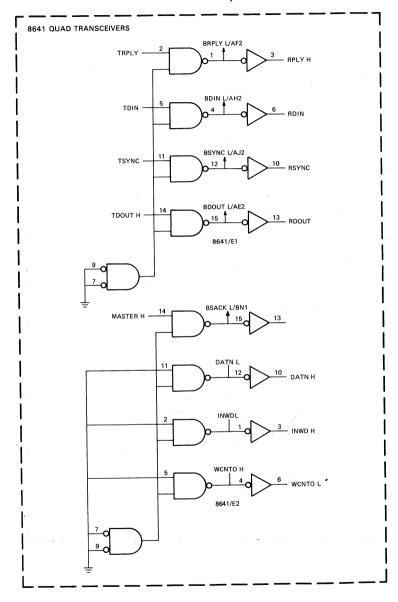

The DCK11-AA and -AC CHIPKITs provide the logic necessary for a program transfer interface to the LSI-11 bus. The DCK11-AA kit contains one DC003 Interrupt Chip, one DC004 Protocol Chip, and four DC005 Transceiver/Address Decoder/Vector Select Chips. The DCK11-AC kit contains previous chips plus one W9512 doubleheight, extended length, high-density wire-wrappable module and one BC07D-10 ten-foot, 40-connector plug-in cable.

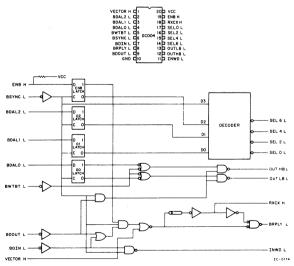

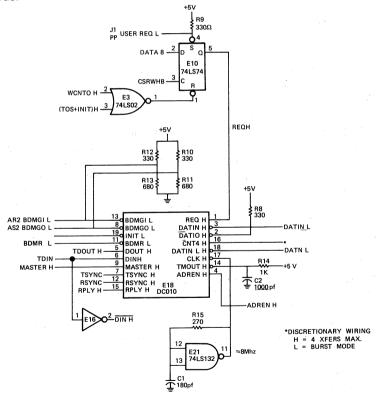

DCK11-AB, -AD

The DCK11-AB and -AD CHIPKITs provide the logic necessary for a Direct Memory Access (DMA) interface to the LSI-11 bus.

The DCK11-AB kit contains one DC003 Interrupt Chip, one DC004 Protocol Chip, four DC005 Transceiver/Address Decoder/Vector Select Chips, two DC006 Word Count/Bus Address Chips, and one DC010 DMA Control Chip. The DCK11-AD kit contains the previous chips plus one W9512 double-height, extended-length, high-density wire-wrappable module and one BC07D-10 ten-foot, 40-connector plug-in cable. DMA applications use the same chips as program control interfaces, plus two DC006s for word or byte address counters and a DC010 DMA bus control IC.

### **Miscellaneous Options**

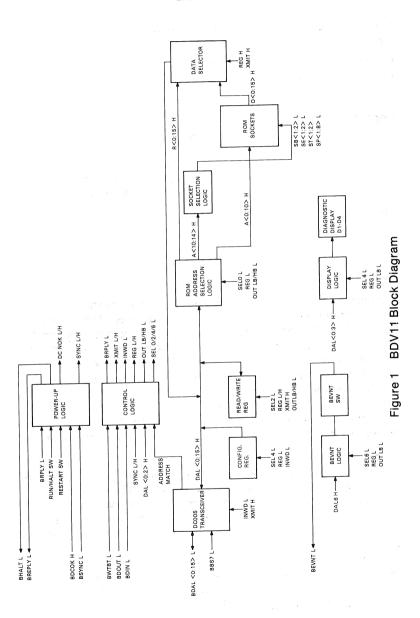

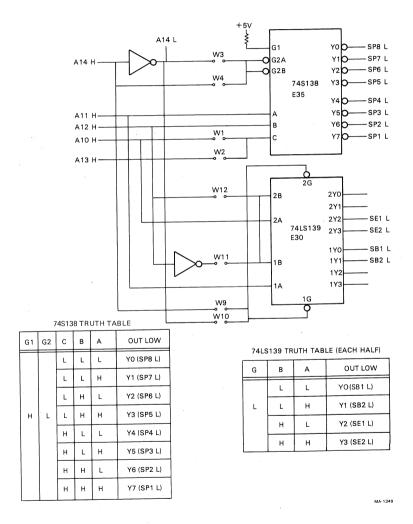

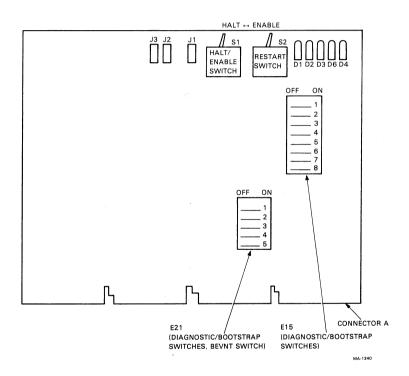

BDV11

The BDV11 module has 2K words of read-only memory (ROM) that contains diagnostic and bootstrap programs. These programs are user-selectable by setting dip switches. The diagnostic programs will test the processor, the memory, and the user's console. The bootstrap programs can boot most LSI-11 peripheral devices. The module also has 120-ohm bus terminator circuits.

The user can add up to 16K of read-only memory (ROM) and up to 2K words of erasable programmable ROM (EPROM) on the module. This 18K words of additional memory can be used with no increase in the amount of I/O address space.

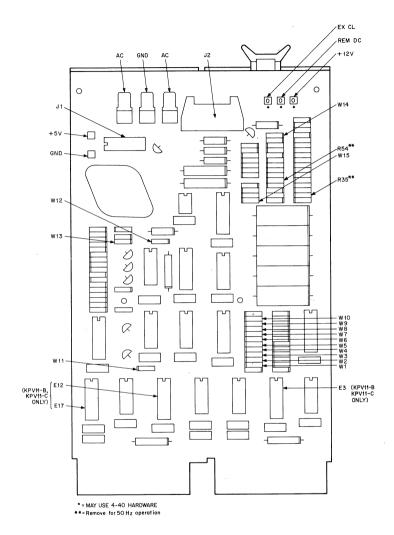

KPV11-A, -B, -C

The KPV11-A module generates power-up and power-down sequences, monitors for a power-fail condition, and generates the line-time clock (LTC) function. The KPV11-B is the same as the "A" except that it provides 120-ohm termination circuits. The KPV11-C is the same as the "A" except that it provides 220-ohm termination circuits. The module can be installed on any back-plane or remotely installed via an optional cable.

REV11-A, -C

The REV11-C module has a bootstrap ROM and direct memory access (DMA) refresh circuits. The REV11-A is identical to the REV11-C except it has additional 120-ohm termination circuits.

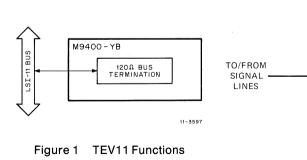

TEV11

The TEV11 is a bus terminator module that provides 120-ohm bus termination circuits.

DLV11

The DMV11 is a microprocessor-controlled communications interface that permits Direct Memory Access (DMA) data transfers. The controller converts parallel data from the LSI-11 bus to serial data for line transmission and serial data from the the line to parallel data for the LSI-11 bus. The serial data is transferred synchronously over private or leased telephone lines or through shielded cables for local operation. The controller performs the detailed protocol operations, including character and message synchronization, header and message formatting, error checking, and transmission control.

DPV11-DA

The DPV11-DA is an single-line, program-controlled, double-buffered communication device designed to interface the LSI-11 bus to high-speed serial synchronous lines for use in many commercial, industrial, and scientific applications, such as remote batch, remote data collection, remote concentration and communication networking. The self-contained DPV11-DA can handle a wide variety of protocols.

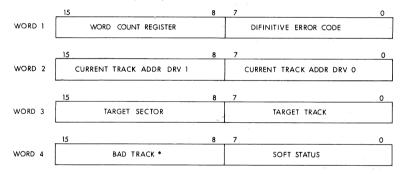

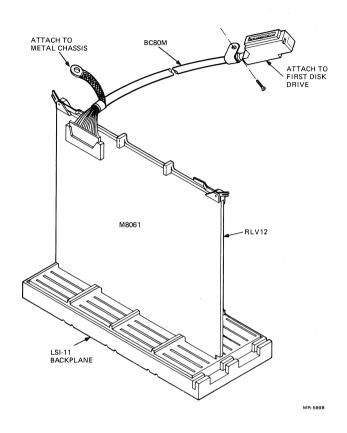

RLV12

The RLV12 disk controller interfaces RL01 and RL02 disk drives to any quad- or hex-size backplane that uses a 16-, 18-, or 22-bit LSI-11 bus. One RLV12 can control up to four RL01 and RL02 disk drives, in any combination. The RLV12 has LSI-11 bus transceivers and decoders, programmable registers, controller timing and sequence logic, and data formatting circuits to read and write on the disk.

Table 1 Module Specifications

| Option  | Module |                                                                                                           | Power Requirements | irements    | Bus Loads* |     |        |   |

|---------|--------|-----------------------------------------------------------------------------------------------------------|--------------------|-------------|------------|-----|--------|---|

| Desig.  | No(s). | Description                                                                                               | +5V<br>⊹5%         | +12V<br>+3% | AC(Max)    | 2   | Size   |   |

| AAV11-A | A6001  | 4-channel, 12-bit<br>D/A converter                                                                        | 1.5 A              | 0.4 A       | 1.9        | -   | Quad   | 1 |

| AAV11-C | A6006  | 4-channel, 12-bit<br>D/A converter                                                                        | 2.0 A              | 1           | 6.0        | 1.0 | Double |   |

| ADV11-A | A012   | 16-channel, 12-bit<br>A/D converter                                                                       | 20. A              | 0.45 A      | 3.25       | ·   | Quad   |   |

| ADV11-C | A8000  | 16 single-ended or 8<br>differential A/D channels,<br>12-bit                                              | 1.5 A              |             | 1.3        | 1.0 | Donble |   |

| AXV11-C | A0026  | Analog I/O board<br>16 single-ended analog<br>input channels, 12-bits<br>2 D/A output, 12-bit<br>channels | 1.5 A              | 1           | <u>.</u> . | 1.0 | Double |   |

| BDV11   | M8012  | Bootstrap,<br>terminator,<br>diagnostic                                                                   | 1.6 A              | 0.07 A      | 2.0        | -   | Quad   |   |

| DDV11-B |        | 6 X 9 backplane                                                                                           |                    |             | 6.4        | 0   | - 1    |   |

|         |        |                                                                                                           |                    |             |            |     |        |   |

\* These ac load figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

Table 1 Module Specifications (cont.)

|                  |                 |                                       |                    | modelic opcomoduous (cont.) |            |          |        |

|------------------|-----------------|---------------------------------------|--------------------|-----------------------------|------------|----------|--------|

| Option<br>Desig. | Module<br>No(s) | Description                           | Power Requirements | ements<br>+12V              | Bus Loads* |          |        |

|                  |                 |                                       | ±2%                | +3%                         | AC(Max)    | DC<br>DC | Size   |

| DLV11            | M7940           | Asynchronous serial<br>line interface | 1.0 A              | 0.18 A                      | 2.5        | -        | Double |

| DLV11-E          | M8017           | Asynchronous line interface           | 1.0 A              | 0.18 A                      | 9.1        | -        | Double |

| DLV11-F          | M8028           | Asynchronous line interface           | 1.0 A              | 0.18 A                      | 2.2        | _ 1      | Double |

| DLV11-J          | M8043           | 4 asynchronous<br>serial interfaces   | 1.0 A              | 0.25 A                      | -          | -        | Double |

| DPV11            | M8020           | Synchronous<br>serial line interface  | 1.2 A              | 0.30 A                      | 1.0        | 0.0      | Double |

| DMV11            |                 | Synchronous<br>line controller        | 4.7 A              | 0.38 A                      | 5.0        | 0.1      | Quad   |

| DRV11            | M7941           | Parallel line unit<br>interface       | 0.9 A              | 1                           | 4.1        | -        | Double |

| DRV11-B          | M7950           | DMA interface                         | 1.9 A              | 1                           | 3.3        | _        | Quad   |

| DRV11-J          | M8049           | 64-line parallel I/O                  | 1.6 A              | 1.8 A                       | 5.0        | _        | Double |

| DRV11-P          | M7948           | Foundation                            | 1.0 A              | 1                           | 2.1        | _        | Quad   |

| *1               |                 | module                                | + user logic       |                             |            |          |        |

\* These ac load figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

Double

2.4

Quad

2.4

0.8 A

1.8 A

Interface LSI-11 CPU

M7264

**AD11-F**

4K RAM

0.8 A

2 X 12 backplane

nstrument bus

M7954

H9281C IBV11-A

2 X 8 backplane

ဗ္ဗ **Bus Loads\*** AC(Max) 9. 3.95 10.0 2.6 <del>د</del>. Module Specifications (cont.) **Power Requirements** +12V %€∺ 0.32 0.39 0.86 A 1.15 A **+2**% +5 ı Synchronous serial Table 1 2 X 4 backplane 4 X 4 backplane 4 X 9 backplane 4 X 9 backplane 4 X 9 backplane Asynchronous ine interface ine interface Description Module M7951 M7957 No(s).

Quad

Size

Quad

\* These ac load figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

H9276

H9281A H9281B

H9275-A

H9273

H9270

Option

Desig.

DUV11

DZV11

Table 1 Module Specifications (cont.)

|                  |                  | lable I Mo                                                               | dule Specifi                   | Module Specifications (cont.) |            |              |        |

|------------------|------------------|--------------------------------------------------------------------------|--------------------------------|-------------------------------|------------|--------------|--------|

| Option<br>Desig. | Module<br>No(s). | Description                                                              | Power Requirements<br>+5V +12V | irements<br>+12V              | Bus Loads* | j. T         |        |

|                  | ,                | •                                                                        | ÷2%                            | +3%                           | AC(Max)    | 20           | Size   |

| КD11-Н           | M7264-YA         | LSI-11 CPU<br>without RAM                                                | 1.6 A                          | 0.25                          | 2.4        | -            | Quad   |

| KD11-HA          | M7270            | LSI-11/2 CPU                                                             | 1.0 A                          | 0.22 A                        | 1.7        | -            | Double |

| KDF-11           | M8186            | LSI-11/23 CPU                                                            | 2.0 A                          | 0.2 A                         | 2.0        | -            | Double |

| KPV11-A          | M8016            | Power-fail/line-<br>time clock                                           | 0.56 A                         | 1                             | 1.63       | -            | Double |

| KPV11-B          | M8016-YB         | Power-fail/line-<br>time clock/120 \( \text{\Omega} \)<br>bus terminator | 0.56                           | 1                             | 1.63       | <del>-</del> | Double |

| KPV11-C          | M8016-YC         | Power-fail/line-<br>time clock/220 \( \text{\alpha}\)<br>bus terminator  | 0.56 A                         | I                             | 1.63       | <del>-</del> | Double |

| KUV-11           | M8018            | WCS module                                                               | 3.0 A                          |                               |            | -            | Quad   |

| KWV11-A          | M7952            | Programmable real-time clock                                             | 1.75 A                         | 0.01 A                        | 3.4        | -            | Quad   |

| KWV11-C          | A4002            | Programmable real-time clock                                             | 1.75 A                         | 0.1 A                         | 1.0        | 1.0          | Double |

|                  |                  |                                                                          |                                |                               |            |              |        |

\* These ac load figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

|                  |                  | Table 1                                                      | Module Speci             | Table 1 Module Specifications (cont.)     | E)         |   |          |

|------------------|------------------|--------------------------------------------------------------|--------------------------|-------------------------------------------|------------|---|----------|

| Option<br>Desig. | Module<br>No(s). | Description                                                  | Power Red<br>+5V<br>+50% | Power Requirements<br>+5V +12V<br>+5% +2% | Bus Loads* | ړ | <u>0</u> |

|                  |                  |                                                              | 0/ <b>5</b>              | 0. <b>2</b> −                             | AC(INIAA)  | 3 | OIFC     |

| LPV11            | M8027            | LA180/LP05<br>printer interface                              | 0.8 A                    | i<br>I                                    | 1.4        | - | Double   |

| MRV11-AA         | M7942            | 4K X 16 read-only                                            | 0.4 AA                   | ı                                         | 1.8        | - | Double   |

|                  |                  | memory (less<br>PROM intergrated<br>circuits)                |                          |                                           |            |   |          |

|                  |                  | (with 32 512 X 4 PROM integrated circuits) (MRV11-AC)        | 2.8 A                    |                                           |            |   |          |

| MRV11-BA         | M8021            | UV PROM-<br>RAM (less PROM<br>integrated circuits            | 0.58 A                   | 0.34 A                                    | 2.8        | - | Double   |

|                  |                  | (with 8 1K X 8<br>PROM integrated<br>circuits)<br>(MRV11-BC) | 0.62 A                   | 0.5 A                                     |            |   |          |

\* These ac load figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

Table 1 Module Specifications (cont.)

|                  |                  | I ADIC I MO                                                  | יווים לה בוחוי                 | Module opecifications (colif.) |            |     |        |

|------------------|------------------|--------------------------------------------------------------|--------------------------------|--------------------------------|------------|-----|--------|

| Option<br>Desig. | Module<br>No(s). | Description                                                  | Power Requirements<br>+5V +12V | irements<br>+12V               | Bus Loads* |     |        |

|                  |                  |                                                              | <b>∓2</b> %                    | <b>∓3</b> %                    | AC(Max)    | ည   | Size   |

| MRV11-C          | M8048            | PROM/ROM module                                              | 0.8 A                          |                                | 2.0        | -   | Double |

| MSV11-B          | M7944            | 4K X 16 read/write<br>MOS memory                             | 0.6 A                          | 0.54 A                         | 6.1        | -   | Double |

| MSV11-CD         | M7955-YD         | 16K X 16 read/write<br>MOS memory                            | 1.1 A                          | 0.54 A                         | 2.3        | -   | Quad   |

| MSV11-D          | M8044            | 4K/16K/32K<br>MOS memory                                     | 1.7 A                          | 0.34 A                         | 2.0        | -   | Double |

| MSV11-E          | M8045            | 4K/16/32K<br>MOS memory                                      | 2.0 A                          | 0.41 A                         | 2.0        | -   | Double |

| MXV11-A          | M8047            | Multifunction module                                         | 1.2 A                          | 0.1 A                          | 2.0        | 7   | Double |

| REV11-A          | M9400-YA         | 120 \( \Omega\) terminator,<br>DMA refresh,<br>bootstrap ROM | 1.6 A                          | I                              | 2.2        | -   | Double |

| REV11-C          | M9400-YC         | DMA refresh,<br>bootstrap                                    | 1.6 A                          | 1                              | 2.2        | - 1 | Double |

<sup>\*</sup> These ac load figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

|                  |                  | Table 1 Mo                         | dule Specific                             | Table 1 Module Specifications (cont.) |            |      |        |

|------------------|------------------|------------------------------------|-------------------------------------------|---------------------------------------|------------|------|--------|

| Option<br>Desig. | Module<br>No(s). | Description                        | Power Requirements<br>+5V +12V<br>±5% ±3% | ements<br>+12V<br>±3%                 | Bus Loads* | DC C | Size   |

| RLV12            | M8061            | Disk controller                    | 5.0 A                                     | 0.1 A                                 | 3.0        | 1.0  | Quad   |

| RXV11            | M7946            | RX01 interface                     | 1.5 A                                     | 1                                     | 1.8        | -    | Double |

| RXV21            | N8029            | Double density<br>floppy interface | 1.1 A                                     |                                       | 5.0        | -    | Double |

| TEV11            | M9400-YB         | 120 \text{\alpha} terminator       | 0.5 A                                     | - 1                                   | 0          | 0    | Double |

| TU58             |                  | Serial/cartridge<br>cassette       | 0.75<br>Appr.                             | 1.2 A max                             |            |      |        |

| VK170            | CAM7142          | Serial video module                | 1.2 A                                     | 0.15                                  |            |      | Double |

load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in \* These ac load figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac the manufacturing of the product.

### CONFIGURATION

The LSI-11 bus permits a unified addressing structure in which control/status and data registers for peripheral devices are directly addressed as memory locations. All operations on these registers, such as transferring information to or from them or manipulating data within them, are performed by normal memory address instructions. The use of memory address instructions on peripheral device registers greatly increases the flexibility of input/output communications.

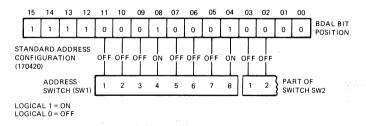

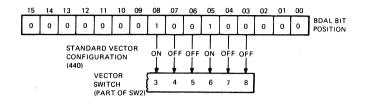

### **Addresses**

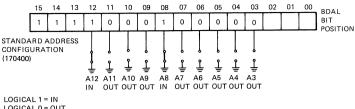

All the options except memories have at least one control and status register and may have several data registers. Each register is assigned an address through which the option can communicate with the processor. The upper 4K of memory address space is reserved for the processor and external input/output (I/O) registers. The user can select any address (Appendix A) in the range of 160000 through 177776 and assign it to the option interface module. The modules are configured to the desired address by selecting dip switches, connecting or disconnecting wire-wrap pins, or installing or removing wired jumpers on the module.

part2

the

interfaces

## **ΔΔV11-Δ**

### AAV11-A 4-CHANNEL 12-BIT D/A CONVERTER

#### INTRODUCTION

The AAV11-A is a four-channel, digital-to-analog converter module that includes control and interfacing circuits. It has four D/A converters, a dc-to-dc converter that provides power to the analog circuits, and a precision voltage reference. Each channel has its own holding register that can be addressed separately and provides 12 bits of resolution. These registers can be written and read, using either word or byte format. In addition, bits 0, 1, 2, and 3 of the fourth holding register are brought out to the I/O connector, so they can be used as a fourbit digital output register.

#### **FEATURES**

- Four 12-bit digital input channels, binary encoded for either unipolar mode or bipolar mode.

- Jumper-selected output ranges and modes: Bipolar mode  $\pm 2.56 \text{ V}, \pm 5.12 \text{ V}, \pm 10.24 \text{ V}$ Unipolar mode 0 to +5.12 V, 0 to +10.24 V

- One part in 4,096 resolution

- 5 V / μs slew rate

- ±5 mA drive capability per converter

#### SPECIFICATIONS

Digital storage

| Identification           | A6001                                           |

|--------------------------|-------------------------------------------------|

| Size                     | Quad                                            |

| Power                    | +5.0 Vdc ±5% at 1.5 A<br>+12.0 Vdc ±3% at 0.4 A |

| Bus loads                |                                                 |

| ac                       | 1.9                                             |

| dc -                     | 1.0                                             |

| Resolution               | 12 bits (1 part in 4,096)                       |

| Number of D/A converters | 4                                               |

| Digital input            | 12 bits (binary-encoded for uni-                |

Read/write, word or byte oper-

polar mode; offset-binary-encod-

able, single-buffered

ed for bipolar mode)

## **ΔΔV11-Δ**

Output voltage range  $\pm 2.56 \text{ V.} \pm 5.12 \text{ V.} \pm 10.24 \text{ V bipo-}$ lar, 0 V to +5.12 V, 0 V to +10.24 (jumper selected)

V unipolar

Adjustable (factory set for bipolar Gain accuracy

±5.12 V)

10 PPM per °C, max. Gain temperature coefficient

20 PPM of full scale range per °C, Offset temperature coefficient

max.

±½ LSB max, nonlinearity Linearity

Differential linearity ±1/2 LSB, monotonic

Output impedance 1 ohm max.

±6 mA max. per converter Drive capability

Slewing speed 5 V/μs

Rise and settling time (to 0.1% of  $4 \mu s$  (8  $\mu s$  wth 5000 pF load in

final value) parallel with 1 k $\Omega$

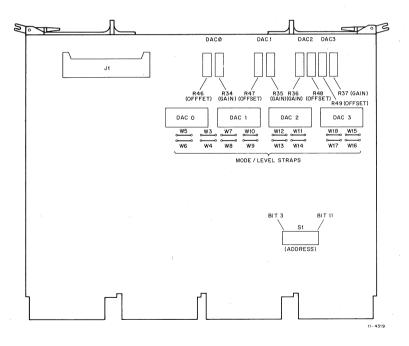

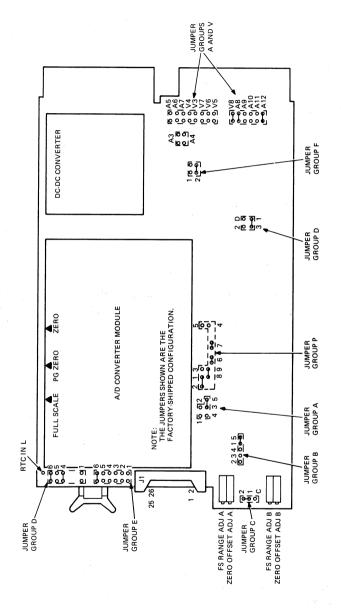

### CONFIGURATION

This section describes how the user can configure the module to function within the system by setting dip switches (Figure 2) to obtain the desired device address. The voltage range for each D/A converter (DAC 0—DAC 3) can be configured independently by installing or removing the designated jumpers (Figure 2) associated with a specific D/A converter. This section also describes how to connect external devices to the module. The standard factory addresses for the registers are listed in Table 1.

Table 1 Standard Addresses

| Register  | Mnemonic | Address |

|-----------|----------|---------|

| Holding 0 | DAC 0    | 170440  |

| Holding 1 | DAC 1    | 170442  |

| Holding 2 | DAC 2    | 170444  |

| Holding 3 | DAC 3    | 170446  |

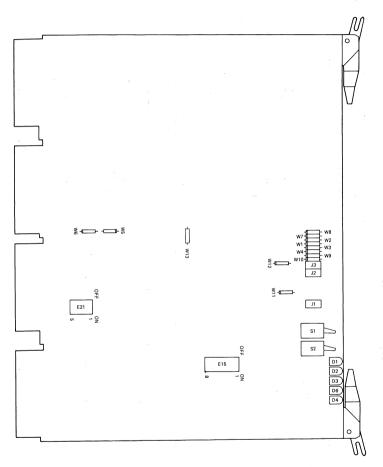

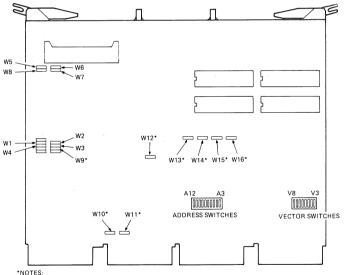

Figure 1 AAV11-A Connectors, Switches, and Jumpers

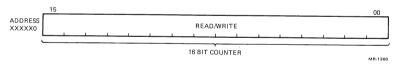

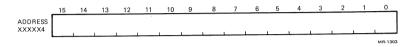

### **Device Registers**

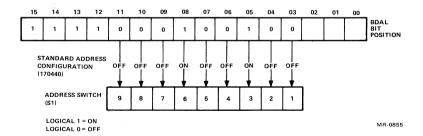

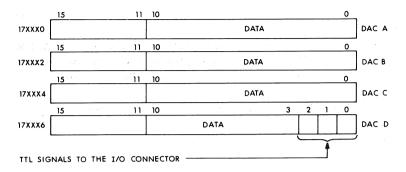

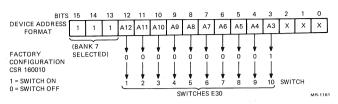

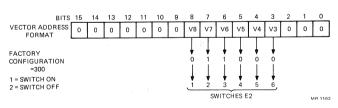

The device registers can be configured to respond to any address within the range 170000 to 177777. Each register address does not have to be individually set. The DAC 0 register address is selectable, and the last digit will be zero. The remaining registers will use addresses 17XXX2, 17XXX4, and 17XXX6 for DAC 1, DAC 2, and DAC 3 registers, respectively. The factory-configured device address is 170440 as shown in Figure 2. The word formats for the DAC registers are described in Table 2. Note that all device registers are always a sequence of four consecutive even locations. There is no vector used for this module.

### D/A Converter Range and Mode

The range and mode (bipolar or unipolar) voltages can be selected by the user inserting or removing jumpers as shown in Figure 1. Four jumpers are associated with each D/A converter. The module is factory-configured for -5.12 to +5.12 V bipolar operation. The jumper configuations for the bipolar mode ranges are shown in Table 3; the unipolar ranges are shown in Table 4.

Figure 2 Address Selection

Table 2 DAC Word Formats

| Bit   | DAC 0, DAC 1, DAC 2 | DAC 3              |

|-------|---------------------|--------------------|

|       |                     | ,                  |

| 15-12 | Not used            | Not used           |

| 11    | Binary 11           | Binary 11          |

| 10    | Binary 10           | Binary 10          |

| 9     | Binary 9            | Binary 9           |

| 8     | Binary 8            | Binary 8           |

| 7     | Binary 7            | Binary 7           |

| 6     | Binary 6            | Binary 5           |

| 5     | Binary 5            | Binary 5           |

| 4     | Binary 4            | Binary 4           |

| 3     | Binary 3            | Binary 3/Control 3 |

| 2     | Binary 2            | Binary 2/Control 2 |

| 1     | Binary 1            | Binary 1/Control 1 |

| Ò     | Binary 0            | Binary 0/Control 0 |

Table 3

Jumper Configurations for Bipolar Operation

|       | ±2.56 V | ±5.12 V | ±10.24 V |

|-------|---------|---------|----------|

| DAC 1 |         |         |          |

| W3    | IN      | IN .    | OUT      |

| W4    | OUT     | OUT     | IN       |

| W5    | IN      | OUT     | OUT      |

| W6    | IN      | IN .    | IN       |

| DAC 2 |         |         |          |

| W7    | IN      | IN s    | OUT      |

| W8    | OUT     | OUT     | IN       |

| W9    | IN      | OUT     | OUT      |

| W10   | IN      | IN      | IN       |

Table 3 Jumper Configurations for Bipolar Operation (Cont)

|       | $\pm 2.56	extsf{V}$ | $\pm 5.12~	extsf{V}$ | ±10.24 V |

|-------|---------------------|----------------------|----------|

| DAC 3 |                     |                      |          |

| W11   | IN                  | IN                   | OUT      |

| W12   | OUT                 | OUT                  | IN       |

| W13   | IN                  | OUT                  | OUT      |

| W14   | IN                  | IN                   | IN       |

| DAC 4 |                     |                      |          |

| W15   | IN                  | IN                   | OUT      |

| W16   | OUT                 | OUT                  | · IN     |

| W17   | IN                  | OUT                  | OUT      |

| W18   | IN                  | IN                   | IN       |

Table 4

Jumper Configurations for Unipolar Operation

| <u></u> | 0 V—+5.12 V | 0 V—+10.24 V |

|---------|-------------|--------------|

| DAC 1   |             |              |

| W3      | IN          | IN           |

| W4      | OUT         | OUT          |

| W5      | IN          | OUT          |

| W6      | OUT         | OUT          |

| DAC 2   |             |              |

| W7      | IN          | IN           |

| W8      | OUT         | OUT          |

| W9      | IN          | OUT          |

| W10     | OUT         | OUT          |

| DAC 3   |             |              |

| W11     | IN          | IN           |

| W12     | OUT         | OUT          |

| W13     | IN          | OUT          |

| W14     | OUT         | OUT          |

|         |             |              |

Table 4 Jumper Configurations for Unipolar Operation (Cont)

|       | 0 V—+5.12 V | 0 V—+10.24 \ |

|-------|-------------|--------------|

| DAC 4 |             |              |

| W15   | IN          | IN           |

| W16   | OUT         | OUT          |

| W17   | IN          | OUT          |

| W18   | OUT         | OUT          |

| VV 10 |             | 001          |

## J1 Output Connections

Analog output devices such as oscilloscopes may be either grounded or floating. If the oscilloscope is grounded, either through its power plug or through contact between its chassis and a grounded cabinet, the oscilloscope ground should not be connected to any of the AAV11-A ground pins. Doing so may result in a ground loop which will adversely affect oscilloscope control results as well as ADV11-A operation (if used). If the oscilloscope is floating, its ground should be connected to the AAV11-A logic ground, J1 pins L, N, R, or T. Note that the foregoing assumes that the LSI-11 powersupply ground is connected to powerline (earth) ground. If continuity checks reveal no such connection, attach a length of 12-gauge wire between the powersupply ground and a convenient point associated with earth ground.

Figure 3 Connection to Oscilloscope with Differential Input

## **AAV11-C ANALOG OUPUT BOARD**

#### INTRODUCTION

The AAV11-C is a dual-height, multi-channel analog output board designed to interface analog instrumentation to the LSI-11 bus. It has four individually addressable digital-to-analog converters (DACs), each with 12 bits of input data resolution. Each DAC can be written or read in either word or byte format. Jumpers permit selection of the analog output voltage range for each register and its operating mode, either unipolar or bipolar. One of the registers, DAC D, also has four digital output bits for creating control signals to an analog device, such as a CRT.

#### **FEATURES**

- 4 D/A converter circuits, separately controlled

- 12-bit digital resolution

- Read/write, word or byte addressable registers

- Unipolar or bipolar output

- Output voltage range selection of ± 10 V or 0 to 10 V

- 4-bit digital output for CRT control signals intensity, blank, unblank, erase

#### **SPECIFICATIONS**

| Identification           | A6006                                                                        |

|--------------------------|------------------------------------------------------------------------------|

| Size                     | Dual-height: 13.16 cm $\times$ 21.6 cm (5.18 in $\times$ 8.5 in)             |

| Power                    | +5.0 V ±5% at 2.5 A                                                          |

| Bus loads<br>AC<br>DC    | 0.9<br>1.0                                                                   |

| D/A Resolution           | 12-bit                                                                       |

| Number of D/A converters | 4                                                                            |

| Digital input            | 12-bits (binary encoded for unipolar output; offset binary for binolar mode) |

Four separate Read/write DAC Digital storage

registers for word or byte stor-

age

±10 V @ 10 mA; Analog Output Voltage

0 V to 10 V @ 10 mA

Adjustable to (-) full-scale value Gain accuracy

±30 PPM per °C, max. Gain drift

Offset drift ± 15 PPM per °C, max.

Offset error Adjustable to zero

Linearity (0-10 V) ± ½ LSB: ± 1.2 mV at full-scale

range

Differential linearity + 1/2 I SB

Output impedance 0.5 ohm

Output current 10 mA @ 10 V min.

Settling time 6us to 0.1% for a 20 V p-p output

change

I/O connector 20 pins; 3M no. 3421-7020

## CONFIGURATION

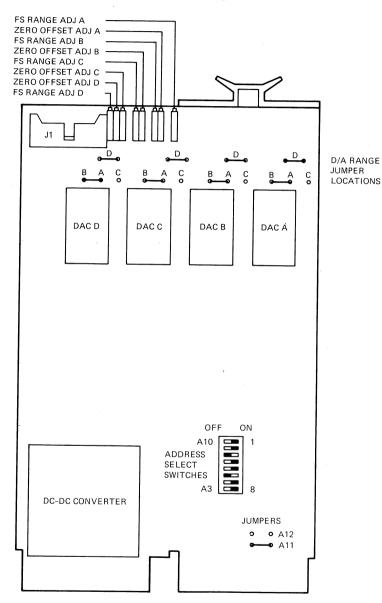

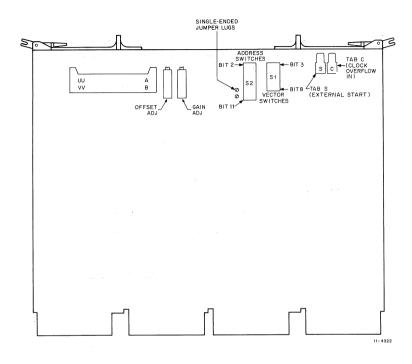

The physical layout of the AAV11-C is shown in Figure 1. The AAV11-C has switches and two jumpers to set up the device address. The board also has jumpers to select the output voltage range for unipolar and bipolar operation. The following paragraph describes in detail the procedure for setting up the circuit board.

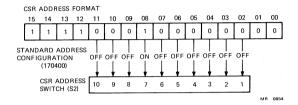

# **Device Select Addressing**

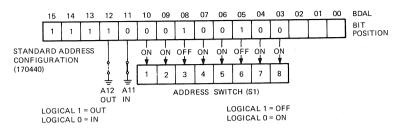

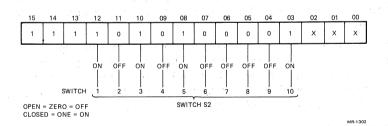

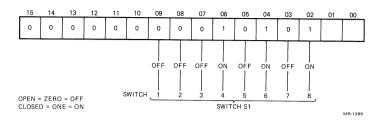

The AAV11-C device address is the I/O address assigned to the first of four DAC registers. The user selects the device address via a switch pack for address bits DAL 3-10 and two jumpers for bits DAL 11 and DAL 12. The device address can range from 160000 to 177770 in increments of 10s. The device address is usually set at 170440s. This is shown in Figure 2. A switch in the ON position represents a 0; a switch in the OFF position represents a 1. Jumper A11 is installed to place a 0 at address bit DAL 11. Jumper A12 is removed to place a 1 at address bit DAL 12.

Figure 1 AAV11-C Physical Layout

Figure 2 Selecting AAV11-C Device Address

## **Output Voltage Range Selection**

Each DAC on the AAV11-C has separate voltage range jumpers. These jumpers are found above their corresponding D/A converter IC on the printed circuit board (See Figure 1). When sent from the factory, the AAV11-C has a voltage range selected for all four DACs of bipolar  $\pm\,10$  V. Table 1 shows the jumpers to install to select the output voltage range. The output of the board can be configured for either straight binary notation for unipolar operation or offset binary notation for bipolar operation. The expected output values are shown in Table 1.

Table 1 AAV11-C Output Voltage Range Jumpers

| Polarity | Output Voltage<br>Range |              | Notation         | Input Code<br>(Octal)                | Output<br>Value                            |

|----------|-------------------------|--------------|------------------|--------------------------------------|--------------------------------------------|

| Unipolar | 0 to +10 V              | A to C       | Binary           | 000000                               | + full scale                               |

| Bipolar  | ± 10 V                  | A to B:<br>D | Offset<br>binary | 007777<br>000000<br>004000<br>007777 | 0 V<br>+ full scale<br>0 V<br>- full scale |

Figure 3 AAV11-C DACs

#### PROGRAMMING

The AAV11-C has four addressable read/write registers. Each register is used by one of four digital-to-analog converters and can be addressed as one word or two bytes, allowing complete use of the LSI-11 instruction set. The AAV11-C device address is the base address of the first register, usually 170440<sub>8</sub>. The other registers are addressed in increments of 2<sub>8</sub> above the base address.

# Interfacing to the AAV11-C

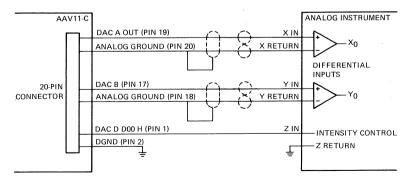

Figure 1 shows the location of the connectors on the AAV11-C. DAC inputs and control signal inputs enter the board via the LSI-11 bus connectors. Analog output voltages and digital control signals leave the board via the top edge connector J1. Table 2 shows the signal names on this connector. Each DAC has one output and a corresponding analog ground pin. The four least significant bits of DAC D (D00, D01, D02, and D03) are used for control signals to an analog device. These four bits are TTL-compatible.

Figure 4 shows how the AAV11-C is connected to a device that uses differential analog inputs and one control input. Both the AAV11-C and the analog device must be set up for electrical compatibility. The device manual should define which pins to attach to the AAV11-C control bits. The software enables or disables the control bits.

Table 2 AAV11-C Connector J1 Pin Assignments

| Pin | Signal    | Pin | Signal |

|-----|-----------|-----|--------|

| 1   | D00 H     | 2   | DGND   |

| 3   | D01 H     | 4   | DGND   |

| 5   | D02 H     | 6   | DGND   |

| 7   | D03 H     | 8   | DGND   |

| 9   |           | 10  |        |

| 11  | AGND      | 12  | AGND   |

| 13  | DAC D OUT | 14  | AGND   |

| 15  | DAC C OUT | 16  | AGND   |

| 17  | DAC B OUT | 18  | AGND   |

| 19  | DAC A OUT | 20  | AGND   |

Figure 4 Connecting AAV11-C to a Differential Input Device

Figure 5 AAV11-C Block Diagram

#### DESCRIPTION

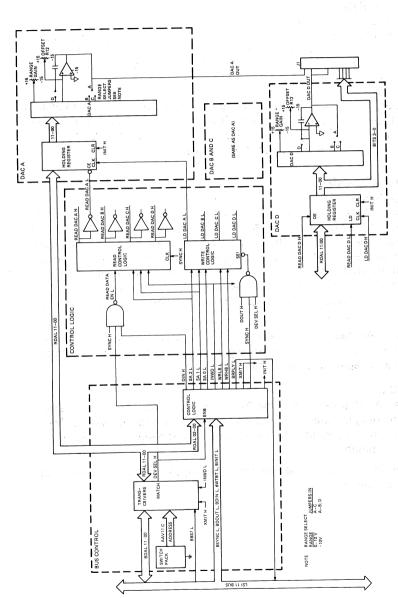

Illustrated in Figure 5 is the block diagram of the AAV11-C. It is addressable from the LSI-11 bus at its interface transceivers. An address switch pack determines the device address of the board. Setting the address switch pack is described in the Configuration section of the discussion on this interface.

Binary data is written to these registers to be converted to an analog voltage. BDAL 000-11 becomes RDAL 00-11 within the AAV11-C. This is the input to the holding register of the DAC selected. LD DAC A, B, C, or D clocks the data into the DAC register.

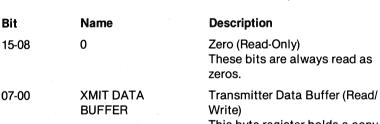

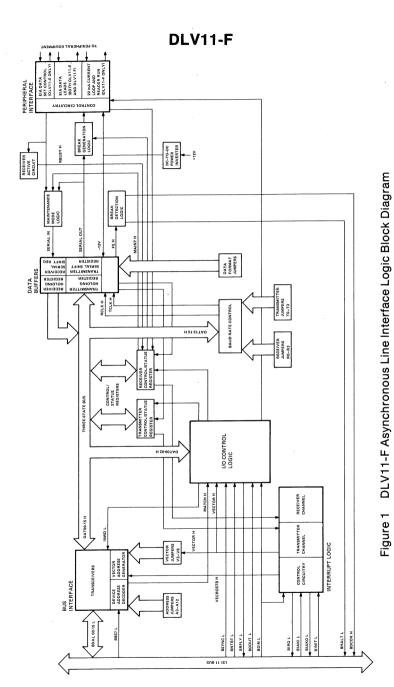

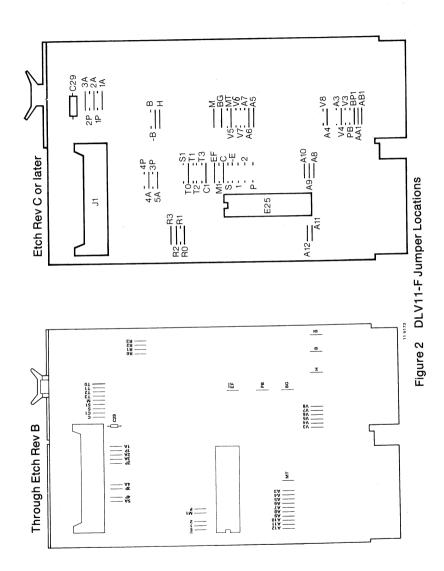

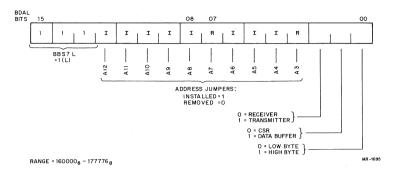

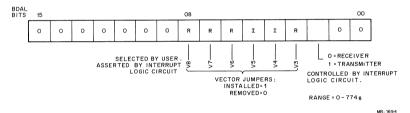

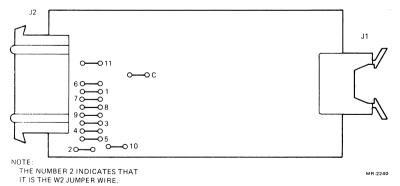

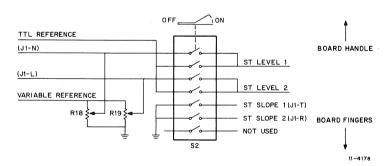

### DAC A, B, AND C