FP11 floating-point processor maintenance manual

FP11 floating-point processor maintenance manual

1st Edition, March 1972 2nd Printing (Rev), October 1972 3rd Printing, December 1972 4th Printing, April 1973 5th Printing (Rev), August 1973 6th Printing, January 1974 7th Printing, November 1974

Copyright © 1972, 1973, 1974 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

FLIP CHIP

FOCAL

DIGITAL

COMPUTER LAB

**UNIBUS**

### CONTENTS

|           |                                            | Page |

|-----------|--------------------------------------------|------|

| CHAPTER 1 | INTRODUCTION                               |      |

| 1.1       | General                                    | 1-1  |

| 1.2       | Floating-Point Arithmetic                  | 1-1  |

| 1.2.1     | Floating-Point Addition and Subtraction    | 1-1  |

| 1.2.2     | Floating-Point Multiplication and Division | 1-2  |

| 1.3       | Floating-Point Features                    | 1-2  |

| 1.4       | Simplified Block Diagram Description       | 1-3  |

| 1.5       | FP11/Memory Word Relationships             | 1-4  |

| 1.5.1     | FP11 Hidden Bit                            | 1-5  |

| 1.6       | FP11-B Physical Description (PDP-11/45)    | 1-6  |

| CHAPTER 2 | INTERFACE                                  |      |

| 2.1       | Introduction                               | 2-1  |

| 2.2       | Interface Signals                          | 2-1  |

| 2.3       | 11/45 Interface                            | 2-3  |

| CHAPTER 3 | DATA AND DATA FORMATS                      |      |

| 3.1       | FP11 Data Formats                          | 3-1  |

| 3.1.1     | FP11 Integer Format                        | 3-1  |

| 3.1.2     | FP11 Floating-Point Formats                | 3-1  |

| 3.1.3     | Floating-Point Mantissa                    | 3-2  |

| 3.1.4     | Floating-Point Exponent                    | 3-2  |

| 3.2       | FP11 Program Status Register               | 3-3  |

| 3.3       | Processing of Floating-Point Exceptions    | 3-4  |

| 3.4       | FP11 Instruction Formats                   | 3-4  |

| 3.5       | Instruction Set                            | 3-7  |

| 3.6       | FP11 Programming Examples                  | 3-8  |

| CHAPTER 4 | CONTROL ROM                                |      |

| 4.1       | Introduction                               | 4-1  |

| 4.2       | Control ROM                                | 4-2  |

| 4.2.1     | Control ROM Flow Diagram                   | 4-5  |

| 4.2.2     | ROM Field Description                      | 4-12 |

| 4.2.3     | Detailed Analysis of ROM Word              | 4-20 |

| CHAPTER 5 | ARITHMETIC ALGORITHMS                      |      |

| 5.1       | Introduction                               | 5-1  |

| 5.2       | Floating-Point Addition and Subtraction    | 5-1  |

| 5.2.1     | Description of Fraction Processing         | 5-1  |

| 5.2.2     | Description of Exponent Processing         | 5-2  |

| 5.2.3     | Testing For Normalization                  | 5-4  |

## CONTENTS (Cont)

|           |                                        | Page |

|-----------|----------------------------------------|------|

| 5.3       | Floating-Point Multiplication          | 5-4  |

| 5.3.1     | Fundamental Concepts                   | 5-4  |

| 5.3.2     | Multiply Hardware                      | 5-6  |

| 5.3.3     | Multiply Timing                        | 5-11 |

| 5.4       | Division                               | 5-13 |

| 5.4.1     | Restoring Division                     | 5-13 |

| 5.4.2     | Non-Restoring Division                 | 5-13 |

| 5.4.3     | Non-Restoring Divide Using Normalizing | 5-14 |

| 5.4.4     | Divide Timing                          | 5-17 |

|           |                                        |      |

| CHAPTER 6 | FP11-B LOGIC DIAGRAM DESCRIPTIONS      |      |

| 6.1       | Introduction                           | 6-1  |

| 6.2       | Detailed Logic Diagram Descriptions    | 6-1  |

| 6.2.1     | FRHA                                   | 6-2  |

| 6.2.2     | FRHB, FRHC, FRHD                       | 6-2  |

| 6.2.3     | FRHE                                   | 6-2  |

| 6.2.3.1   | Multiply                               | 6-3  |

| 6.2.3.2   | MR1 and MR0 Register                   | 6-3  |

| 6.2.3.3   | MUL ARITH                              | 6-3  |

| 6.2.3.4   | Pause Logic                            | 6-4  |

| 6.2.3.5   | STRG 1 Flip-Flop                       | 6-4  |

| 6.2.3.6   | AR Control                             | 6-4  |

| 6.2.3.7   | QR Control                             | 6-5  |

| 6.2.3.8   | MUL SUB Flip-Flop                      | 6-6  |

| 6.2.3.9   | AR Clock                               | 6-6  |

| 6.2.3.10  | QR Clock                               | 6-6  |

| 6.2.4     | FRHF                                   | 6-7  |

| 6.2.4.1   | Sign Bit                               | 6-7  |

| 6.2.4.2   | RSQR IN                                | 6-7  |

| 6.2.4.3   | RR2, RR1, RR0                          | 6-7  |

| 6.2.4.4   | LSQR IN                                | 6-8  |

| 6.2.4.5   | SS Logic                               | 6-8  |

| 6.2.4.6   | SD Logic                               | 6-8  |

| 6.2.4.7   | Step Counter                           | 6-8  |

| 6.2.5     | FRHH                                   | 6-9  |

| 6.2.5.1   | Time State Generator                   | 6-9  |

| 6.2.5.2   | PAUSE Flip-Flop                        | 6-9  |

| 6.2.5.3   | MPAUSE Flip-Flop                       | 6-9  |

| 6.2.6     | FRHJ                                   | 6-11 |

| 6.2.7     | FRLA, FRLB, FRLC, FRLD                 | 6-11 |

| 6.2.8     | FRLE, FRLF, FRLH, FRLJ, and FRLK       | 6-11 |

| 6.2.8.1   | FALU Control                           | 6-12 |

| 6.2.8.2   | Carry-Look-Ahead                       | 6-12 |

## CONTENTS (Cont)

|          |                              | Page |

|----------|------------------------------|------|

| 6.2.8.3  | Rounding                     | 6-12 |

| 6.2.8.4  | Increment                    | 6-13 |

| 6.2.9    | FRLL, FRLM                   | 6-13 |

| 6.2.9.1  | QR                           | 6-13 |

| 6.2.9.2  | BR                           | 6-13 |

| 6.2.9.3  | EXP NEQ 0                    | 6-13 |

| 6.2.9.4  | LSQR31 IN H                  | 6-13 |

| 6.2.10   | FRLN                         | 6-13 |

| 6.2.11   | FRLP                         | 6-13 |

| 6.2.11.1 | Floating Status Register     | 6-13 |

| 6.2.11.2 | Floating Condition Codes     | 6-14 |

| 6.2.11.3 | FER Flip-Flop                | 6-14 |

| 6.2.12   | FRMA, FRMB                   | 6-14 |

| 6.2.12.1 | Control ROM Address Register | 6-14 |

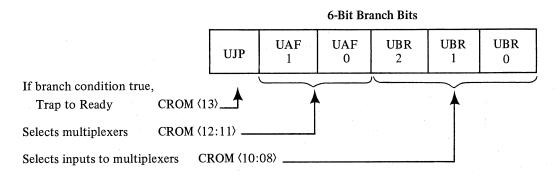

| 6.2.12.2 | Address Modification         | 6-14 |

| 6.2.12.3 | Traps                        | 6-15 |

| 6.2.13   | FRMC, FRMD                   | 6-16 |

| 6.2.14   | FRME, FRMF                   | 6-16 |

| 6.2.15   | FRMH                         | 6-16 |

| 6.2.15.1 | ALU Select                   | 6-16 |

| 6.2.16   | FRMJ                         | 6-18 |

| 6.2.16.1 | ICLR and 20 ABORT            | 6-18 |

| 6.2.16.2 | Set ATTENTION                | 6-18 |

| 6.2.16.3 | Set FP REQ                   | 6-18 |

| 6.2.16.4 | Set FP SYNC                  | 6-20 |

| 6.2.16.5 | Clear ATTN                   | 6-20 |

| 6.2.16.6 | FP SYNC L                    | 6-20 |

| 6.2.16.7 | Clear FP SYNC                | 6-20 |

| 6.2.16.8 | Clear FP REQ                 | 6-20 |

| 6.2.17   | FXPA and FXPB                | 6-20 |

| 6.2.17.1 | EMX                          | 6-20 |

| 6.2.17.2 | EALU                         | 6-20 |

| 6.2.17.3 | Constant Field Decoding      | 6-20 |

| 6.2.18   | FXPC                         | 6-21 |

| 6.2.18.1 | BD Register                  | 6-21 |

| 6.2.18.2 | BA Register                  | 6-21 |

| 6.2.19   | FXPD                         | 6-22 |

| 6.2.20   | FXPE                         | 6-22 |

| 6.2.21   | FXPF                         | 6-22 |

| 6.2.21.1 | B Condition Code Logic       | 6-22 |

| 6.2.21.2 | Range ROM                    | 6-22 |

| 6.2.21.3 | SUB FRAC                     | 6-22 |

| 6.2.21.4 | Illegal Op Code Detector     | 6-22 |

| 6222     | EVDH                         | 622  |

## CONTENTS (Cont)

Page

| 6.2.23                                                      | FXPJ                                                                                                                                                                                                                                                                                                                              | 6-23                                                                             |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 6.2.24                                                      | FXPK                                                                                                                                                                                                                                                                                                                              | 6-23                                                                             |

| 6.2.24.1                                                    | DIMX                                                                                                                                                                                                                                                                                                                              | 6-23                                                                             |

| 6.2.24.2                                                    | Drivers                                                                                                                                                                                                                                                                                                                           | 6-24                                                                             |

| 6.2.25                                                      | FXPL                                                                                                                                                                                                                                                                                                                              | 6-24                                                                             |

|                                                             |                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| CHAPTER 7                                                   | MAINTENANCE                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 7.1                                                         | Introduction                                                                                                                                                                                                                                                                                                                      | 7-1                                                                              |

| 7.2                                                         | Maintenance Module                                                                                                                                                                                                                                                                                                                | 7-1                                                                              |

| 7.2.1                                                       | Time Margining Using Maintenance Module                                                                                                                                                                                                                                                                                           | 7-2                                                                              |

| 7.3                                                         | Special Maintenance Instructions                                                                                                                                                                                                                                                                                                  | 7-3                                                                              |

| 7.3.1                                                       | LDUB – Load Microbreak Register (170003)                                                                                                                                                                                                                                                                                          | 7-3                                                                              |

| 7.3.2                                                       | LDSC – Load Step Counter (170004)                                                                                                                                                                                                                                                                                                 | 7-3                                                                              |

| 7.3.3                                                       | STA0 – Store AR In AC0 (170005)                                                                                                                                                                                                                                                                                                   | 7-3                                                                              |

| 7.3.4                                                       | STQ0 – Store QR In AC0 (170007)                                                                                                                                                                                                                                                                                                   | 7-4                                                                              |

| 7.3.5                                                       | MRS – Maintenance Right Shift (170006)                                                                                                                                                                                                                                                                                            | 7-4                                                                              |

| 7.3.6                                                       | Maintenance Instruction Programming Example                                                                                                                                                                                                                                                                                       | 7-4                                                                              |

| 7.4                                                         | Console Display Features                                                                                                                                                                                                                                                                                                          | 7-8                                                                              |

| 7.4.1                                                       | Display of ROM Address                                                                                                                                                                                                                                                                                                            | 7-8                                                                              |

| 7.4.2                                                       | Display of EALU Contents                                                                                                                                                                                                                                                                                                          | 7-8                                                                              |

| 7.5                                                         | Maintenance Programming                                                                                                                                                                                                                                                                                                           | 7-8                                                                              |

|                                                             |                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

|                                                             |                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| APPENDIX A                                                  | SIGNAL GLOSSARY                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| APPENDIX A                                                  | SIGNAL GLOSSARY                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| APPENDIX A                                                  |                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| APPENDIX A                                                  | SIGNAL GLOSSARY  ILLUSTRATIONS                                                                                                                                                                                                                                                                                                    |                                                                                  |

| APPENDIX A                                                  |                                                                                                                                                                                                                                                                                                                                   | Page                                                                             |

|                                                             | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                     | Page                                                                             |

| Figure No.                                                  | ILLUSTRATIONS<br>Title                                                                                                                                                                                                                                                                                                            |                                                                                  |

| Figure No.                                                  | ILLUSTRATIONS  Title  Floating-Point Representation                                                                                                                                                                                                                                                                               | 1-1                                                                              |

| Figure No. 1-1 1-2                                          | ILLUSTRATIONS  Title  Floating-Point Representation  FP11 Simplified Block Diagram                                                                                                                                                                                                                                                | 1-1<br>1-4                                                                       |

| Figure No. 1-1 1-2 1-3                                      | ILLUSTRATIONS  Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration                                                                                                                                                                                                                       | 1-1<br>1-4<br>1-5                                                                |

| Figure No. 1-1 1-2 1-3 1-4                                  | ILLUSTRATIONS  Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration FP11                                                                                                                                                                                                                  | 1-1<br>1-4<br>1-5<br>1-6                                                         |

| Figure No. 1-1 1-2 1-3 1-4                                  | ILLUSTRATIONS  Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration FP11 FP11-B Module Layout                                                                                                                                                                                             | 1-1<br>1-4<br>1-5<br>1-6<br>1-7                                                  |

| Figure No. 1-1 1-2 1-3 1-4 1-5 2-1                          | ILLUSTRATIONS  Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration FP11 FP11-B Module Layout 11/45 Simplified Interface Diagram                                                                                                                                                          | 1-1<br>1-4<br>1-5<br>1-6<br>1-7<br>2-1                                           |

| Figure No.  1-1 1-2 1-3 1-4 1-5 2-1 2-2                     | ILLUSTRATIONS  Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration FP11 FP11-B Module Layout 11/45 Simplified Interface Diagram CPU/FPP Interface Diagram                                                                                                                                | 1-1<br>1-4<br>1-5<br>1-6<br>1-7<br>2-1<br>2-3                                    |

| Figure No.  1-1 1-2 1-3 1-4 1-5 2-1 2-2                     | ILLUSTRATIONS  Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration FP11 FP11-B Module Layout 11/45 Simplified Interface Diagram CPU/FPP Interface Diagram Sequence of Events for Load Instruction                                                                                        | 1-1<br>1-4<br>1-5<br>1-6<br>1-7<br>2-1<br>2-3<br>2-4                             |

| Figure No.  1-1 1-2 1-3 1-4 1-5 2-1 2-2 2-3 3-1             | Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration FP11 FP11-B Module Layout 11/45 Simplified Interface Diagram CPU/FPP Interface Diagram Sequence of Events for Load Instruction Integer Formats                                                                                       | 1-1<br>1-4<br>1-5<br>1-6<br>1-7<br>2-1<br>2-3<br>2-4<br>3-1                      |

| Figure No.  1-1 1-2 1-3 1-4 1-5 2-1 2-2 2-3 3-1 3-2         | ILLUSTRATIONS  Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration FP11 FP11-B Module Layout 11/45 Simplified Interface Diagram CPU/FPP Interface Diagram Sequence of Events for Load Instruction Integer Formats Floating-Point Data Formats                                            | 1-1<br>1-4<br>1-5<br>1-6<br>1-7<br>2-1<br>2-3<br>2-4<br>3-1<br>3-2               |

| Figure No.  1-1 1-2 1-3 1-4 1-5 2-1 2-2 2-3 3-1 3-2 3-3     | ILLUSTRATIONS  Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration FP11 FP11-B Module Layout 11/45 Simplified Interface Diagram CPU/FPP Interface Diagram Sequence of Events for Load Instruction Integer Formats Floating-Point Data Formats Status Register Format                     | 1-1<br>1-4<br>1-5<br>1-6<br>1-7<br>2-1<br>2-3<br>2-4<br>3-1<br>3-2<br>3-3        |

| Figure No.  1-1 1-2 1-3 1-4 1-5 2-1 2-2 2-3 3-1 3-2 3-3 3-4 | ILLUSTRATIONS  Title  Floating-Point Representation FP11 Simplified Block Diagram Accumulator Configuration FP11 FP11-B Module Layout 11/45 Simplified Interface Diagram CPU/FPP Interface Diagram Sequence of Events for Load Instruction Integer Formats Floating-Point Data Formats Status Register Format Instruction Formats | 1-1<br>1-4<br>1-5<br>1-6<br>1-7<br>2-1<br>2-3<br>2-4<br>3-1<br>3-2<br>3-3<br>3-5 |

## ILLUSTRATIONS (Cont)

| Figure No. | Title                                         | Page |

|------------|-----------------------------------------------|------|

| 5-2        | Multiply Flow Diagram                         | 5-7  |

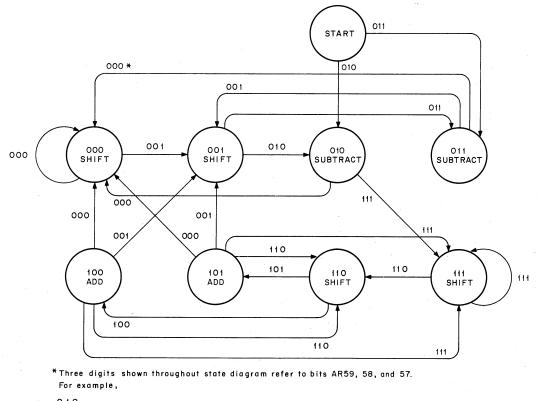

| 5-3        | Multiply State Diagram                        | 5-8  |

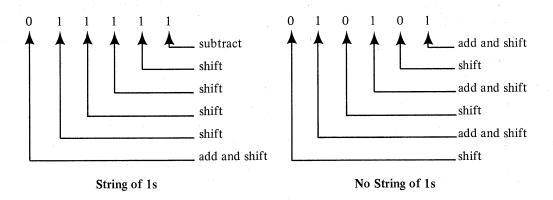

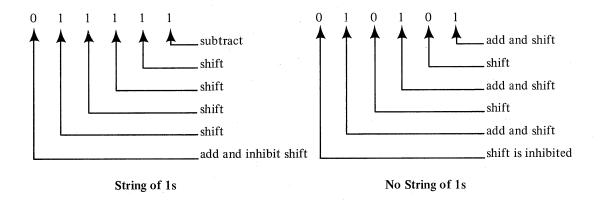

| 5-4        | Examples of Floating-Point Multiplication     | 5-9  |

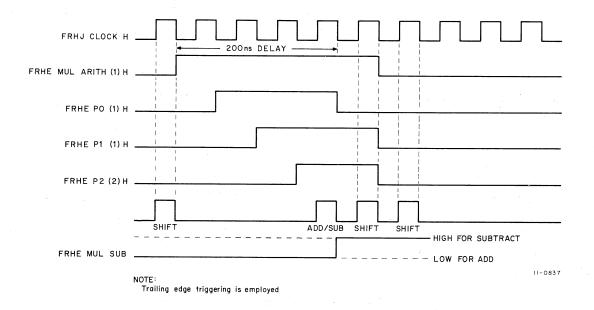

| 5-5        | Multiply and Divide Timing Diagram            | 5-11 |

| 5-6        | Example of Non-Restoring Division             | 5-14 |

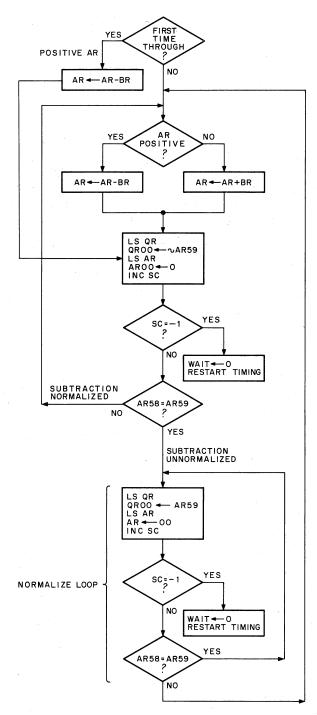

| 5-7        | Divide Flow Diagram                           | 5-16 |

| 5-8        | State Diagram for Divide                      | 5-17 |

| 5-9        | Examples of Floating Point Division           | 5-18 |

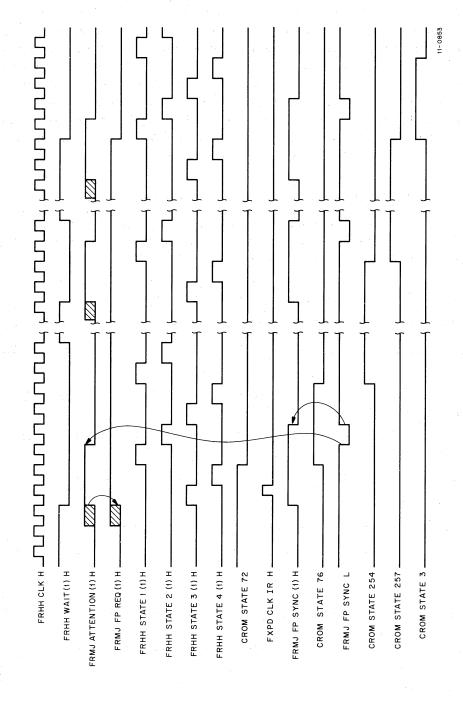

| 6-1        | Time State Generator Timing Relationships     | 6-10 |

| 6-2        | Scratchpad Configuration                      | 6-12 |

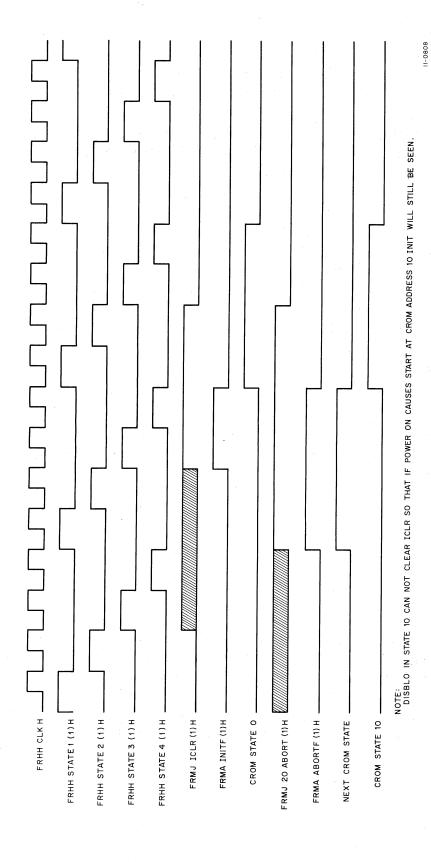

| 6-3        | ICLR, INIT, and 20 Abort Timing Relationships | 6-19 |

| <b></b>    | TABLES                                        |      |

| Table No.  | Title                                         | Page |

| 3-1        | Format of FP11 Instructions                   | 3-6  |

| 3-2        | Instruction Set                               | 3-9  |

| 4-1        | Flow Diagram Statements                       | 4-7  |

| 4-2        | ROM Fields                                    | 4-13 |

| 5-1        | Add and Subtract Implementation               | 5-2  |

| 6-1        | Arithmetic Anticipation                       | 6-4  |

| 6-2        | Multiplexer Branching Conditions              | 6-16 |

| 6-3        | ALU Control Selection                         | 6-17 |

| 6-4        | Scratch Address Selection                     | 6-18 |

#### **FOREWORD**

The PDP-11 Floating-Point Processor is an optional arithmetic processor used with the PDP-11/45. This processor eliminates the necessity of writing complex software routines to implement arithmetic operations. This manual is divided into the following seven chapters and two appendices:

- Chapter 1 is both a system description and a physical description of the FP11.

- Chapter 2 is a description of the PDP-11/45 and FP11 interface.

- Chapter 3 is a description of the data and instruction formats and describes the FP11 instruction set.

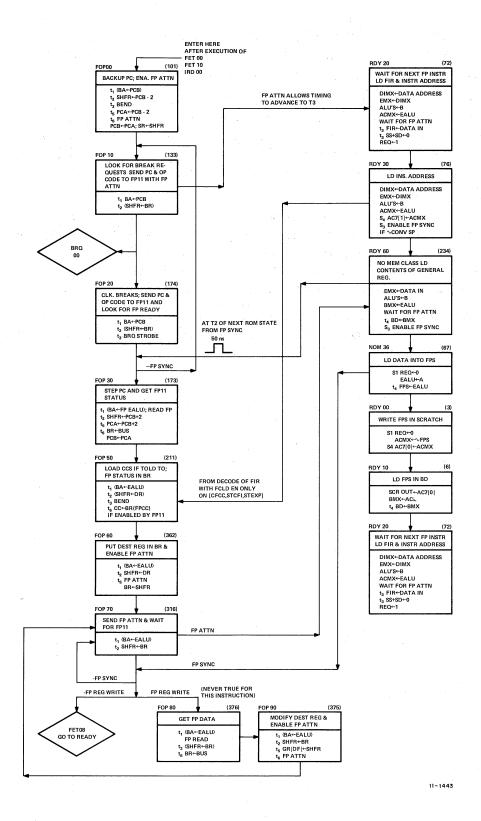

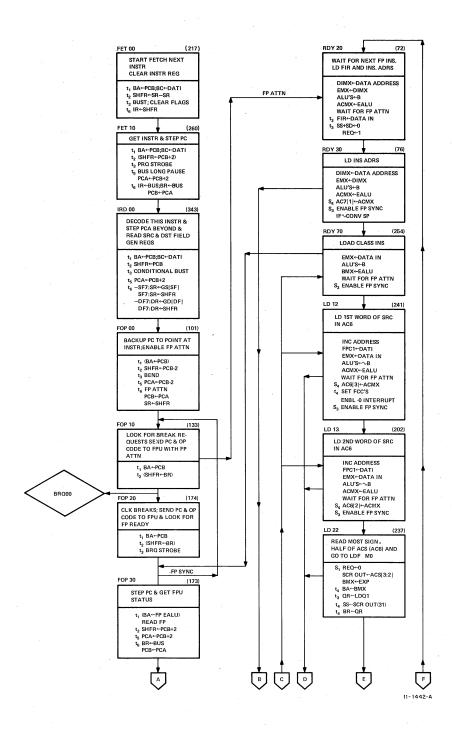

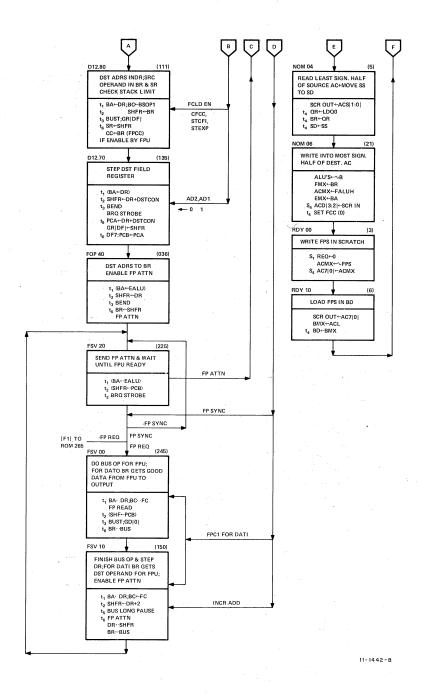

- Chapter 4 is a description of the control ROM used to microprogram the FP11. A description of the FP11 flow diagrams is also included in this chapter.

- Chapter 5 is a conceptual description of the add, subtract, multiply and divide algorithms.

- Chapter 6 is a detailed description of the FP11 logic diagrams.

- Chapter 7 provides maintenance information on the Maintenance Module, 11/45 console, FP11 maintenance instructions, and diagnostic programming.

- Appendix A is a brief description of the integrated circuits in the FP11.

- Appendix B is a signal glossary of the FP11.

The following list of documents supplement the information contained in this manual.

PDP-11/45 Maintenance Manual

KB11 Central Processor Maintenance Manual

PDP-11/45 Processor Handbook

PDP-11/45 Unibus Interface Manual (2nd edition)

TTL Integrated Circuits Catalog from Texas Instruments

TTL Catalog Supplement from Texas Instruments

MSI/TTL Integrated Circuits from Texas Instruments

INTEL LSI Product Guide

The Integrated Circuits Catalog for Design Engineers

DEC-11-H45A-D

DEC-11-HKBA-D

DEC-11-HIAB-D

CC-201-R

Catalog Supplement CC-301

Bulletin CB-125

# CHAPTER 1 INTRODUCTION

#### 1.1 GENERAL

The FP11 Floating-Point Processor is a hardware option used with the PDP-11/45 Central Processor. The FP11 enables the PDP-11 Central Processor to perform arithmetic and logic operations using floating-point arithmetic. The prime advantage is increased speed without the necessity of writing complex floating-point software routines. The FP11 has single- and double-precision floating-point capability. Prior to describing the FP11 Floating-Point Unit, several fundamentals of floating-point arithmetic are presented.

#### 1.2 FLOATING-POINT ARITHMETIC

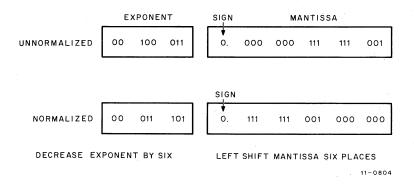

Floating-point representation of a binary number consists of two parts, an *exponent* and a *mantissa*. The mantissa is a fraction in sign and magnitude format with the binary point positioned between the sign bit and the most significant bit. If the mantissa is normalized, all leading 0s are eliminated from the binary representation; the most significant bit is thus a logical 1. Leading 0s are removed by shifting the mantissa left; however, each left shift of the mantissa must be followed by a decrement of the exponent value to maintain the true value of the number. The exponent value represents the power of 2 by which the mantissa is multiplied to obtain the value to be used. Figure 1-1 shows an unnormalized number in floating-point notation and then the same number after it has been normalized.

Figure 1-1 Floating-Point Representation

### 1.2.1 Floating-Point Addition and Subtraction

For floating-point addition or subtraction operations, the exponents must be aligned or equal. If they are not aligned, the mantissa with the smaller exponent is shifted right until they are. Each shift to the right is

accompanied by an incrementing of the exponent value. When the exponents are aligned or equal, the mantissa can be added or subtracted, whichever the case may be. The exponent value indicates the number of places the binary point is to be moved to obtain the actual representation of the number.

In the example below, the number  $7_{10}$  is added to the number  $40_{10}$ , using floating-point representation. Note that the exponents are first aligned and then the mantissas are added; the exponent value dictates the final location of the binary point.

0. 101 000 000 000 000

$$x2^6 = 50_8 = 40_{10}$$

0. 111 000 000 000 000  $x2^3 = 7_8 = 7_{10}$

a. To align exponents, shift the mantissa with the smaller exponent three places to the right and increment the exponent by 3.

0. 101 000 000 000 000

$$x2^6 = 50_8 = 40_{10}$$

0. 000 111 000 000 000  $x2^6 = 7_8 = 7_{10}$

0. 101 111 000 000 000  $x2^6 = 57_8 = 47_{10}$

b. Move the binary point six places to the right.

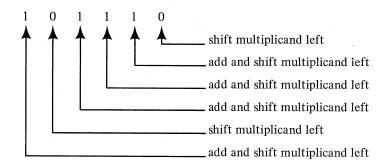

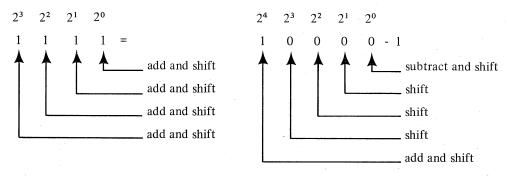

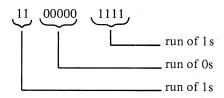

#### 1.2.2 Floating-Point Multiplication and Division

In floating-point multiplication, the mantissas are multiplied and the exponents are added. For floating-point division, the mantissas are divided and the exponents are subtracted.

There is no requirement to align the binary point in the floating-point multiplication or division.

In the following example, the number  $7_{10}$  is multiplied by the number  $5_{10}$ . An eight-bit register is assumed for simplicity.

a. Move the binary point six places to the right.

$$.100011.00000000 = 43_8 = 35_{10}$$

#### 1.3 FLOATING-POINT FEATURES

The Floating-Point Processor is an integral part of the central processor. It uses the same memory management facilities provided by the Memory Segmentation option and similar addressing modes. Floating-point instructions can reference any core location, the CPU general registers, and any of the floating-point accumulators discussed in this chapter. Some of the notable features of the FP11 Floating-Point Unit are listed as follows:

- Performs arithmetic operations on 32- or 64-bit floating-point numbers.

- Includes special instructions to optimize input/output routines and mathematical subroutines.

- Utilizes microprogramming techniques for reduced cost.

- Compatible with existing PDP-11 address modes.

- Overlap processing, i.e., CPU and FP11 can run simultaneously.

- Allow execution of in-line code, i.e., CPU and floating-point instructions can be interspersed as desired.

- Employs multiple accumulators for ease of data handling.

- Is capable of converting 16- or 32-bit integers to 32- or 64-bit floating-point numbers during the load class of instructions, if desired.

- Is capable of converting 32- or 64-bit floating-point numbers to 16- or 32-bit integers during the Store class of instructions, if desired.

- Is capable of converting single-precision floating point to double-precision floating point and vice versa during the Store class of instructions, if desired.

- Average single-precision multiply time is  $6 \mu s$ .

- Average double-precision multiply time is 9.5  $\mu$ s.

- Average single-precision divide time is 7.5  $\mu$ s.

- Average double-precision divide time is 12.5 μs.

- Contains floating-point condition codes that can be copied into the CPU status register to provide the CPU with the capability of branching on results of floating-point operations.

- Contains built-in maintenance instructions for ease of maintenance.

- Hardware provides for flexible handling of error conditions.

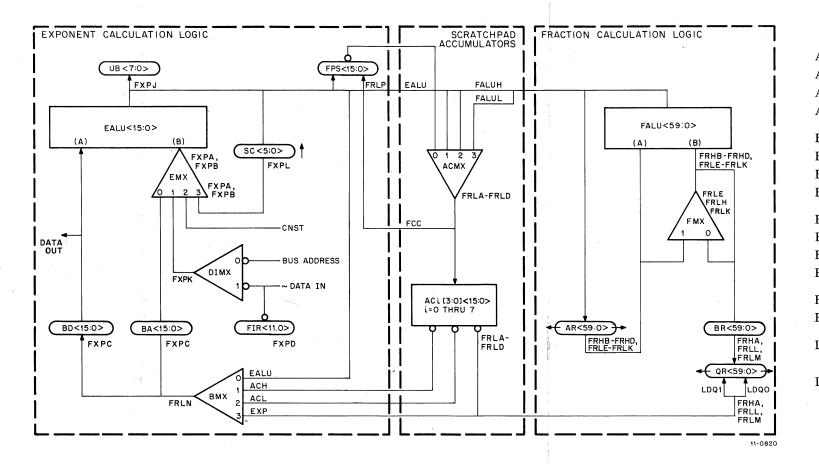

#### 1.4 SIMPLIFIED BLOCK DIAGRAM DESCRIPTION

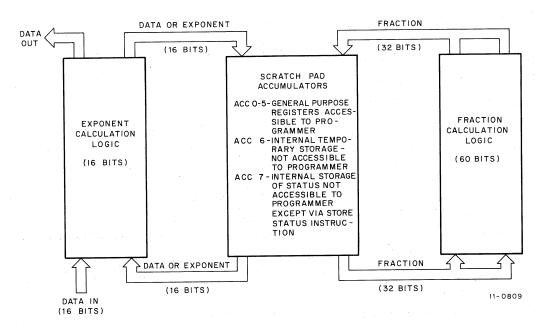

Figure 1-2 shows a simplified block diagram of the Floating Point Processor. The major elements of the FP11 are the exponent calculation logic, the accumulators, and the fraction calculation logic.

The exponent calculation logic connects to a 16-bit wide data path that processes exponent or data information; the fraction calculation logic consists of a 60-bit wide data path that processes the fractional part of the operands. The fraction calculation logic sends or receives data to or from the 32-bit scratchpad accumulator.

The accumulators (ACs) are general-purpose read/write scratchpad memories with nondestructive readout. Accumulators 5 through 0 are used for storage of general-purpose data and for register-to-register transfers. Accumulator 6 is used as internal storage and is not accessible by the programmer.

Accumulator 7 is used for internal temporary storage of the following status information:

- 1. FEC Floating Exception Code a number that identifies the cause of the interrupt.

- 2. FEA Floating Exception Address the address of the instruction that caused an error.

Accumulator 7 is also used for temporary storage of the address of the current instruction, the program status (FPS), and the exception code.

Figure 1-2 FP11 Simplified Block Diagram

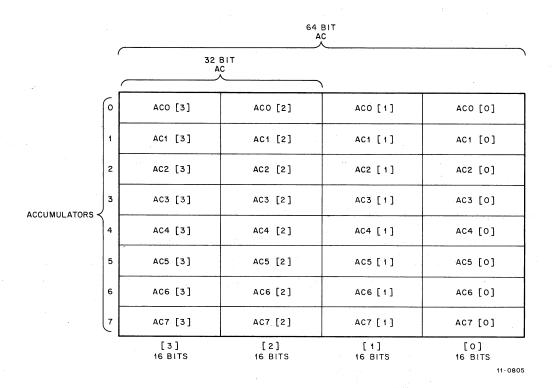

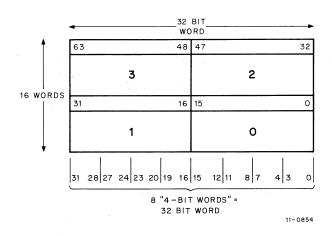

The ACs are interpreted as 32- or 64-bits long depending on the data formats (refer to Chapter 3). For a single-precision floating-point format, a 32-bit AC is specified (the left-most 32 bits as shown in Figure 1-3). For double-precision floating-point format, a 64-bit AC is specified. The ACs are accessible in 32-bit words. The designated AC and the length of the word contained therein is specified as follows:

The number following the AC designates one of 8 accumulators, and each number in the bracket denotes a 16-bit word. In the first example, AC 5 contains a 32-bit word; in the second case, AC 3 contains a 64-bit word [3:2] [1:0]. The [3] represents the most significant 16 bits, and the [0] represents the least-significant 16 bits. This notation is carried throughout this manual and also in the associated flow diagrams.

#### 1.5 FP11/MEMORY WORD RELATIONSHIPS

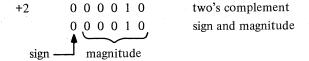

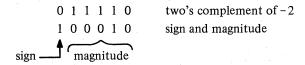

Words stored in memory are either integers or floating-point numbers. Integers are stored in 2's complement format and are converted to sign and magnitude format when transferred to the FP11. Floating-point numbers are already in sign and magnitude format and are transferred directly to the FP11 without being converted. When the FP11 finishes processing the numbers, they can be transferred back to memory as two's complement integers or sign and magnitude floating-point numbers. Floating-point numbers are normalized before being transferred back to memory.

All positive numbers are represented the same in two's complement or in sign and magnitude format. An example is the positive number 2 shown below.

For a negative 2, the number is represented as shown below.

Figure 1-3 Accumulator Configuration

## NOTE AC 7 [1] contains address of instruction AC 7 [0] contains FPS (temporary storage of FEC)

#### 1.5.1 FP11 Hidden Bit

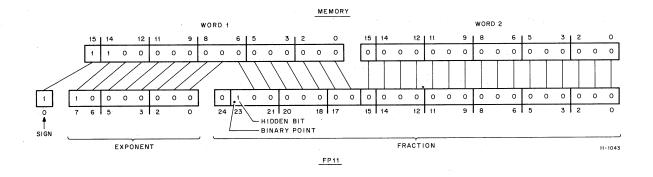

All numbers (fractions) transferred to the fraction calculation logic are transferred as positive fractions of the form 0.1 xxxx. Since the most significant bit to the right of the binary point is always a 1, this bit is referred to as the "hidden bit" and is dropped when the word is stored in memory. This provides another bit of significance in the FP11. Words transferred from memory to the FP11 are represented in the FP11 by a sign bit, eight bits of exponent and 23 bits (single-precision) or 55 bits (double-precision) of fraction. For example, consider the number minus 1/2. The sign is 1, the exponent is 200 which is equal to 2° power, and the fraction is .10....

Figure 1-4 shows the word as it appears in memory and how it appears when stored internally in the FP11.

Figure 1-4 FP11

Note that even with a negative number as shown above the fraction is treated as a positive normalized fraction (bit 24 = 0, bit 23 = 1). Bits 24 and 23 are dropped when the floating-point word is reassembled and stored back in memory.

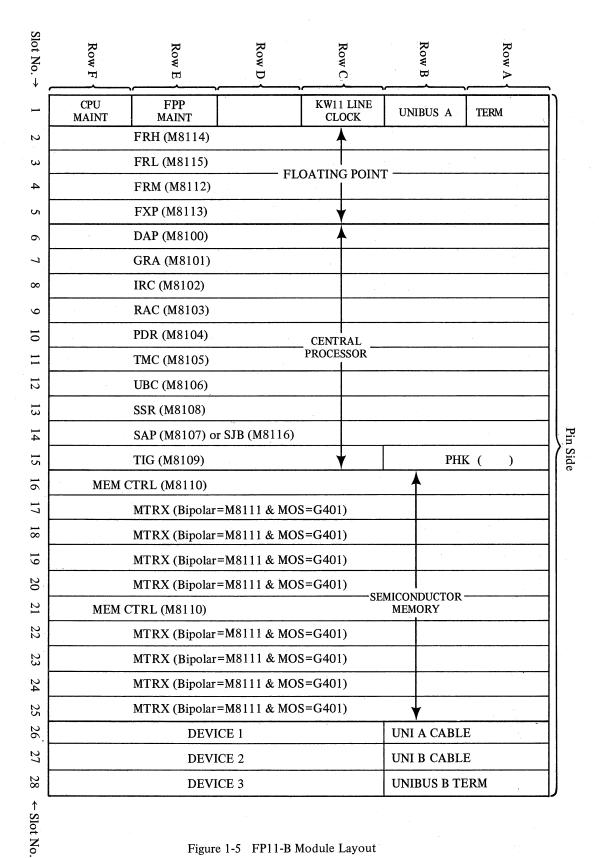

#### 1.6 FP11-B PHYSICAL DESCRIPTION (PDP-11/45)

The FP11-B Floating-Point Processor is used with the PDP-11/45 CPU. The FP11-B consists of four multi-layer hex modules that are plugged into the pre-wired KB11A Main Frame. The four modules plug into slots 2, 3, 4, and 5 and take-up rows A through F (see Figure 1-5). The chart below shows the slots associated with each module.

| Module      | Slot | Row         |

|-------------|------|-------------|

| M8113 - FXP | 5    | A through F |

| M8112 - FRM | 4    | A through F |

| M8115 - FRL | 3    | A through F |

| M8114 – FRH | 2    | A through F |

A +5V regulator card is included and is plugged into the upper power supply in slot A. The -15V needed for the time state generator on the FRH module is supplied by regulator E, which is included as part of the Central Processor Regulator Set.

Slot E1 on the KB11A Main Frame is reserved for the Floating-Point Maintenance Module (refer to Chapter 7 for additional information on this module). The +8 Vdc required for this module is obtained from the upper bulk supply (PS H742A).

Figure 1-5 FP11-B Module Layout

## CHAPTER 2 INTERFACE

#### 2.1 INTRODUCTION

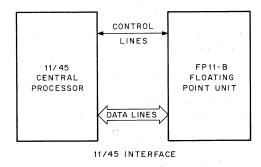

The Floating Point Processor connects directly to the 11/45 Central Processor (see Figure 2-1) and not to the Unibus. This is to allow for proper operation of the segmentation option and to increase the speed of instruction execution.

The 11/45 CPU fetches instructions from memory and decodes them. If the instruction contains a 17<sub>8</sub> op code, it is a floating-point instruction and the CPU branches to the CPU ROM states associated with floating-point instructions. At this point, the CPU/FP11-B interaction is initiated (refer to Paragraph 2.3).

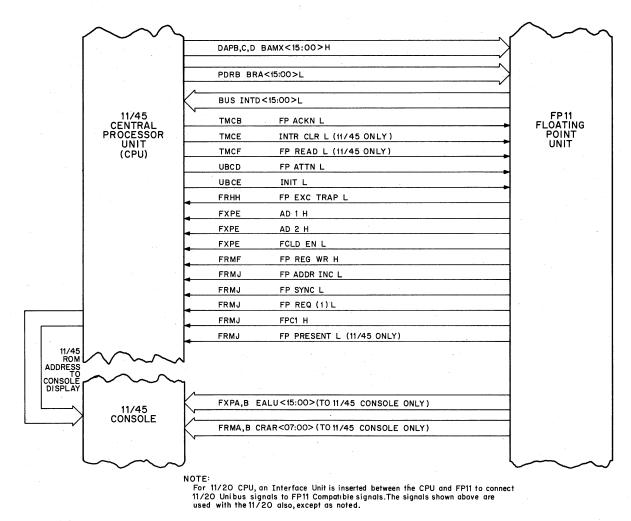

Figure 2-1 11/45 Simplified Interface Diagram

#### 2.2 INTERFACE SIGNALS

The signals that interface the 11/45 CPU to the FP11 are described below (see Figure 2-2).

| Signal             | Description                                                                                                     |

|--------------------|-----------------------------------------------------------------------------------------------------------------|

| BAMX (00:15) H     | Sixteen lines from the CPU that contain the address of the instruction.                                         |

| BR (00:15) B L     | Sixteen data lines that provide transfer of data from the CPU to FP11.                                          |

| BUS INTD (00:15) L | Sixteen lines used to send data from the FP11 to the CPU. These lines are also used by the segmentation option. |

| FP ACKN L          | A signal from the CPU indicating that an FP TRAP was received from the FP11.                                    |

| Signal        | Description                                                                                                                                 |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| INTR CLR L    | A signal from the 11/45 that indicates that the 11/45 CPU is in its interrupt service routine.                                              |  |  |

| FP READ L     | A signal from the $11/45$ that indicates that the BUS INTD lines can be used by the FP11.                                                   |  |  |

| FP ATTN L     | A signal from the CPU to the FP11 that accompanies information sent to or from the FP11.                                                    |  |  |

| INIT L        | An initialize pulse used to reset major registers in the FP.                                                                                |  |  |

| FP EXC TRAP L | This signal, when low, causes the CPU to trap to vector address $244_8$ (Trap Vector).                                                      |  |  |

| AD 1, AD 2 H  | Represent constants that are added to or subtracted from the general registers in the CPU for address calculation. The constants are:       |  |  |

|               | AD2 AD1                                                                                                                                     |  |  |

|               | 0 0 constant of 8<br>0 1 constant of 4<br>1 0 constant of 2<br>1 1 constant of 0                                                            |  |  |

| FCLD EN L     | This signal causes the FP11 floating-point condition codes to be written into the CPU condition codes.                                      |  |  |

| FP REG WR H   | When high, this signal causes BUS INTD data to be loaded into general registers in the CPU.                                                 |  |  |

| FP ADDR INC L | A signal to the CPU indicating that the address is to be incremented by 2.                                                                  |  |  |

| FP SYNC L     | A signal from the FP11 in response to FP ATTN indicating that the data has been accepted or that the FP11 is ready to send or receive data. |  |  |

| FP REQ (1) L  | A signal used in conjunction with FP SYNC to indicate that more data words are desired.                                                     |  |  |

| FPC1 H        | Indicates a DATO operation. When this signal goes low, it indicates a DATI operation.                                                       |  |  |

| FP PRESENT L  | Indicates the FP11 is present.                                                                                                              |  |  |

| EALU (00:15)  | Sixteen lines to console that allow the contents of EALU to be displayed (used with $11/45$ CPU).                                           |  |  |

Eight lines to console that allow the next ROM address to be displayed.

CRAR (00:07)

Figure 2-2 CPU/FPP Interface Diagram

11-0807

#### 2.3 11/45 INTERFACE

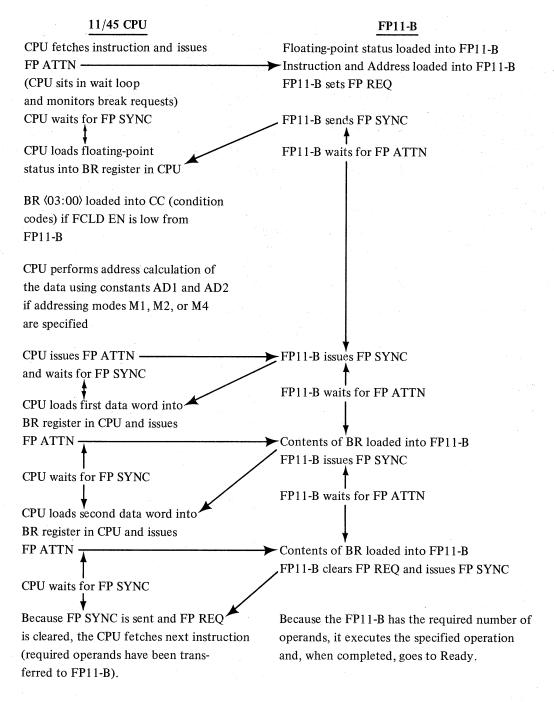

Figure 2-3 shows the interaction involved between the 11/45 CPU and the FP11-B for a floating-point Load instruction. The sequence of events for other instructions can be found in the FP11 flow diagrams. The CPU puts the instruction on the BRA lines accompanied by FP ATTN. The CPU also decrements the PC and puts the decremented PC on the BAMX lines (see Figure 2-2). It is necessary to transfer the contents of the PC to the FP11-B because the CPU and FP11 can execute instructions simultaneously. The CPU may jump or trap to a new location while the FP11 instruction is being executed, and if a floating-point error occurs the programmer can then determine the address of the FP11 instruction that caused the error condition.

After the instruction and address are on the lines, the CPU goes into a wait loop, monitoring break requests and also waiting for FP SYNC from the FP11. If a break request occurs, the CPU branches to its break service routine and issues an Abort signal (INTR CLR) to the FP11. This signal aborts the floating-point instruction in process. On return from the break service routine, the CPU fetches the next instruction; however, this instruction is the same instruction that was aborted since the PC was previously decremented.

If FP SYNC occurs before a break request, the CPU loads the status from the FP11 into the CPU (see Figure 2-3). If FCLD EN is low, the floating-condition codes (BR (3:07)) from the FP11 are inserted in the status word;

Figure 2-3 Sequence of Events for Load Instruction

otherwise, the word is unmodified. In addition, the CPU starts to calculate the address of the data. If addressing modes M1, M2, or M4 are specified, the address is calculated using constants AD1 and AD2. If another mode is specified, the address is calculated like any other destination address. On completion of the address calculation, the CPU issues FP ATTN to the FP11, and the FP11 responds with FP SYNC.

On receipt of FP SYNC from the FP11, the CPU loads the first data word into the BR register, raises FP ATTN, and waits for FP SYNC. The data word is loaded in the FP11-B, and the FP11-B raises FP SYNC, acknowledges receipt of this word, and awaits the next data word accompanied by FP ATTN.

The CPU loads the second data word into the BR register and raises FP ATTN. This word is loaded in the FP11-B and the FP11-B raises FP SYNC; however, because this is the last data word desired (single-precision floating-point format requires two data words), FP REQ is cleared. When the CPU receives FP SYNC with FP REQ cleared, it fetches the next instruction. While the CPU is fetching the instruction, the FP11-B proceeds to execute the operations specified. When this is completed, the FP11-B goes to the Ready state to await the next floating-point instruction.

When the FP11 is executing an instruction and the CPU fetches another FP11 instruction, the FP11 continues execution of the instruction and the CPU hangs in a wait loop. If a break request occurs while the CPU is in the wait loop, the CPU branches to its service routine and issues an Abort (INTR CLR) as previously described; however, because the FP11 is busy in this case, the Abort is not honored and the FP11 proceeds to complete execution of the instruction. The CPU subsequently refetches the instruction so it can be executed.

To further clarify the interaction between the CPU and the FP11, two examples are provided. The first (Figure 2-4) shows the interaction for address mode 0 and the second (Figure 2-5) shows the interaction for address mode 2.

Figure 2-4 LD FPS Instruction Interaction - Mode 0

Figure 2-5 LDF Instruction Interaction – Mode 2 (Sheet 1 of 2)

Figure 2-5 LDF Instruction Interaction – Mode 2 (Sheet 2 of 2)

# CHAPTER 3 DATA AND DATA FORMATS

#### 3.1 FP11 DATA FORMATS

The FP11 utilizes short (I) and long (L) integer format in addition to single-(F) and double-precision (D) floating-point format. The following paragraphs briefly define the integer formats followed by a description of the floating-point formats.

#### 3.1.1 FP11 Integer Format

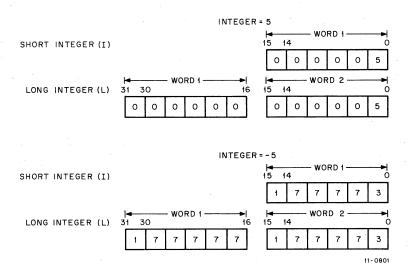

Integer format is represented in 2's complement notation in the FP11. The short-integer format is 16 bits long; the long-integer format is 32 bits long. In both instances the most significant bit represents the sign bit. Figure 3-1 shows the integer 5 in both formats followed by the integer minus 5 in both formats.

Figure 3-1 Integer Formats

#### 3.1.2 FP11 Floating-Point Formats

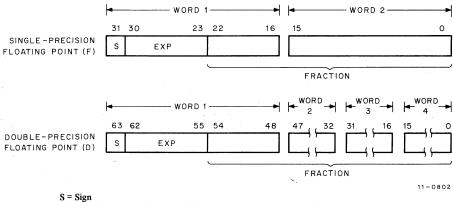

Single-precision floating-point format is 32 bits long and is designated by F; double-precision (extended) format is 64 bits long and is designated by D. All floating-point numbers are assumed to be normalized. The mantissa or fraction is represented in sign and magnitude format with the sign bit extended to the most significant bit position, as shown in Figure 3-2. Note that the 8-bit exponent separates the fraction from its associated sign.

EXP = Exponent in excess 200<sub>8</sub> notation (refer to Paragraph 3.1.4.)

Fraction = 23 or 55 bit fraction in sign and magnitude format. Binary point between bits 22 and 23 for F format or between bits 54 and 55 for D format.

Figure 3-2 Floating-Point Data Formats

#### 3.1.3 Floating-Point Mantissa

All floating-point numbers are normalized; thus, in sign and magnitude format, the mantissa has a range from 0.10000.... to 0.1111.... for positive operands and a range from 1.10000.... to 1.11111.... for negative operands. All operands transferred between the CPU and FP11 are in sign and magnitude format and are converted internally to 2's complement format to perform arithmetic operations. Because, in sign and magnitude format, the bit immediately to the right of the binary point is always a 1, it is not stored in memory or in the scratchpad accumulators. This *hidden bit* provides another bit of significance in the results of arithmetic operations. However, when data is loaded into the fractional calculation logic data path, the hardware inserts the hidden bit; this point must be kept in mind when examining results during maintenance procedures.

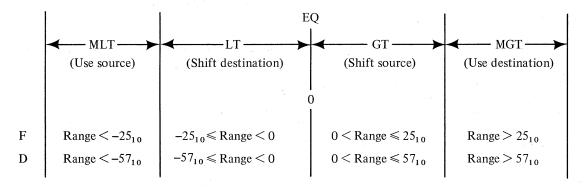

#### 3.1.4 Floating-Point Exponent

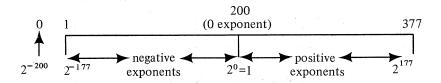

The exponent in the FP11 is specified by eight bits, providing a range from 0 to  $377_8$ . Excess 200 notation is used, which means that 200 is added to the exponent. Thus, an exponent of -177 is represented by  $001_8$ , an exponent of  $000_8$  is represented by  $200_8$ , and an exponent of 177 is represented by  $377_8$ .

For example, the number  $0.1_2$  is actually  $0.1 \times 2^0$ , and the exponent is represented as  $10\ 000\ 000_2$  because  $200_8$  represents an exponent of zero. The following chart shows the range of floating-point numbers that can be handled by the FP11. Only three bits are shown for simplicity, but they can be extended to any number.

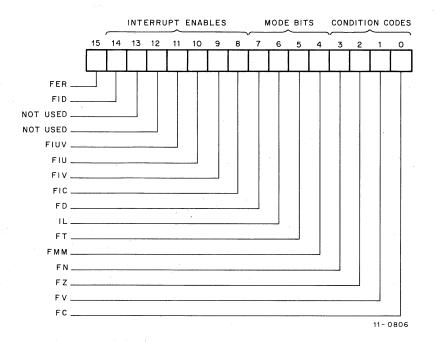

#### 3.2 FP11 PROGRAM STATUS REGISTER

The FP11 contains a program status register; this register contains FP11 condition codes (carry, overflow, zero, and negative) that can be copied into the Central Processor. In other words, FC, FV, FZ, and FN can be copied into the CPU's C, V, Z, and N condition codes, respectively. The program status register also contains four mode bits and additional bits used to enable various interrupt conditions. Figure 3-3 shows the layout of the program status register. Each bit shown in the figure is described in the following paragraphs:

Figure 3-3 Status Register Format

FER – This bit indicates an error condition of the FP11.

FID (Floating Interrupt Disable) - All interrupts by the FP11 are disabled when this bit is on.

FIUV (Floating Interrupt on Undefined Variable) — When this bit is set and a minus 0 is obtained from memory, an interrupt occurs. If the bit is not set, minus 0 can be loaded and stored; however, any arithmetic operation is treated as if it were a positive 0.

FIU (Floating Interrupt on Underflow) — When this bit is set, an underflow condition causes a floating underflow interrupt. The result of the operation causing the interrupt is correct except for the exponent, which is off by  $400_8$ . If the FIU bit is not set and underflow occurs, the result is set to zero.

FIV (Floating Interrupt on Overflow) — When this bit is set, floating overflow causes an interrupt. The result of the operation causing the interrupt is correct except for the exponent, which is off by  $400_8$ . If the FIV bit is not set, the result of the operation is the same; the only difference is that the interrupt does not occur.

FIC (Floating Interrupt on Integer Conversion Error) — When this bit is set, and the Store Convert Floating to Integer instruction causes FC to be set (indicating a conversion error), an interrupt occurs. When a conversion error occurs, the destination register is cleared and the source register is untouched. When FIC is reset, the result of the operation is the same; however, no interrupt occurs.

FD (Double-Precision Mode Bit) — This bit, when set, specifies double-precision format and, when reset, specifies single-precision format.

IL (Long-Precision Integer Mode Bit) — This bit is employed during conversion between integer and floating-point format. If set, double-precision, 2's complement integer format of 32 bits is specified, and, if reset, single-precision 2's complement integer of 16 bits is specified.

FT (Truncate Bit) — This bit, when set, causes the result of any floating-point operation to be truncated rather than rounded.

FMM (Maintenance Mode Bit) - This bit is used to enable special maintenance logic and is described in Chapter 7.

FC, FV, FZ, and FN — These bits are the four floating-point condition codes, which can be loaded in the CPU's C, V, Z, and N condition codes, respectively. This is accomplished by the Copy Floating Condition Codes (CFCC) instruction. To determine how each instruction affects the condition codes, refer to the instruction description in the PDP-11 Handbook.

For the Store Convert Floating to Integer instruction (which converts a floating-point number to an integer), the FC bit is set if the resulting integer is too large to be stored in the specified register.

#### 3.3 PROCESSING OF FLOATING-POINT EXCEPTIONS

The interrupt vector used to handle all floating-point interrupts is in location 244<sub>8</sub>. A total of seven possible interrupts can occur. These seven possible interrupt exceptions are encoded in the FP11 Exception Code Register (FEC). The interrupt exception codes represent an offset into a dispatch table, which routes the program to the right error handling routine. The dispatch table is a function of the software. The offset for each exception code is shown below followed by a brief description.

| FP11 Exception Code | Definition                                                                                                  |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2                   | Floating Op Code Error $-$ The FP11 causes an interrupt for an erroneous op code if the FID bit is not set. |  |  |  |  |

| 4                   | Floating Divide by Zero $-$ Division by zero causes an interrupt if the FID bit is not set.                 |  |  |  |  |

| 6                   | Floating Integer Conversion Error                                                                           |  |  |  |  |

| 10                  | Floating Overflow                                                                                           |  |  |  |  |

| 12                  | Floating Underflow                                                                                          |  |  |  |  |

| 14                  | Floating Undefined Variable                                                                                 |  |  |  |  |

| 16                  | Micro Break Trap                                                                                            |  |  |  |  |

#### NOTE

The traps for exception codes 6, 10, 12, and 14 can be enabled in the FPU's Program Status Register.

In addition to the FEC register, the FP11 contains a 16-bit Floating Exception Address register (FEA), which stores the address of the last floating-point instruction that caused a floating-point exception.

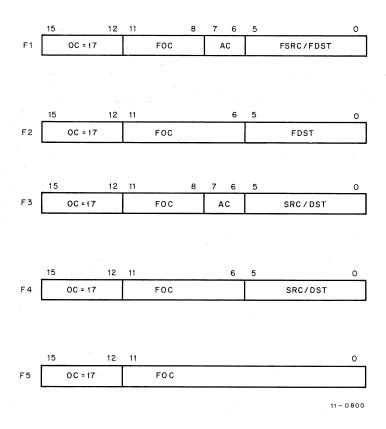

#### 3.4 FP11 INSTRUCTION FORMATS

The FP11 instruction set is divided into five formats as shown in Figure 3-4.

Figure 3-4 Instruction Formats

The 2-bit AC field (bits 6 and 7) allows selection of scratchpad accumulators 0 through 3 only. If address mode 0 is specified with formats F1 or F2, bits 2 through 0 are used to select the floating-point accumulator. Only accumulators 5 through 0 can be accessed in this manner. If accumulators 6 or 7 are specified, the FP11 traps if the interrupt is enabled.

The fields of the various instruction formats (refer to Table 3-1) are interpreted as follows:

| Mnemonic | Description                                                                                                                                                                                   |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OC       | Operation Code $-$ All floating-point instructions are designated by a 4-bit op code of $17_8$ .                                                                                              |  |  |  |  |

| FOC      | Floating Operation Code — The number of bits in this field varies with the format and is used to specify the actual floating-point operation.                                                 |  |  |  |  |

| SRC      | Source – A 6-bit source field identical to that in a PDP-11 instruction.                                                                                                                      |  |  |  |  |

| DST      | Destination $-$ A 6-bit destination field identical to that in a PDP-11 instruction.                                                                                                          |  |  |  |  |

| FSRC     | Floating Source $-$ A 6-bit field used only in format F1. It is identical to SRC, except in mode 0 when it references a floating-point accumulator rather than a CPU general register.        |  |  |  |  |

| FDST     | Floating Destination $-$ A 6-bit field used in formats F1 and F2. It is identical to DST, except in mode 0 when it references a floating-point accumulator instead of a CPU general register. |  |  |  |  |

| AC       | Accumulator $-$ A 2-bit field used in formats F1 and F3 to specify accumulators 0 through 3.                                                                                                  |  |  |  |  |

Table 3-1

Format of FP11 Instructions

| Instruction Format | Instruction                       | Mnemonic                                                         |

|--------------------|-----------------------------------|------------------------------------------------------------------|

| F1                 | ADD                               | ADDF FSRC, AC<br>ADDD FSRC, AC                                   |

|                    | LOAD                              | LDF FSRC, AC<br>LDD FSRC, AC                                     |

|                    | SUBTRACT                          | SUBF FSRC, AC<br>SUBD FSRC, AC                                   |

|                    | COMPARE                           | CMPF AC, FDST<br>CMPD AC, FDST                                   |

|                    | MULTIPLY                          | MULF FSRC, AC<br>MULD FSRC, AC                                   |

|                    | MODULO                            | MODF FSRC, AC<br>MODD FSRC, AC                                   |

|                    | STORE                             | STF AC, FDST<br>STD AC, FDST                                     |

|                    | DIVIDE                            | DIVF FSRC, AC<br>DIVD FSRC, AC                                   |

|                    | LOAD CONVERT                      | LDCFD FSRC, AC                                                   |

| F1                 | STORE CONVERT                     | STCFD AC, FDST<br>STCDF AC, FDST                                 |

| F2                 | CLEAR                             | CLRF FDST<br>CLRD FDST                                           |

|                    | TEST                              | TSTF FDST<br>TSTD FDST                                           |

|                    | ABSOLUTE                          | ABSF FDST<br>ABSD FDST                                           |

| F2                 | NEGATE                            | NEGF FDST<br>NEGD FDST                                           |

| F3                 | LOAD EXPONENT                     | LDEXP SRC, AC                                                    |

|                    | LOAD CONVERT INTEGER TO FLOATING  | LDCIF SRC, AC<br>LDCID SRC, AC<br>LDCLF SRC, AC<br>LDCLD SRC, AC |

|                    | STORE EXPONENT                    | STEXP AC, DST                                                    |

| F3                 | STORE CONVERT FLOATING TO INTEGER | STCFI AC, DST<br>STCFL AC, DST<br>STCDI AC, DST<br>STCDL AC, DST |

| F4                 | LOAD FP11's PROGRAM STATUS        | LDFPS SRC                                                        |

| 1                  | STORE FP11's PROGRAM STATUS       | STFPS DST                                                        |

| F4                 | STORE FP11's STATUS               | STST DST                                                         |

(continued on next page)

Table 3-1 (Cont)

Format of FP11 Instructions

| Instruction Format | Instruction                   | Mnemonic |  |

|--------------------|-------------------------------|----------|--|

| F5                 | COPY FLOATING CONDITION CODES | CFCC     |  |

|                    | SET FLOATING MODE             | SETF     |  |

| ,                  | SET INTEGER MODE              | SETI     |  |

|                    | LOAD UBREAK REGISTER          | LDUB     |  |

|                    | LOAD SHIFT COUNTER            | LDSC     |  |

|                    | STORE AR REGISTER IN ACO      | STA0     |  |

|                    | MAINTENANCE RIGHT SHIFT       | MRS      |  |

|                    | STORE QR REGISTER IN ACO      | STQ0     |  |

| e fout to ↓ e      | SET DOUBLE MODE               | SET D    |  |

| F5                 | SET LONG INTEGER MODE         | SET L    |  |

#### 3.5 INSTRUCTION SET

Table 3-2 contains the instruction set of the FP11. Some of the symbology may not be readily apparent; therefore, a brief description is given in the following paragraphs:

- a. A floating-point flip-flop, designated FD, determines whether single- or double-precision floating-point format is specified. If the flip-flop is reset, single-precision is specified and is designated by F. If the flip-flop is set, double precision is specified and is designed by D. Examples are NEG  $\underline{F}$ , NEG D, SUB D, etc.

- b. An integer flip-flop, designated IL, determines whether short-integer or long-integer format is specified. If the flip-flop is reset, short-integer format is specified and is designated by I. If the flip-flop is set, long-integer format is specified and is designated by L.

- c. Several convert type instructions use the symbology below and are defined as follows:

C<sub>IL,FD</sub> - convert integer to floating

$C_{FD,IL}$  - convert floating to integer

C<sub>F,D</sub> or C<sub>D,F</sub> - convert single-float to double-float or double-float to single-float

- d. Numbers in angle brackets indicate bit positions; an example is AR  $\langle 57:0 \rangle$ , which indicates AR bits 57 through 0.

- e. UPLIM is defined as the largest possible number that can be represented in floating-point format.

This number has an exponent of 377 and a fraction of all 1s. Note that UPLIM is dependent on the format specified. LOLIM is defined as the smallest possible number that is not identically zero.

This number has an exponent of 001 and a fraction of all 0s except for the hidden bit.

- f. Some of the octal codes listed in Table 3-2 are in the form of mathematical expressions. These octal codes can be calculated as shown in the following examples.

#### Example:

LD FPS instruction 170100+SRC

Mode 3, Register 7 specified

SRC field is equal to 37 Basic op code is 170100

SRC + basic op code is added to yield 170137.

(continued on next page)

#### Example:

LDF instruction 172400+AC\*100+FSRC AC = 2 2\*100 = 200 172400 + 200 = 172600FSRC is equal to 26 172600 + 26 = 172626 AC2, Mode 2, and Register 6 specified

#### 3.6 FP11 PROGRAMMING EXAMPLES

This paragraph shows two programming examples using the FP11 instruction set. In program example 1, A is added to B, D is subtracted from C, the quantity (A+B) is multiplied by (C-D), and the product of this multiplication is divided by X and the result stored. Example 2 calculates  $DX^3 + CX^2 + BX + A$ . This involves a three-pass loop, whereby each loop does the calculation indicated below.

$$AC0 = \underbrace{[(D*X+C)*X+B]*X+A}_{Loop 1}$$

$$Loop 3$$

$$AC0 = [DX^2 + CX + B] * X + A$$

$AC0 = DX^3 + CX^2 + BX + A$

#### Example 1:

| 666666          | 172467 | 000122          | LDF  | A → AC Ø | JLCAD ACO FROM A          |

|-----------------|--------|-----------------|------|----------|---------------------------|

| 000000 <b>4</b> | 172067 | 000122          | ADDF | B.ACO    | ;ACØ HAS (A+B)            |

| 000010          | 172567 | 000122          | LDF  | C AC1    | ;LOAD ACT FROM C          |

| 000014          | 173167 | 000122          | SUBF | D • AC 1 | ;AC1 HAS (C-D)            |

| 0000020         | 171001 |                 | MULF | AC1.AC0  | ;AC0 HAS (A+D)*(C-D)      |

| 000022          | 174467 | 000 <b>7</b> 52 | DIVE | X.ACO    | JACK HAS (A+D)*(C-D)/X    |

| 000026          | 174067 | 000752          | STF  | AC@ • Y  | ;STORE (A+D)*(C-D)/X IN Y |

#### Example 2:

| 000100 | 012700          | 000003 |       | MOV  | #3•%0            | SET UP LOCP COUNTER       |

|--------|-----------------|--------|-------|------|------------------|---------------------------|

| 000104 | 012 <b>7</b> 01 | 000146 |       | MOV  | #D+4,%1          | SET UP POINTER TO         |

|        |                 |        |       |      |                  | ; COEFFICIENTS            |

| Ø60110 | 172526          |        |       | LDF  | (6)+,AC1         | JPOP X FROM STACK         |

| 000112 | 170400          |        |       | CLRF | ACØ              | CLEAR OUT ACM             |

| 000114 | 172044          |        | LOOP; | ADDF | -(4).ACØ         | ;ADD NEXT COEFFICIENT     |

|        |                 |        |       |      |                  | TO PARTIAL RESULT         |

| 000116 | 171001          |        |       | MULF | AC1.AC0          | ; MULTIPLY PARTIAL RESULT |

|        | . ,             |        |       |      |                  | ;BY X                     |

| 060120 | 077003          |        |       | SOB  | 200P <b>LOOP</b> | ;DO LOOP 3 TIMES          |

| 000122 | 172044          |        |       | ADDF | -(4),AC0         | ;ADD X TO GET RESULT      |

| 000124 | 174046          |        |       | STF  | AC@,-(6)         | PUSH RESULT ON STACK      |

|        |                 |        |       |      |                  |                           |

Table 3-2 Instruction Set

| Mnemonic | Instruction Description                                                                                                                                                                                                                                                                                                                                                                                                 | Octal Code          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| CFCC     | Copy Floating Condition Codes<br>C ← FC<br>V ← FV                                                                                                                                                                                                                                                                                                                                                                       | 170000<br>F5 Format |

|          | $Z \leftarrow FZ$ $N \leftarrow FN$                                                                                                                                                                                                                                                                                                                                                                                     |                     |

| SETF     | Set Floating Mode $FD \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                     | 170001<br>F5 Format |

| SETI     | Set Integer Mode $FL \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                      | 170002<br>F5 Format |

|          | This instruction is a maintenance instruction in which the content of register R3 is gated into the UB register. When the control ROM address register matches the contents of the UB register, a scope sync is generated. If the FP11 is in maintenance mode (FMM=1), an interrupt is also generated and the FPU traps to the Ready state. A UB interrupt cannot be generated by the Ready state or by the states that | 170003<br>F5 Format |

|          | are used to generate the U Break interrupt.                                                                                                                                                                                                                                                                                                                                                                             |                     |

| LDSC     | Load Step Counter  This is a maintenance instruction in which the content of register R4 is gated into the step counter, if the FP11 is in maintenance mode (FMM=1). Whenever the step counter is loaded by an LDSC, normal loading via the microprogram                                                                                                                                                                | 170004<br>F5 Format |

|          | is inhibited until the step counter is incremented to zero.  This allows partial quotients and products to be formed for diagnostic purposes. If FMM=0, the LDSC acts as a NOP.                                                                                                                                                                                                                                         |                     |

Table 3-2 (Cont) Instruction Set

| Mnemonic STA0          |                                                                                                                                                                                          |                            |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| STAO                   | Instruction Description                                                                                                                                                                  | Octal Code                 |

| N N N                  | Store AR in AC0 AC0 $\langle 54:32 \rangle \leftarrow AR \langle 57:35 \rangle$ if FD = 0 AC0 $\langle 54:0 \rangle \leftarrow AR \langle 57:3 \rangle$ if FD = 1                        | 170005<br>F5 Format        |

|                        | Maintenance Right Shift $AR \leftarrow AR/2$ ; $QR \leftarrow QR/2$                                                                                                                      | 170006<br>F5 Format        |

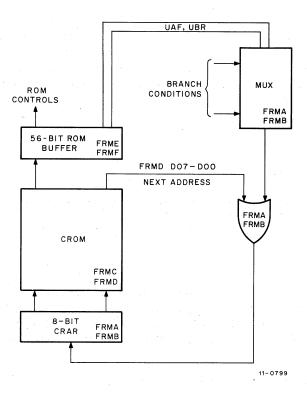

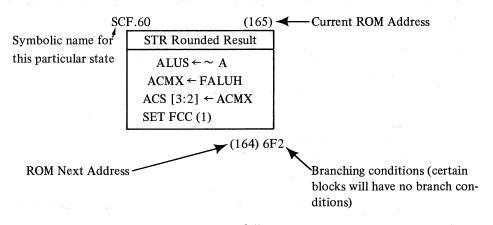

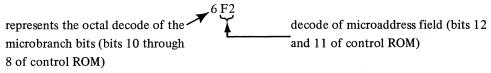

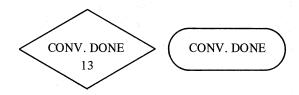

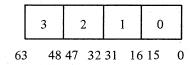

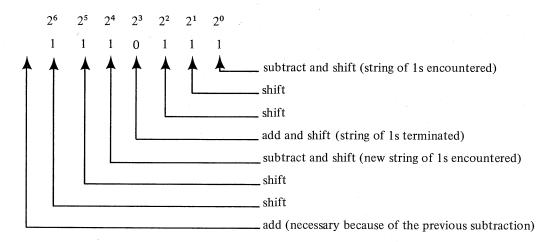

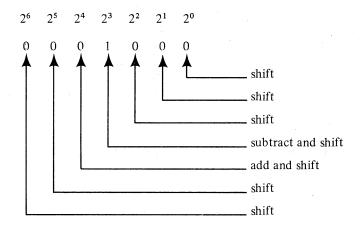

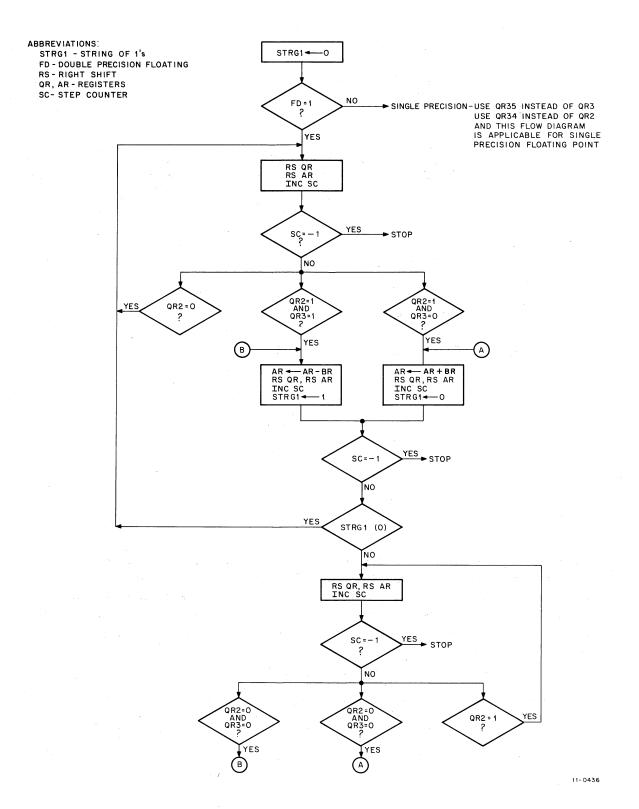

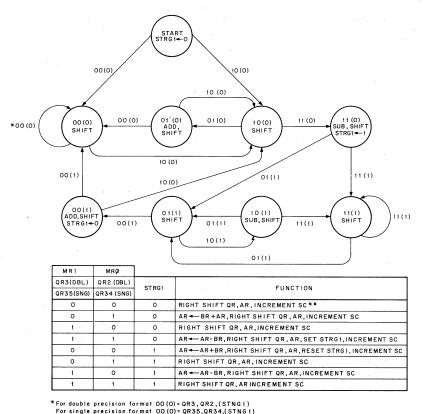

| STQ0                   | Store QR in AC0 BR $\leftarrow$ QR; AC $\langle 54:32 \rangle \leftarrow$ BR $\langle 57:35 \rangle$ if FD = 0 AC0 $\langle 54:0 \rangle \leftarrow$ BR $\langle 57:3 \rangle$ if FD = 1 | 170007<br>F5 Format        |