2340 XOR test system maintenance manual

digital equipment corporation · maynard, massachusetts-

2340 XOR test system maintenance manual

DEC-00-H2340-A-D

### Copyright © 1974 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

**DEC**

PDP

**FLIP CHIP**

**FOCAL**

**DIGITAL**

**COMPUTER LAB**

### CONTENTS

| , a fire  | rag                                      | e |

|-----------|------------------------------------------|---|

| CHAPTER 1 | GENERAL DESCRIPTION                      |   |

| 1.1       | SCOPE                                    | _ |

| 1.2       | DESCRIPTION                              | 1 |

| 1.2.1     | General                                  | 1 |

| 1.2.2     | Functional                               | 1 |

| 1.2.3     | Mechanical                               | 1 |

| 1.3       | GENERAL SPECIFICATIONS                   | 2 |

| CHAPTER 2 | INSTALLATION                             |   |

| 2.1       | SCOPE                                    | 1 |

| 2.2       | SPACE REQUIREMENTS                       | 1 |

| 2.3       | POWER REQUIREMENTS                       | 1 |

| 2.4       | UNPACKING AND INSPECTION                 | 1 |

| 2.5       | CHECKOUT AND ACCEPTANCE TESTS            | 2 |

| CHAPTER 3 | PROGRAMMING                              |   |

| 3.1       | GENERAL                                  | 1 |

| 3.2       | TYPICAL PROGRAM ADAPTER                  |   |

| CHAPTER 4 | OPERATION                                |   |

| 4.1       | SCOPE                                    | 1 |

| 4.2       | CONTROLS AND INDICATORS                  | 1 |

| 4.3       | OPERATING PROCEDURES                     | 3 |

| 4.3.1     | In Random Mode                           | 3 |

| 4.3.2     | In Program Mode                          | 5 |

| 4.4       | USE OF THE 2340 AS A MAINTENANCE TOOL 4- | 5 |

| CHAPTER 5 | THEORY OF OPERATION                      |   |

| 5.1       | SCOPE                                    | 1 |

| 5.2       | BASIC XOR PRINCIPLE OF TESTING           |   |

| 5.3       | FUNCTIONAL BLOCK DIAGRAM DISCUSSION5-    |   |

| 5.3.1     | General                                  | 1 |

| 5.3.2     | Random Mode Operation                    | _ |

| 5.3.3     | Program Mode Operation                   |   |

| 5.4       | DETAILED LOGIC DISCUSSION                |   |

| 5.4.1     | Timing                                   |   |

| 5.4.2     | Adapter Interface                        |   |

| 5.4.3     | Program Adapter                          |   |

| 5.4.4     | Random Adapter                           |   |

| 5.4.5     | Random Generators                        |   |

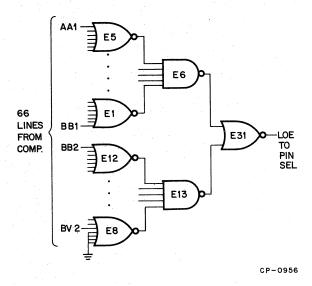

| 5.4.6     | Pin Selector                             |   |

| 5.4.7     | Comparators                              |   |

| 5.4.8     | Failure Summation                        | 7 |

### CONTENTS (Cont)

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | Page                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| C.                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | J                                                                                                                                        |

| CHAPTER 6                                                                                                                         | MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                                                                                                          |

| 6.1                                                                                                                               | SCOPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | . 6-1                                                                                                                                    |

| 6.2                                                                                                                               | TEST EQUIPMENT REQUIRED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                                                                                                                                          |

| 6.3                                                                                                                               | PREVENTIVE MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                                                                                                                                          |

| 6.3.1                                                                                                                             | Visual Inspection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                                                                                                                                          |

|                                                                                                                                   | Daily Checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                                                                                                                          |

| 6.3.2                                                                                                                             | Daily Checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | . 6-2                                                                                                                                    |

| 6.3.3                                                                                                                             | Maintenance Schedule (3 months or 5000 hours)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                                                                                                                                          |

| 6.4                                                                                                                               | CORRECTIVE MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • • • |                                                                                                                                          |

| 6.4.1                                                                                                                             | Defective Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • • • | . 6-2                                                                                                                                    |

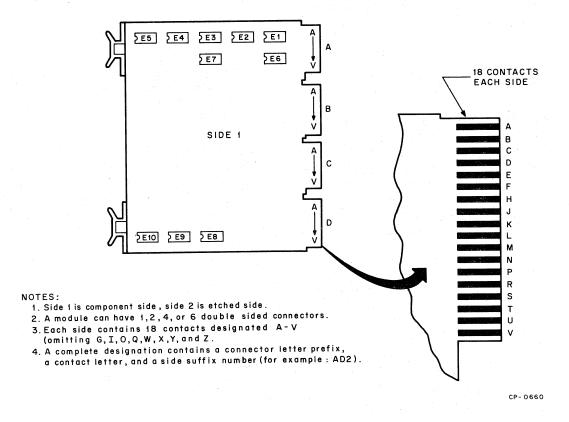

| 6.4.2                                                                                                                             | IC Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                                                                                                                          |

| 6.4.3                                                                                                                             | Repair and Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • • • | . 6-4                                                                                                                                    |

| CHAPTER 7                                                                                                                         | DRAWINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                                                                                                                                          |

| 7.1                                                                                                                               | GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | . 7-1                                                                                                                                    |

| 7.1                                                                                                                               | REFERENCED ENGINEERING DRAWINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                                                                                          |

| 7.3                                                                                                                               | LIST OF RECOMMENDED SPARES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                                                                                                                          |

| 7.5                                                                                                                               | LIST OF RECOMMENDED STARES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • • • | , ,-1                                                                                                                                    |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                                                                                          |

|                                                                                                                                   | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                                                                                                                                          |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | _                                                                                                                                        |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                                                                                          |

| Figure No.                                                                                                                        | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | Page                                                                                                                                     |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                                                                                          |

| 1-1                                                                                                                               | 2340 XOR Test System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | . 1-1                                                                                                                                    |

| 1-1<br>1-2                                                                                                                        | 2340 XOR Test System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 1-1                                                                                                                                      |

| 1-1<br>1-2<br>1-3                                                                                                                 | 2340 XOR Test System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | . 1-1<br>. 1-2<br>. 1-3                                                                                                                  |

| 1-1<br>1-2<br>1-3<br>1-4                                                                                                          | 2340 XOR Test System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 1-1<br>1-2<br>1-3<br>1-3                                                                                                                 |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5                                                                                                   | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | 1-1<br>1-2<br>1-3<br>1-3                                                                                                                 |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1                                                                                            | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | 1-1<br>1-2<br>1-3<br>1-4<br>2-1                                                                                                          |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2                                                                                     | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3                                                                                            |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3                                                                              | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment                                                                                                                                                                                                                                                                                                                                                                                               |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3                                                                                     |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1                                                                       | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module                                                                                                                                                                                                                                                                                                                                                                   |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2                                                                              |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2                                                                | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter                                                                                                                                                                                                                                                                                                                                                      |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3                                                                       |

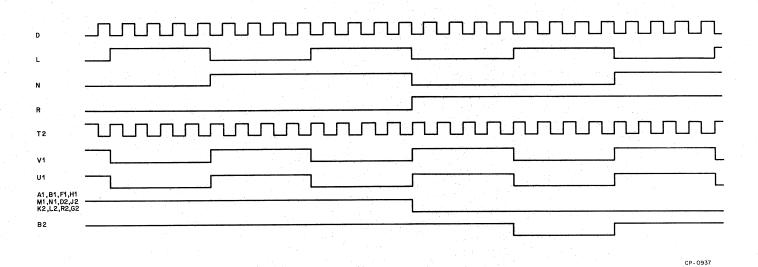

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3                                                         | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing                                                                                                                                                                                                                                                                                                                     |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3                                                                |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3<br>4-1                                                  | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators                                                                                                                                                                                                                                                                        |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3<br>4-4                                                         |

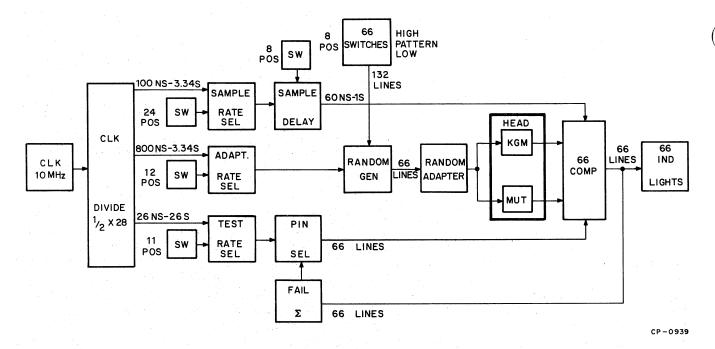

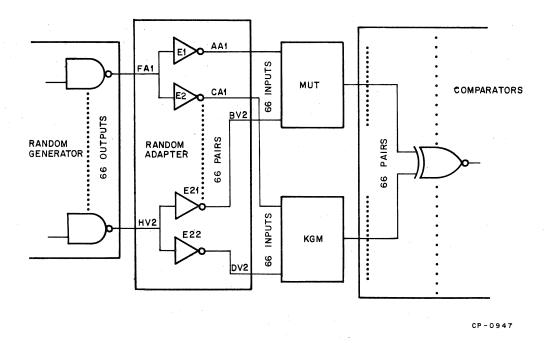

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3                                                         | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators 2340 Random Mode Functional Block Diagram                                                                                                                                                                                                                              |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3<br>4-4<br>5-2                                                  |

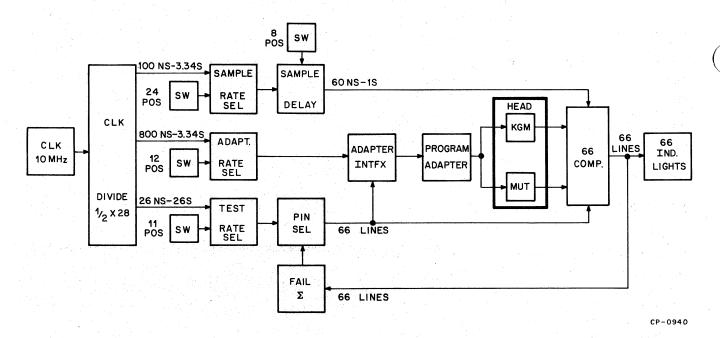

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3<br>4-1<br>5-1<br>5-2                                    | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators 2340 Random Mode Functional Block Diagram 2340 Program Mode Functional Block Diagram                                                                                                                                                                                   |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>4-4<br>5-2<br>5-2                                                  |

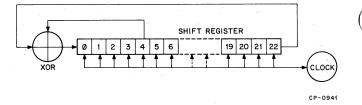

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3<br>4-1<br>5-1                                           | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators 2340 Random Mode Functional Block Diagram 2340 Program Mode Functional Block Diagram Random Generator Shift Register (Typical)                                                                                                                                         |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3<br>4-4<br>5-2<br>5-2                                           |

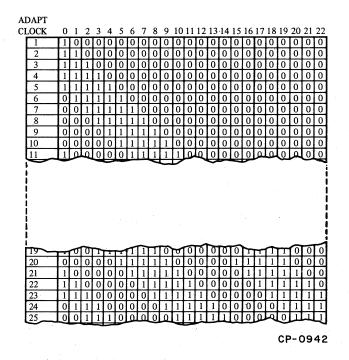

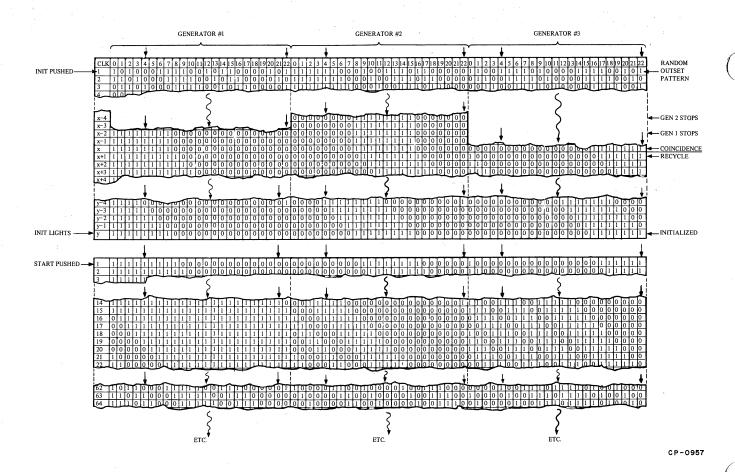

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3<br>4-1<br>5-1<br>5-2<br>5-3<br>5-4                      | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators 2340 Random Mode Functional Block Diagram 2340 Program Mode Functional Block Diagram Random Generator Shift Register (Typical) Partial Random Generator Pattern                                                                                                        |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3<br>4-4<br>5-2<br>5-2<br>5-4                                    |

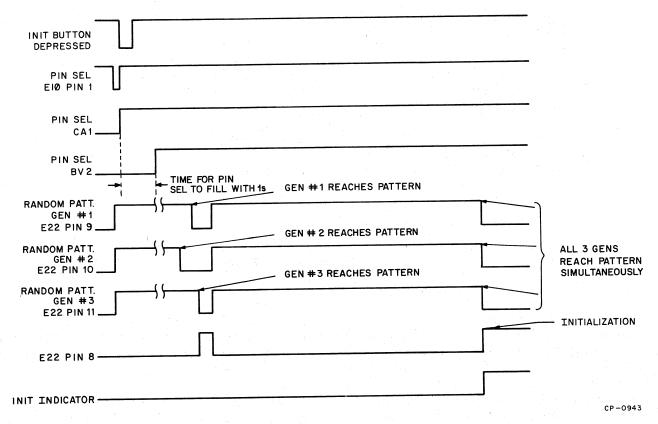

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3<br>4-1<br>5-1<br>5-2<br>5-3                             | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators 2340 Random Mode Functional Block Diagram 2340 Program Mode Functional Block Diagram Random Generator Shift Register (Typical) Partial Random Generator Pattern Random Generator Initialization Sequence                                                               |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3<br>4-4<br>5-2<br>5-4<br>5-4                                    |

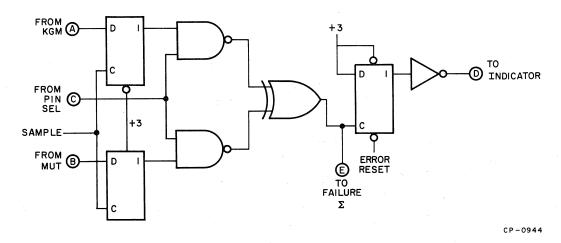

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3<br>4-1<br>5-1<br>5-2<br>5-3<br>5-4                      | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators 2340 Random Mode Functional Block Diagram 2340 Program Mode Functional Block Diagram Random Generator Shift Register (Typical) Partial Random Generator Pattern Random Generator Initialization Sequence Comparator Block Diagram                                      |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3<br>4-4<br>5-2<br>5-4<br>5-4<br>5-5<br>5-6                      |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3<br>4-1<br>5-1<br>5-2<br>5-3<br>5-4<br>5-5               | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators 2340 Random Mode Functional Block Diagram 2340 Program Mode Functional Block Diagram Random Generator Shift Register (Typical) Partial Random Generator Pattern Random Generator Initialization Sequence Comparator Block Diagram Time Select Simplified Block Diagram |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3<br>4-4<br>5-2<br>5-4<br>5-4<br>5-5<br>5-6<br>5-7               |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3<br>4-1<br>5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6        | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators 2340 Random Mode Functional Block Diagram 2340 Program Mode Functional Block Diagram Random Generator Shift Register (Typical) Partial Random Generator Pattern Random Generator Initialization Sequence Comparator Block Diagram                                      |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3<br>4-4<br>5-2<br>5-4<br>5-4<br>5-5<br>5-6<br>5-7               |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>3-1<br>3-2<br>3-3<br>4-1<br>5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7 | 2340 XOR Test System 2340 Functional Block Diagram 2340 Access Schematic 2340 Overall Dimensions 2340 Module Utilization 2340 Power Plug and Source Receptacle MUT pin AA1 Rise Time Sample Rate Adjustment Typical Program Mode Module M249 Adapter M249 Adapter M249 Adapter Timing 2340 XOR Test System Controls and Indicators 2340 Random Mode Functional Block Diagram 2340 Program Mode Functional Block Diagram Random Generator Shift Register (Typical) Partial Random Generator Pattern Random Generator Initialization Sequence Comparator Block Diagram Time Select Simplified Block Diagram |       | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>3-2<br>3-3<br>3-3<br>4-4<br>5-2<br>5-2<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9 |

### ILLUSTRATIONS (Cont)

| Figure No. | Title                                             | :  |

|------------|---------------------------------------------------|----|

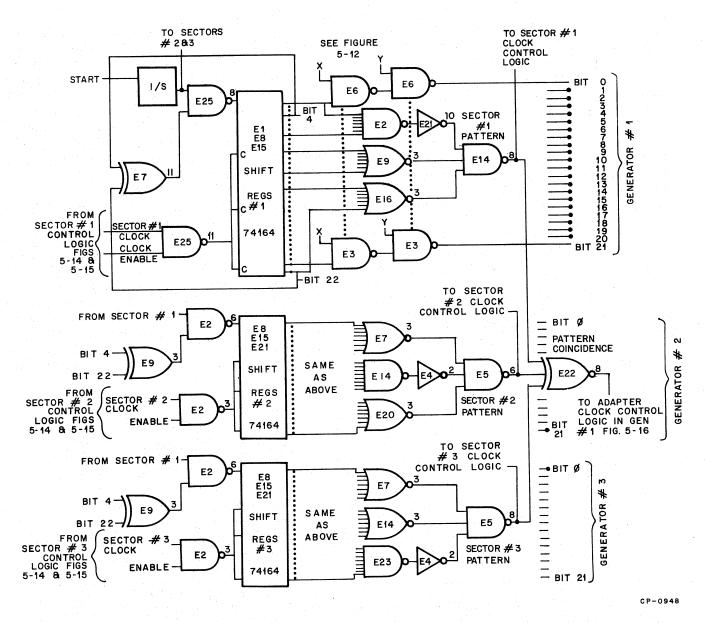

| 5-11       | Random Generators Simplified Block Diagram        | L  |

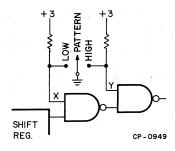

| 5-12       | Typical Front Panel Switch Arrangement            | Ĺ  |

| 5-13       | Random Generator Patterns                         | 2  |

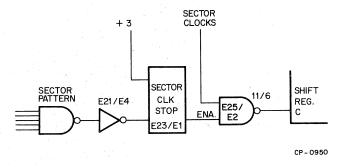

| 5-14       | Sector Clock Removal Logic                        | 3  |

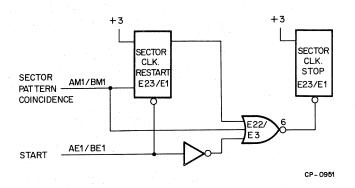

| 5-15       | Sector Clock Restoration Logic                    | 3  |

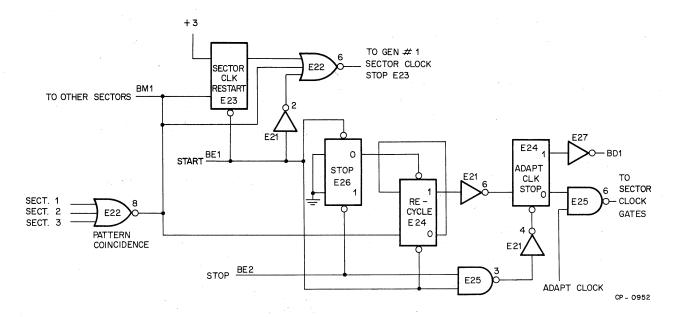

| 5-16       | Adapter Clock Removal and Restoration Logic       | ļ  |

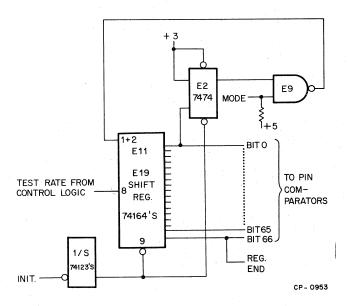

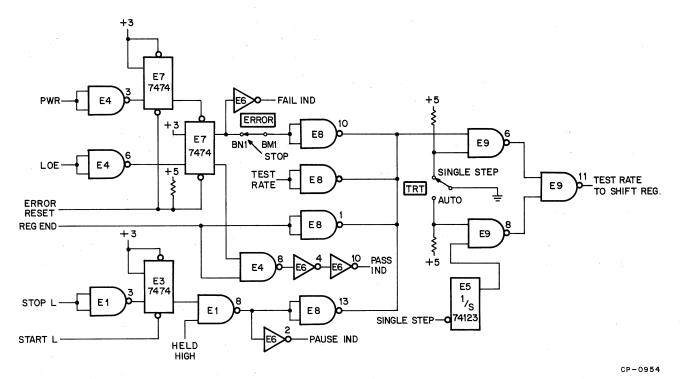

| 5-17       | Pin Selector Shift Register Logic                 | 5  |

| 5-18       | Pin Selector Control Logic                        | ś  |

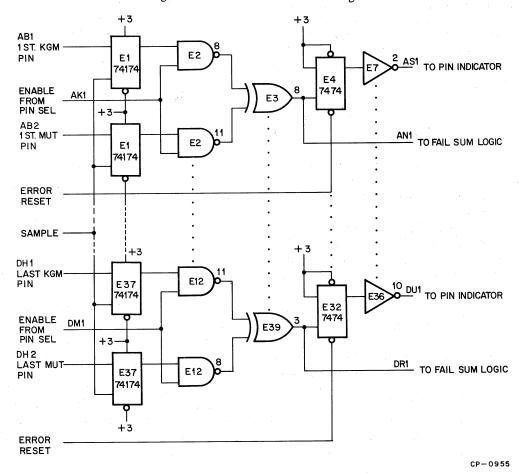

| 5-19       | XOR Comparators Block Diagram                     | 5  |

| 5-20       | Fail Sum Block Diagram                            | 7  |

| 6-1        | Physical Location of ICs on a Typical DEC Module  | 3. |

| Table No.  | TABLES  Title Pag                                 | e  |

| 14010 1 10 |                                                   |    |

| 4-1        | 2340 Controls and Indicators                      | _  |

| 4-2        | Auxiliary Test Equipment and Troubleshooting Aids | 5  |

| 5-1        | Adapter Clock Select Position/Rate                |    |

| 5-2        | Test Rate Select Position/Rate                    |    |

| 5-3        | Sample Rate Select Position/Rate                  |    |

| 6-1        | Maintenance Equipment                             |    |

| 7-1        | Referenced Engineerings Drawings                  | 1  |

| 7-2        | List of Recommended Spares                        | 1  |

# CHAPTER 1 GENERAL DESCRIPTION

#### 1.1 SCOPE

This chapter describes the 2340 XOR Test System in general terms — its purpose and use, the unit in functional terms, and provides a brief list of general specifications.

#### 1.2 DESCRIPTION

#### 1.2.1 General

The 2340 XOR Test System, (Figure 1-1) is a production line automatic test system, designed to be used in both Manufacturing and Field Service applications for comparison testing of DEC FLIP-CHIP Modules. The unit utilizes the Exclusive Or (XOR) principle to compare the outputs of a "known good module" (KGM) with the identical outputs from another module of the same type that is being tested (MUT). The same input pins on both modules are simultaneously activated and their resultant outputs are then checked on a time-margined basis. The unit is intended for testing only those modules that use positive logic at standard logic levels.

#### 1.2.2 Functional

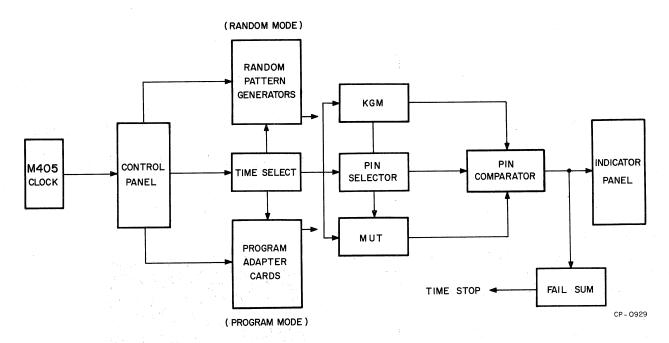

The 2340 is a stand-alone device that does not require an external computer to supply source signals. Signal generation is achieved within the tester by two modes of operation (Figure 1-2): the first is provided by pseudo-random pattern generators, the second by preprogrammed adapter cards. Timing is generated by an M405 Master Crystal Clock that controls the operation of the tester at all times.

Outputs from the two modules are strobed into the comparator by a preselected strobe. The rate and amount of delay of this strobe (or sampling period) provides a tolerance for critical timing measurements. If the output of the MUT does not coincide with the KGM during the sampling time, an error is shown on the indicator panel.

Figure 1-1 2340 XOR Test System

#### 1.2.3 Mechanical

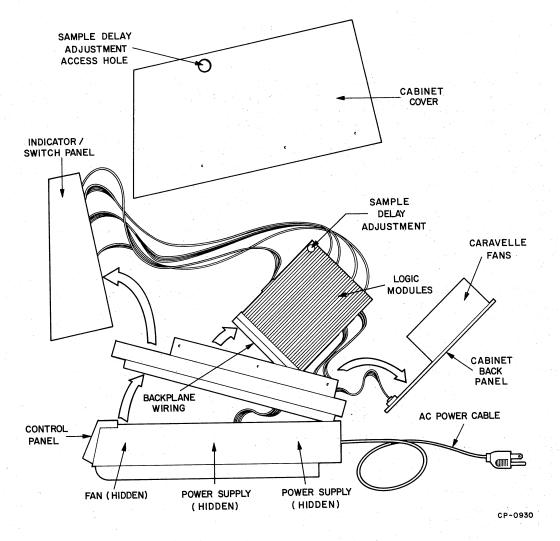

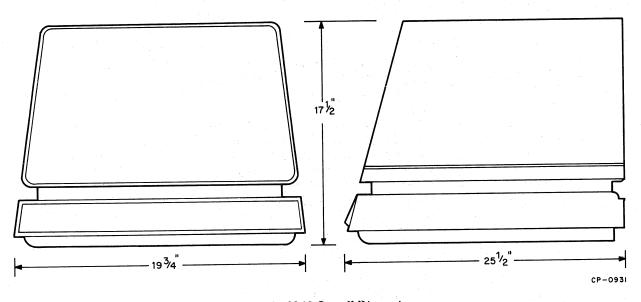

The 2340 is housed within a specially-constructed cabinet intended for bench-top use. The unit is contained within three subassemblies, each secured and hinged upon the other, providing a high degree of stability for the components while affording easy accessibility to all sections. Section accessibility is schematically illustrated in Figure 1-3. Overall cabinet dimensions are given in Figure 1-4.

Forced air cooling is supplied by two Caravelle fans, located inside the back of the unit. A separate fan is situated inside the front of the control section and supplies extra cooling for the power supplies.

Figure 1-2 2340 Functional Block Diagram

The unit contains two power supplies: the Type H740 provides the voltages needed by the indicator lamps, the Type BKF 5-5 supplies power to the logic. A single 10-ft power cord, terminated in a NEMA Type 5-15P power plug and a DEC Power Control H400-A, connects ac power to the unit.

The test head consists of 2 H851 Module Slot Connectors, 1 for the KGM and 1 for the MUT. These are double-height connectors so that double-height modules can be accommodated. Single-height modules are tested in the left-hand side of each head. The slots on each connector are connected in parallel to allow testing in any position.

Three BNC connectors, described in Table 4-1, may be used for scoping during troubleshooting procedures on a defective module.

The unit contains the following module complement. Figure 1-5 shows the Module Utilization Chart for the 2340 Test System.

#### 1.3 GENERAL SPECIFICATIONS

#### Physical

Height: 17-1/2 in. Width: 19-3/4 in. Length: 25-1/2 in.

#### Environmental

Temperature Range: +40° to +210° F Humidity: 10 to 95% Relative (no condensation)

#### **Power Requirements**

#### AC

Frequency: 47 to 63 Hz Single Phase Voltage: 95 to 130 V

#### DC

Indicators: Supplied by self-contained Type H740 Power Supply

Logic: Supplied by self-contained Type BKF 5-5 Power Supply

#### Performance

Test Cycle Time (Random Mode): 25 sec (approx.)

Range of Testing Speeds (Module): dc to 10 MHz

Testing Capacity: 100 module types are implemented

Type of Testing Fixture: 2 Type H851 Module Slot

Connector Blocks

Logic Input Requirements

Logic Type: Positive

Logic Levels: Gnd = (0) +3 = (1)

Figure 1-3 2340 Access Schematic

Figure 1-4 2340 Overall Dimensions

|    | F                                     | Е                           | D                          | C                          | В                          | Α                          |

|----|---------------------------------------|-----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| 14 | M908B KGM A<br>FROM A4 HEAD           | M908B KGM B<br>FROM C4 HEAD | G752 KGM A<br>FROM A1 HEAD | G752 KGM B<br>FROM B1 HEAD | G752 MUT A<br>FROM C1 HEAD | G752 MUT B<br>FROM D1 HEAD |

| 13 | M908B MUT A<br>FROM B4 HEAD           | M908B MUT B<br>FROM D4 HEAD | G751 KGM A<br>FROM A1 HEAD | G751 KGM B<br>FROM B1 HEAD | G751 MUT A<br>FROM C1 HEAD | G751 MUT B<br>FROM D1 HEAD |

| 12 | M405<br>CLOCK                         | M908B<br>MAJOR FUNC.        | G5001                      | PIN SELECT                 | OR                         |                            |

| 11 | M9002 TO J                            | 1 PANEL                     | G5002                      | COMPARAT                   | OR #3                      |                            |

| 9  | M9002 TO J                            | 2 PANEL                     | G5002                      | COMPARATO                  | OR #2                      |                            |

| 8  | M9002 TO J                            | 3 PANEL                     | G5002                      | COMPARATO                  | OR #1                      |                            |

| 7  | G750 KGM A<br>TO A2&A3 HEAD           | G750 KGM B<br>TO B2&B3 HEAD | G5007                      | ADAPTER IN                 | NTERFACE                   |                            |

| 6  | G750 MUT A<br>TO C2&C3 HEAD           | G750 MUT B<br>TO D2&D3 HEAD | G5006                      | RANDOM AI                  | DAPTER                     |                            |

| 4  | М9002 ТО Ј                            | 4 PANEL                     | G5005                      | RANDOM GI                  | ENERATOR #3                |                            |

| 3  | M9002 TO J                            | 5 PANEL                     | G5004                      | RANDOM GI                  | ENERATOR #2                |                            |

| 2  | M9002 TO J                            | 6 PANEL                     | G5003                      | RANDOM GI                  | ENERATOR #1                |                            |

| 1  | M908B & TEST<br>ADAPTER<br>CLOCK RATE | M908B<br>SAMPLE RATE        | G5000                      | SUMMATION                  | N & TIMING                 |                            |

FROM PANEL FUNCTION SWITCHES

Figure 1-5 2340 Module Utilization

- 1 M405 Crystal Clock Module

- 6 M908B Ribbon Cable Connector/Terminator

- 6 M9007 Bus Terminators

- 4 G750 Interface Connector Modules

- 4 G751 Interface Driver Connector Modules

- 4 G752 Interface Driver Connector Modules

- 1 G5000 Summation and Timing Module

- 1 G5001 Pin Selector Module

- 3 G5002 XOR Comparator Modules (#1, #2, #3)

- 1 G5003 Random Generator Module #1

- 1 G5004 Random Generator Module #2

- 1 G5005 Random Generator Module #3

- 1 G5006 Random Adapter Module

- 1 G5007 Adapter Interface Module

- 1 G5008 Indicator Board

- 6 M9002 Ribbon Connector Cable Module

## CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter contains installation procedures for the 2340 XOR Test System, including instructions on how to unpack the unit, and how to reinstall those unit components that were removed prior to shipment to ensure their safety. Included are checks that can be made once the System is reassembled to verify its proper operation, and tests that can be made to validate its acceptance by the user.

#### 2.2 SPACE REQUIREMENTS

The 2340 should be operated in an atmosphere relatively free of dust and corrosive fumes. The frequency of maintenance schedules is determined by the ambient operating conditions.

The degree of heat radiated by the equipment is relatively low and has no effect on the air conditioning requirements at the site.

The unit should be operated on a bench, providing proper support and power source, with sufficient space for auxiliary test equipment required when troubleshooting modules. It is recommended that the system be located in the module test area.

#### 2.3 POWER REQUIREMENTS

As listed under General Specifications (Paragraph 1.3), the 2340 is powered from a standard 3-wire, single-phase power line, properly fused to accommodate the added load it imposes. The required receptacle is a NEMA Type 5-15R, as illustrated in Figure 2-1. The unit should never be operated through a "zip-cord" type power extension, and it should never be powered from the accessory receptacle of another piece of auxiliary test equipment. Serious ground loops can be set up by this practice that could affect the accuracy of test indications.

CP-0932

Figure 2-1 2340 Power Plug and Source Receptacle

The 2340 Test System operates on ac voltages ranging from 95 V to 130 V. When inserted into a properly wired outlet, the third prong grounds the cabinet.

#### WARNING

It is dangerous to operate the tester without this ground connection.

If the integrity of the ground connection is questionable, the user is advised to measure the potential between the tester cabinet and a known ground with an ac voltmeter. If a potential exists, the circuit must be corrected before operating the tester.

#### 2.4 UNPACKING AND INSPECTION

The 2340 XOR Test System is packed in a specially designed shipping container to prevent damage during shipment. Observe any cautions printed on the container before unpacking the equipment. Proceed as follows:

- 1. Move the equipment, in its container, to the location in which it is to be used; then remove.

- 2. Save all shipping materials and the carton.

3. Remove the shipping document, affixed to the outside of the shipping carton; check it against the materials received.

#### **NOTE**

Any shortages should be noted and reported immediately to the DEC Field Service Representative.

- 4. Inspect the equipment for any obvious dents, scratches, or other shipping damage. Report this to the Field Service Representative.

- 5. Remove any polyethylene covers and/or tape from the equipment; remove any shipping hardware. Save this material.

- 6. Perform the checks listed in Paragraph 2.5.

#### 2.5 CHECKOUT AND ACCEPTANCE TESTS

Once the 2340 is unpacked and installed in its operating position, the procedures listed below should be followed to checkout and assure acceptance of the equipment. The following equipment is required for these procedures:

Tektronix 454A (or equivalent) oscilloscope Two known good modules (M115) Simpson 260 Voltohmeter W984A Module Extender Board

#### Proceed as follows:

- 1. Using a multimeter, perform a continuity test of the power wiring and check for shorts to ground on the +5 V line.

- 2. With no modules installed in any mounting frames, turn on the main power supply and check the +5 V line.

- 3. Remove power and install modules per the module utilization shown in Figure 1-5.

- Reapply power and check once again for any shorts.

- 5. Push RESET button. All lights should extinguish.

- 6. Set TEST RATE switch to position 1. Set ADAPTER CLOCK switch to position 1. Set SAMPLE RATE switch to position 4. Press START; in approximately 13 seconds the INIT light should indicate.

- 7. Turn on the +5 Vdc.

- 8. Some lights may indicate. These are erroneous and should be extinguished by pushing RESET.

- 9. On the G5000 module, put the scope probe on E42-3 and verify the rates, listed in Table 5-2, by rotating the TEST RATE switch through its positions.

- 10. On the front panel, connect the scope to the CLOCK BNC connector and verify the rates, listed in Table 5-1, by rotating the ADAPTER CLOCK switch through its positions.

- 11. On the front panel, connect the scope to the S RATE BNC connector and verify the rates, listed in Table 5-3, by rotating the SAMPLE RATE switch through its positions.

- 12. Plug two modules into the KGM and MUT test heads and verify the +5 Vdc line.

- 13. With the modules in place, verify the ground line.

- 14. With the modules in place, place all 66 front panel switches in neutral position; using the scope, verify random signals on all pins, except  $V_{cc}$  and ground pins.

- 15. With the modules in place, check corresponding pins (pin AA1 on the MUT side and pin BA1 on the KGM side). Place switch AA1 in UP position, and in the NEUTRAL and DOWN positions. Verify that pins correspond by observing the following:

| Switch   | Signals on    |

|----------|---------------|

| Position | AA1 and BA1   |

| UP       | 0 Vdc         |

| NEUTRAL  | Random Signal |

| DOWN     | +5 Vdc        |

- Repeat step 15 for all corresponding KGM and MUT pins.

- 17. Remove the modules, and on a W984A extender card, tie all pins together except V<sub>CC</sub>. Plug the W984A card into the KGM test head only. All KGM lights should indicate. This verifies all comparators and lights.

- 18. Repeat step 17 by plugging the W984A card in the MUT Test Head only. This verifies all comparators and lights. Remove the W984A card and plug the module into the MUT side.

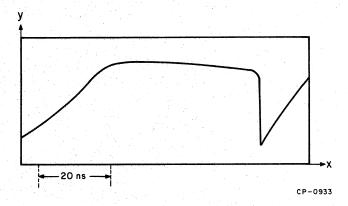

- 19. Set the oscilloscope on internal trigger and place the probe on pin AA1. Check that the rise and fall times appear as in Figure 2-2.

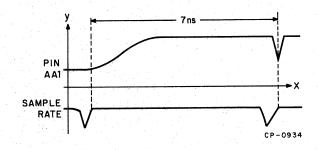

- 20. Place sync probe on KGM pin AA1. On G5000, place the other probe on either E43-8, E43-6, or E43-4. Adjust SAMPLE RATE DELAY to match the waveform in Figure 2-3.

- 21. Using the 2340 Test Procedure for M115, supplied as a separate document, set switches as indicated.

- 22. Press RESET. All erroneous panel lights should extinguish.

- 23. Press STOP. PAUSE should indicate and RUN should extinguish.

- 24. Insert an M115 in the KGM Test Head and an M115 in the MUT Test Head.

- Press CONTINUE. PASS should indicate and RUN should light.

Figure 2-2 MUT pin AA1 Rise Time

Figure 2-3 Sample Rate Adjustment

- 26. On the MUT module, ground pins AA1, AM1, AE2, AK2, AP2, and AU2. The FAIL light should indicate and RUN should blink. The error indicators for the grounded pins should indicate.

- Push both RESET and STOP. Turn off POWER and remove the modules. The procedure is complete.

# CHAPTER 3 PROGRAMMING

#### 3.1 GENERAL

Although the 2340 XOR Test System requires no programming in the traditional sense, it does require the use of *Programmed Adapter Cards*. These cards must be fabricated for each type module to be tested when the unit is operated in the Program Mode. This mode is used to test those modules containing clocks or oscillators, etc. that cannot be tested in the Random Mode.

#### 3.2 TYPICAL PROGRAM ADAPTER

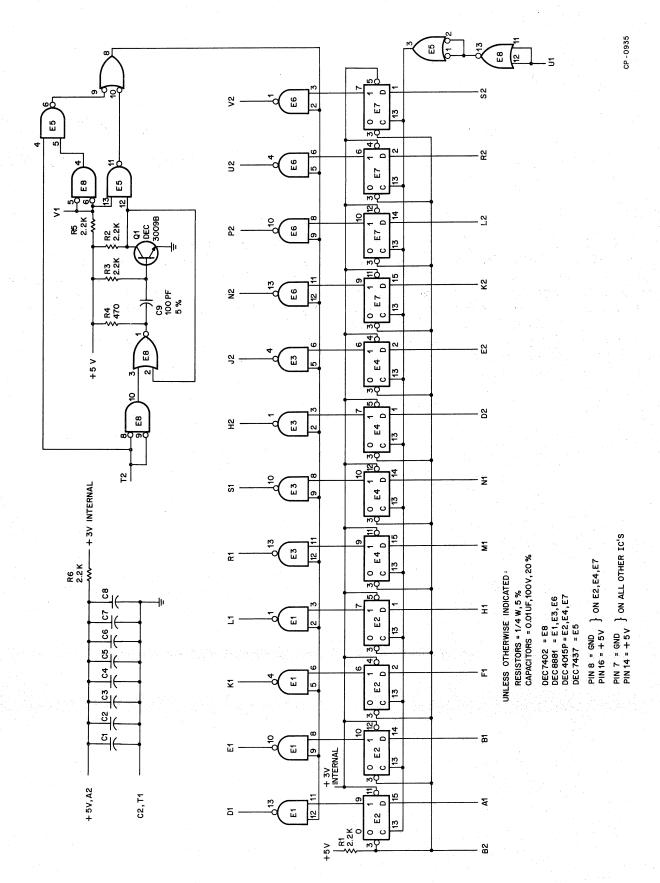

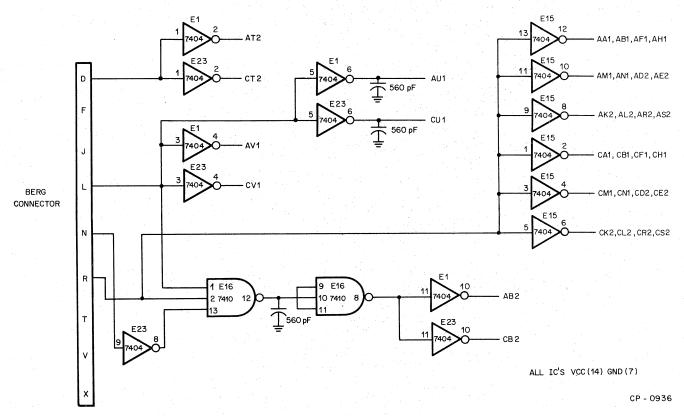

Figure 3-1 is a block diagram of a typical module to be tested in Program Mode (M249 Bus Register). Figure 3-2 illustrates an adapter to be built for testing this module; Figure 3-3 shows the adapter timing signals.

Similar cards can be constructed for other modules.

Figure 3-1 Typical Program Mode Module

Figure 3-2 M249 Adapter

Figure 3-3 M249 Adapter Timing

# CHAPTER 4 OPERATION

#### 4.1 SCOPE

This chapter discusses the operation of the 2340 XOR Test System. It contains a description of the controls and indicators used on the equipment with a tabular listing and description of each control in functional terms. The chapter also contains operational procedures to be used with the equipment and a description of its use as a maintenance tool.

#### 4.2 CONTROLS AND INDICATORS

The controls and indicators for the 2340 XOR Test System are all located on the front panel of the unit (Figure 4-1). The functions of each control and indicator are listed in Table 4-1 as keyed to Figure 4-1.

Table 4-1 2340 Controls and Indicators

| Index<br>No. | Function                                                                                                                                                                                                                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | HIGH/NEUTRAL/LOW – 66 3-position toggle switches, each pertaining to a pair of comparable module pins on both KGM and MUT, that apply either a high (output) or low level to that pin, or leave it open (Neutral) for pattern activation. For use with Random Mode of testing. |

| 2            | AA1-BV2-66 indicators, 1 for each testable pin on the modules. Each indicator bears a one-to-one positional relationship with its associated indicator. These indicators light whenever a lack of comparison is found for any comparable set of pins on KGM and MUT.           |

## Table 4-1 (Cont) 2340 Controls and Indicators

| Index<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3            | TEST RATE — An 11-position rotary switch. By rotating this switch, a specific Test Clock Rate is applied to the Pin Selector and Adapter Interface. Determines the rate at which the output pins of KGM and MUT are tested in relation to the same rate of enablement of their input pins.                                                                                                                                                |

| 4            | ADPT CLOCK – A 12-position rotary switch. By rotating this switch, a specific Adapter Clock Rate is applied to the Random Pattern Generator and to the Adapter Interface. Drives shift register generators.                                                                                                                                                                                                                               |

| 5            | SAMPLE RATE DELAY — A potentiometer adjustment (available through side panel). In conjunction with SAMPLE RATE rotary switch, moves the testing window to conform to the speed of the data.                                                                                                                                                                                                                                               |

| 6            | SAMPLE RATE – A 24-position rotary switch. By rotating this switch, a specific sampling window is applied to the sample delay circuit for application to the pin comparators. In conjunction with this adjustable delay, the specific window can be moved through the duration of test rate in the comparators. Determines the particular portion of the output signals from KGM and MUT that will be used for comparison and evaluation. |

## Table 4-1 (Cont) 2340 Controls and Indicators

## Table 4-1 (Cont) 2340 Controls and Indicators

| Index<br>No. | Function                                                                                                                                                                                                                                       | Index<br>No. | Function                                                                                                                                                                                                                  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | NOTE The following 3 entries are front panel BNC connectors. They are not controls or indicators, but                                                                                                                                          | 14           | STOP — Momentary Close<br>Pushbutton — Causes testing to stop at<br>whatever point it is situated.                                                                                                                        |

|              | provide convenient scoping references in the use of the equipment for troubleshooting.                                                                                                                                                         | 15           | MODE — SPDT toggle switch — In PROGRAM position, if the Program Adapter Card is inserted into slot A-D-6, testing will be conducted in a sequential manner as controlled by the Pin Selector. In RANDOM                   |

| . <b>7</b>   | SYNC — This is a return sync pulse from the                                                                                                                                                                                                    |              | position, if the Random Adapter Card is inserted into slot A-D-6, testing will be conducted in psuedo-random fashion, as                                                                                                  |

|              | Program Adapter Card, used as an oscilloscope clocking source for troubleshooting a defective module.                                                                                                                                          | 16           | determined by the Random Generator.  TRT – SPDT toggle switch – In AUTO                                                                                                                                                   |

| 8            | CLOCK — This is a copy of the Adapter Clock Rate as set by the front panel switch for use in troubleshooting.                                                                                                                                  | 10           | position, testing progresses at the rate determined by the Test Clock. In SINGLE STEP position, testing is stepped by the SINGLE STEP pushbutton.                                                                         |

| 9            | S RATE – Same as above, only Sample Rate.                                                                                                                                                                                                      | 17           | INIT — Momentary Close<br>Pushbutton — When depressed, causes the<br>synchronization of the 3 Random                                                                                                                      |

| 10           | POWER — Momentary Close<br>Pushbutton — Applies ac power to the 2340<br>power supplies, and dc power to the 2340                                                                                                                               |              | Generators. When accomplished, the INIT indicator will light.                                                                                                                                                             |

|              | logic. Does not apply dc to the KGM and MUT.                                                                                                                                                                                                   | 18           | ERROR – DPDT toggle switch – In STOP position, testing automatically stops on error. In BYPASS position, testing will not                                                                                                 |

| 11           | + 5 — Momentary Close<br>Pushbutton — Applies dc power to the KGM<br>and MUT, if POWER has been pushed.                                                                                                                                        |              | stop on error, but errors will accumulate in<br>the error indicators. Functions in Program<br>Mode.                                                                                                                       |

| 12           | RUN – Indicates that a test is running in either Program or Random Mode. Lights when initialization has been achieved and START is pushed, in Random Mode. In Program Mode, lights if START is pushed, or, if in Single Step operation, lights | 19           | SINGLE STEP – Momentary Close Pushbutton – Causes testing, for troubleshooting purposes, to progress one pin for each press of this button, when TRT switch is placed in SINGLE STEP position. Functions in Program Mode. |

|              | momentarily whenever SINGLE STEP is pushed. Will blink if a FAIL condition exists.                                                                                                                                                             | 20           | ERROR RESET – Momentary Close Pushbutton – Negates the error condition, causes any error indicators to extinguish. If                                                                                                     |

| 13           | START — Momentary Close Pushbutton — Causes testing to either start after initialize or to resume after it has been interrupted.                                                                                                               |              | in "Error Stop" condition, causes testing to resume, the FAIL indicator to extinguish, and the PASS indicator to light. Functions in this manner in Program Mode.                                                         |

Table 4-1 (Cont)

2340 Controls and Indicators

| Index<br>No. | Function                                                                                                                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21           | ERROR STOP – Indicates that the test cycle has been halted by an error condition, if the ERROR switch is in the STOP position.                          |

| 22           | FAIL – Indicates at the end of a cycle of tests, in Program Mode, if an error has been sensed on any set of pins.                                       |

| 23           | INIT – Lights whenever the 3 Random Generators have reached synchronism and are now ready to be used for testing.                                       |

| 24           | PASS – In Program Mode, indicates at the end of a cycle of tests that has sensed no errors. In Random Mode, will light <i>until</i> an error is sensed. |

| 25           | PAUSE – Indicates that testing has been interrupted as a result of having pressed the STOP button.                                                      |

#### 4.3 OPERATING PROCEDURES

There are two procedures for using the 2340 XOR Test System: One when in Random Mode, used for most modules, and one when in Program Mode, used to test those modules that cannot be tested in Random Mode (e.g., those containing clocks).

#### 4.3.1 In Random Mode

In this mode, the MODE switch should be positioned to RANDOM, a Random Adapter (G5006) must be installed in slot A-D-6, and the Random Generator must be initialized before testing can commence. Proceed as follows:

- 1. Press POWER. All pin error indicators will light.

- 2. Press ERROR RESET to extinguish lights.

- 3. Insert KGM in the left-hand test head and MUT in right-hand test head.

4. Position the HIGH/NEUTRAL/LOW switches (per the block schematic) for the type module being tested, e.g., set switches associated with output pins to their HIGH positions. Switches associated with input pins should be set to the NEUTRAL position. To disable any pin, set its switch to the LOW position. Set the TEST RATE, ADAPT CLOCK, and SAMPLE RATE switches to their desired positions.

#### NOTE

The ERROR and TRT switches and the SINGLE STEP button are inoperative in this mode.

- Press the +5 button to power the modules. The button will light.

- 6. Press INIT. Some error lights may come up along with FAIL on the first error; these indications should be ignored.

- 7. In about 3 seconds, the INIT lamp should light. At this time, press ERROR RESET to extinguish the erroneous error indications generated by the initialization process. The FAIL lamp should also extinguish.

- 8. When ready, press START. The PASS light should come on and RUN should indicate.

- 9. Upon the first error indication, PASS will go out and errors will accumulate in the indicators.

- 10. The generator will continue to run indefinitely.

- 11. When the desired test period has elapsed, press STOP. The RUN lamp will extinguish, the PAUSE indicator will light, and testing will cease. The same will hold true if testing is stopped and then restarted.

- 12. At this point, either commence troubleshooting procedures, if errors were detected, or, if the tester is being used to test many modules, record the errors encountered and proceed with testing the next module.

- 13. Turn off the +5 V by depressing the +5 button. The +5 button light will extinguish.

Figure 4-1 2340 XOR Test System Controls and Indicators

- 14. Insert the next module and press +5.

- 15. Repeat the procedures in steps 4 through 13.

#### 4.3.2 In Program Mode

In this mode, the MODE switch should be positioned to PROGRAM; a specially fabricated Program Adapter Board must be installed in slot A-D-6 (Paragraph 3.3). Proceed as follows:

- 1. Press POWER. All pin error indicators will light.

- 2. Press ERROR RESET to extinguish lights.

- 3. Insert KGM in the left-hand test head and MUT in the right-hand test head.

- 4. Set the TEST RATE, ADAPTER RATE, and SAMPLE RATE switches to their desired positions. Set SAMPLE RATE DELAY adjustment to its mid-point.

- 5. Press +5 to power the modules. The button will light.

- 6. Set the ERROR switch to STOP position, if it is desired to have the tester stop on each error, and to BYPASS position if not.

- 7. Set the TRT switch to SINGLE STEP position, if it is desired to manually control progress of the tests, and to AUTO position if not.

#### NOTE

The HIGH/NEUTRAL/LOW switches are inoperative in this mode.

- 8. Press START. The RUN indicator will come on. Any error indications will come up in sequence during the test cycle. If TRT is in AUTO position, and if ERROR is in STOP position, the tester will stop on every error; the ERROR and PAUSE indicators will come on and the RUN lamp will extinguish. If ERROR switch is in BYPASS position, the tester will not stop on an error, but the indications will accumulate.

- 9a. If in ERROR STOP condition, press ERROR RESET to proceed. The pin error and ERROR indications will go out and RUN will come on. If it is desired to interrupt testing, press STOP. All indications will be the same; when ready, press START.

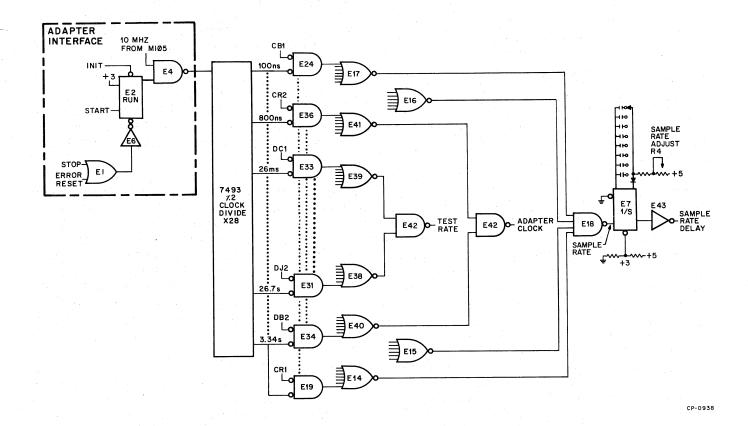

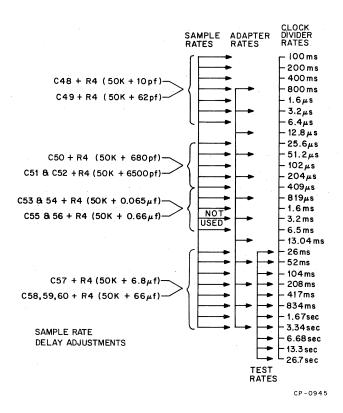

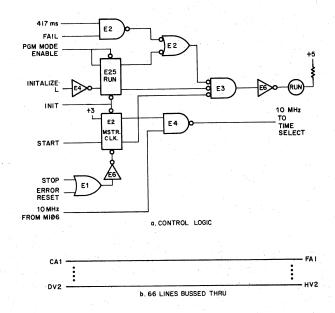

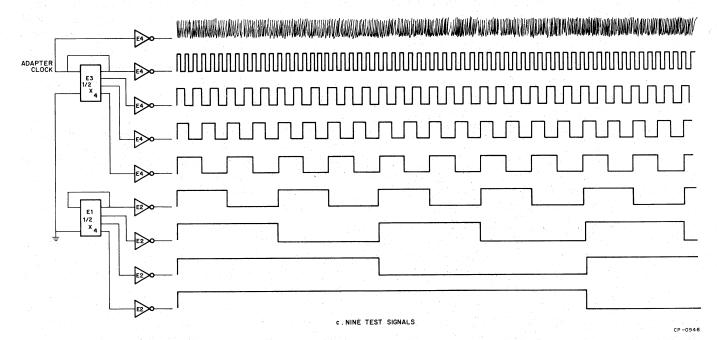

- 9b. If in ERROR BYPASS condition, the error indications will accumulate; when the last pin is tested, testing will cease. RUN will extinguish; if any errors are indicated, the ERROR indicator will be on and the FAIL lamp will light. If no errors are indicated, the PASS lamp will come on.