# processor handbook

# digital

# processor handbook

digital equipment corporation

# TABLE OF CONTENTS

| CHAPTER | 1 INTRODUCTION                                              | 1-1          |

|---------|-------------------------------------------------------------|--------------|

| 1.1     | GENERAL                                                     | 1-1          |

| 1.2     | GENERAL CHARACTERISTICS                                     | 1-2          |

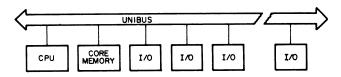

|         | 1.2.1 The UNIBUS                                            | 1-2          |

|         | 1.2.2 Central Processor                                     | 1-3          |

|         | 1.2.3 Memories                                              | 1-5          |

|         | 1.2.4 Floating Point                                        | 1-5          |

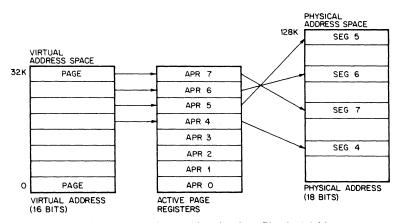

|         | 1.2.5 Memory Management                                     | 1-5          |

| 1.3     | PERIPHERALS/OPTIONS                                         | 1-5          |

|         | 1.3.1 I/O Devices                                           | 1-6          |

|         | 1.3.2 Storage Devices                                       | 1-6          |

|         | 1.3.3 Bus Options                                           | 1-6          |

| 1.4     | SOFTWARE                                                    | 1-6          |

|         | 1.4.1 Paper Tape Software                                   | 1-7          |

|         | 1.4.2 Disk Operating System Software                        | 1-7          |

|         | 1.4.3 Higher Level Languages                                | 1-7          |

| 1.5     | NUMBER SYSTEMS                                              | 1-7          |

| CHAPTER | 2 SYSTEM ARCHITECTURE                                       | 2-1          |

| 2.1     | SYSTEM DEFINITION                                           | 2-1          |

| 2.2     | UNIBUS                                                      | 2-1          |

|         | 2.2.1 Bidirectional Lines                                   | 2-1          |

|         | 2.2.2 Master-Slave Relation 2.2.3 Interlocked Communication | 2-2<br>2-2   |

| 2.3     | CENTRAL PROCESSOR                                           | 2-2          |

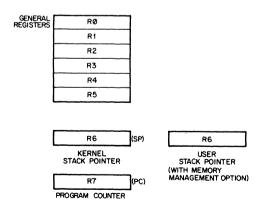

| 2.5     | 2.3.1 General Registers                                     | 2-3          |

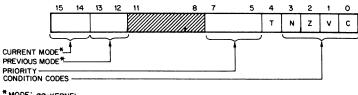

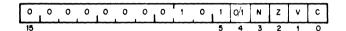

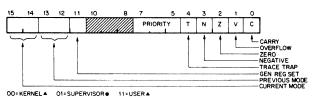

|         | 2.3.2 Processor Status Word                                 | 2.4          |

|         | 2.3.3 Stack Limit Register                                  | 2-5          |

| 2.4     | EXTENDED INSTRUCTION SET & FLOATING POINT                   | 2-5          |

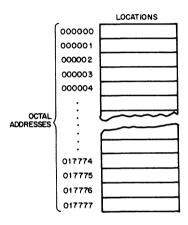

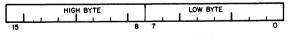

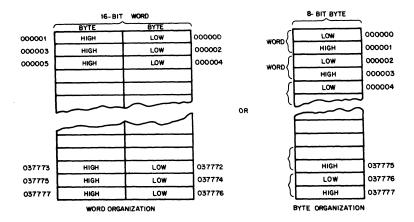

| 2.5     | CORE MEMORY                                                 | 2.6          |

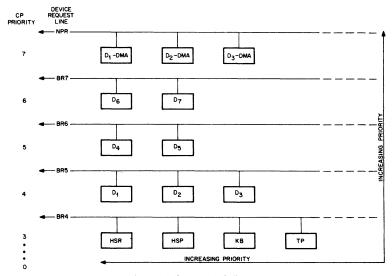

| 2.6     | AUTOMATIC PRIORITY INTERRUPTS                               | 2-7          |

|         | 2.6.1 Using the Interrupts 2.6.2 Interrupt Procedure        | 2.9<br>2.9   |

|         | 2.6.3 Interrupt Servicing                                   | 2-10         |

| 2.7     | PROCESSOR TRAPS                                             | 2-10         |

| -       | 2.7.1 Power Failure                                         | 2-10         |

|         | 2.7.2 Odd Addressing Errors                                 | 2-10         |

|         | 2.7.3 Time-out Errors                                       |              |

|         |                                                             |              |

|         | 2.7.4 Reserved Instructions 2.7.5 Trap Handling             | 2-11<br>2-11 |

| 3.2 DOUBLE OPERAND ADDRESSING 3.3 DIRECT ADDRESSING 3.3.1 Register Mode 3.3.2 Auto-increment Mode 3.3.3 Auto-decrement Mode 3.3.4 Index Mode 3.3.4 Index Mode 3.3.5 USE OF THE PC AS A GENERAL REGISTER 3.5.1 Immediate Mode 3.5.2 Absolute Addressing 3.5.4 Relative Addressing 3.5.5 USE OF STACK POINTER AS GENERAL REGISTER 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 3.7.2 Program Counter Addressing 3.7.4 SINGLE OPERAND INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.4.5 DOUBLE OPERAND INSTRUCTIONS 4.4.6 PROGRAM CONTROL INSTRUCTIONS 4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS  CHAPTER 5 PROGRAMMING TECHNIQUES 5.1 THE STACK 5.2 SUBROUTINE LINKAGE 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3.1 General Principles 5.3.1 General Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CHAPIER . | 3 ADDRESSING MODES                  | 3-1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------|------|

| 3.2 DOUBLE OPERAND ADDRESSING 3.3 DIRECT ADDRESSING 3.3.1 Register Mode 3.3.2 Auto-increment Mode 3.3.3 Auto-decrement Mode 3.3.4 Index Mode 3.3.4 Index Mode 3.3.5 USE OF THE PC AS A GENERAL REGISTER 3.5.1 Immediate Mode 3.5.2 Absolute Addressing 3.5.4 Relative Addressing 3.5.5 USE OF STACK POINTER AS GENERAL REGISTER 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 3.7.2 Program Counter Addressing 3.7.4 SINGLE OPERAND INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.4.5 DOUBLE OPERAND INSTRUCTIONS 4.4.6 PROGRAM CONTROL INSTRUCTIONS 4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS  CHAPTER 5 PROGRAMMING TECHNIQUES 5.1 THE STACK 5.2 SUBROUTINE LINKAGE 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3.1 General Principles 5.3.1 General Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.1       | SINGLE OPERAND ADDRESSING           | 3.2  |

| 3.3 DIRECT ADDRESSING 3.3.1 Register Mode 3.3.2 Auto-increment Mode 3.3.3 Auto-decrement Mode 3.3.3 Auto-decrement Mode 3.3.4 Index Mode 3.3.5 USE OF THE PC AS A GENERAL REGISTER 3.5.1 Immediate Mode 3.5.2 Absolute Addressing 3.5.3 Relative Addressing 3.5.4 Relative Deferred Addressing 3.5.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 3.7.2 Program Counter Addressing 3.7.4 Relative Deferred Addressing 3.7.5 SUMMARY OF ADDRESSING MODES 3.7.6 General Register Addressing 3.7.7 Program Counter Addressing 3.7.8 LIST OF INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.5 DOUBLE OPERAND INSTRUCTIONS 4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS  CHAPTER 5 PROGRAMMING TECHNIQUES 5.1 THE STACK 5.2 SUBROUTINE LINKAGE 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3.1 General Principles 5.3.1 General Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                     | 3-2  |

| 3.3.1 Register Mode 3.3.2 Auto-increment Mode 3.3.3 Auto-decrement Mode 3.3.3 Auto-decrement Mode 3.3.4 Index Mode 3.3.4 DEFERRED (INDIRECT) ADDRESSING 3.5 USE OF THE PC AS A GENERAL REGISTER 3.5.1 Immediate Mode 3.5.2 Absolute Addressing 3.5.3 Relative Addressing 3.5.4 Relative Deferred Addressing 3.5.5 POSITION SET 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 3.7.2 Program Counter Addressing 3.7.4 INTRODUCTION 4.2 INSTRUCTION SET 4.1 INTRODUCTION 4.4 SINGLE OPERAND INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.5 DOUBLE OPERAND INSTRUCTIONS 4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS 5.1 THE STACK 5.2 SUBROUTINE LINKAGE 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3 INTERRUPTS 5.3.1 General Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3       |                                     | 3-4  |

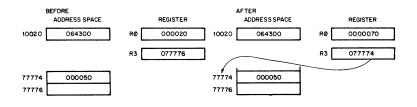

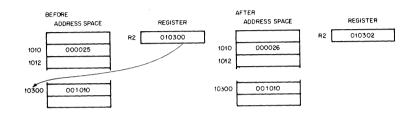

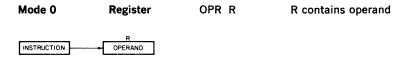

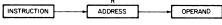

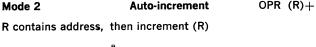

| 3.3.2 Auto-increment Mode 3.3.3 Auto-decrement Mode 3.3.3 Auto-decrement Mode 3.3.4 Index Mode 3.3.4 Index Mode 3.5.1 DEFERRED (INDIRECT) ADDRESSING 3.5.1 Immediate Mode 3.5.1 Immediate Mode 3.5.2 Absolute Addressing 3.5.3 Relative Addressing 3.5.4 Relative Deferred Addressing 3.5.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 3.7.2 Program Cou |           |                                     | 3-4  |

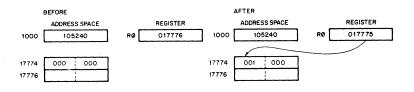

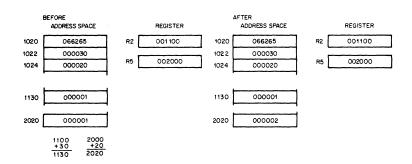

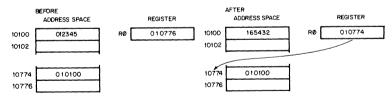

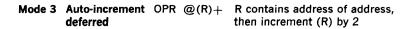

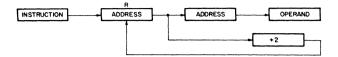

| 3.3.3 Auto-decrement Mode 3.3.4 Index Mode 3.3.4 Index Mode 3.5 USE OF THE PC AS A GENERAL REGISTER 3.5.1 Immediate Mode 3.5.2 Absolute Addressing 3.5.3 Relative Addressing 3.5.4 Relative Deferred Addressing 3.5.5 USE OF STACK POINTER AS GENERAL REGISTER 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 3.7.2 Program Counter Addressing 3.7.4 INTRODUCTION 4.2 INSTRUCTION SET 4.1 INTRODUCTION 4.2 INSTRUCTION FORMATS 4.3 LIST OF INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.5 DOUBLE OPERAND INSTRUCTIONS 4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS 4.7 MISCELLANEOUS 5.1 THE STACK 5.2 SUBROUTINE LINKAGE 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3.1 General Principles 5.3.1 Reenar Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                     | 3-5  |

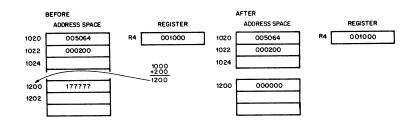

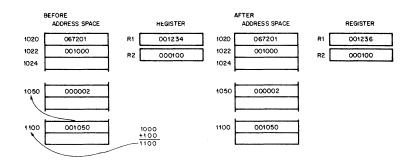

| 3.3.4 Index Mode  3.4 DEFERRED (INDIRECT) ADDRESSING  3.5 USE OF THE PC AS A GENERAL REGISTER  3.5.1 Immediate Mode  3.5.2 Absolute Addressing  3.5.3 Relative Addressing  3.5.4 Relative Deferred Addressing  3.6 USE OF STACK POINTER AS GENERAL REGISTER  3.7 SUMMARY OF ADDRESSING MODES  3.7.1 General Register Addressing  3.7.2 Program Counter Addressing  3.7.2 Program Counter Addressing  3.6 USE OF STACK POINTER AS GENERAL REGISTER  3.7 SUMMARY OF ADDRESSING MODES  3.7.1 General Register Addressing  3.7.2 Program Counter Addressing  3.6 USE OF INSTRUCTION SET  4.1 INTRODUCTION  4.2 INSTRUCTION FORMATS  4.3 LIST OF INSTRUCTIONS  4.4 SINGLE OPERAND INSTRUCTIONS  4.5 DOUBLE OPERAND INSTRUCTIONS  4.6 PROGRAM CONTROL INSTRUCTIONS  4.7 MISCELLANEOUS  5.1 THE STACK  5.2 SUBROUTINE LINKAGE  5.2.1 Subroutine Calls  5.2.2 Argument Transmission  5.2.3 Subroutine Return  5.2.4 PDP-11 Subroutine Advantage  5.3.1 INTERRUPTS  5.3.1 General Principles  5.3.2 Nesting  5.4 REENTRANCY  5.5 POSITION INDEPENDENT CODE  5.5 POSITION INDEPENDENT CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | 3.3.3 Auto-decrement Mode           | 3-7  |

| 3.4 DEFERRED (INDIRECT) ADDRESSING 3.5 USE OF THE PC AS A GENERAL REGISTER 3.5.1 Immediate Mode 3.5.2 Absolute Addressing 3.5.3 Relative Addressing 3.5.4 Relative Deferred Addressing 3.5.5 Relative Deferred Addressing 3.6 USE OF STACK POINTER AS GENERAL REGISTER 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 3.7.2 Program Counter Addressing 3.7.4 INTRODUCTION 4.1 INTRODUCTION 4.2 INSTRUCTION FORMATS 4.3 LIST OF INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.5 DOUBLE OPERAND INSTRUCTIONS 4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS  5.1 THE STACK 5.2 SUBROUTINE LINKAGE 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3 INTERRUPTS 5.3.1 General Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 5.5 POSITION INDEPENDENT CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                     | 3-8  |

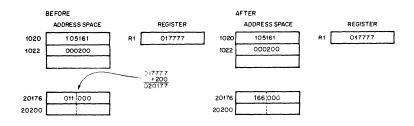

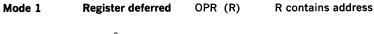

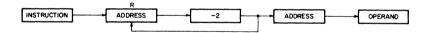

| 3.5       USE OF THE PC AS A GENERAL REGISTER       3.5.1 Immediate Mode       3.5.2 Absolute Addressing       3.5.2 Absolute Addressing       3.5.2 Absolute Addressing       3.5.3 Relative Addressing       3.5.4 Relative Deferred Addressing       3.5.4 Relative Deferred Addressing       3.5.4 Relative Deferred Addressing       3.5.4 Relative Deferred Addressing       3.7.2 SUMMARY OF ADDRESSING MODES       3.7.1 General Register Addressing       3.3.7.1 General Register Addressing       3.3.7.2 Program Counter Addressing       4.4.4 Program Counter Addressing       5.5.2 Program Counter Ad                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.4       |                                     | 3-10 |

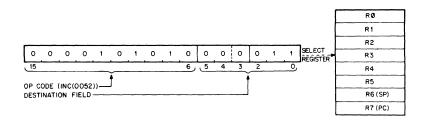

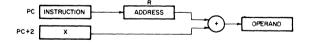

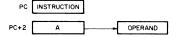

| 3.5.1 Immediate Mode 3.5.2 Absolute Addressing 3.5.3 Relative Addressing 3.5.4 Relative Deferred Addressing 3.5.4 Relative Deferred Addressing 3.5.5 USE OF STACK POINTER AS GENERAL REGISTER 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 3.7.2 Program Counter Addressing 3.7.4 INTRODUCTION 4.1 INTRODUCTION 4.2 INSTRUCTION FORMATS 4.3 LIST OF INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.5 DOUBLE OPERAND INSTRUCTIONS 4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS  CHAPTER 5 PROGRAMMING TECHNIQUES 5.1 THE STACK 5.2 SUBROUTINE LINKAGE 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3 INTERRUPTS 5.3.1 General Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | USE OF THE PC AS A GENERAL REGISTER | 3-12 |

| 3.5.2 Absolute Addressing 3.5.3 Relative Addressing 3.5.4 Relative Deferred Addressing 3.5.4 Relative Deferred Addressing 3.6 USE OF STACK POINTER AS GENERAL REGISTER 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressin | 0.0       |                                     | 3-13 |

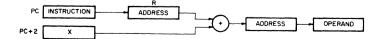

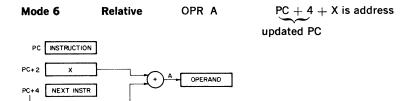

| 3.5.3 Relative Addressing 3.5.4 Relative Deferred Addressing 3.5.4 Relative Deferred Addressing 3.6 USE OF STACK POINTER AS GENERAL REGISTER 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 4.4 INTRODUCTION 4.2 INSTRUCTION SPORMATS 4.3 LIST OF INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.4 SINGLE OPERAND INSTRUCTIONS 4.5 DOUBLE OPERAND INSTRUCTIONS 4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS 4.7 MISCELLANEOUS 5.1 THE STACK 5.2 SUBROUTINE LINKAGE 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.2 Argument Transmission 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3.1 INTERRUPTS 5.3.1 General Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                     | 3-13 |

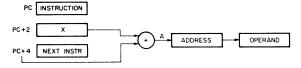

| 3.5.4 Relative Deferred Addressing 3.6 USE OF STACK POINTER AS GENERAL REGISTER 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 4.1 INTRODUCTION 4.4.1 INTRODUCTION 4.4.2 INSTRUCTION 5.4.4.4 SINGLE OPERAND INSTRUCTIONS 4.4.4 SINGLE OPERAND INSTRUCTIONS 4.5 DOUBLE OPERAND INSTRUCTIONS 4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS 4.7 MISCELLANEOUS 5.1 THE STACK 5.2 SUBROUTINE LINKAGE 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3.1 General Principles 5.3.1 General Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                                     | 3-14 |

| 3.6 USE OF STACK POINTER AS GENERAL REGISTER 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 4.1 INTRODUCTION 4.4.1 INTRODUCTION 4.4.2 INSTRUCTION 4.4.4 SINGLE OPERAND INSTRUCTIONS 4.4.5 DOUBLE OPERAND INSTRUCTIONS 4.4.6 PROGRAM CONTROL INSTRUCTIONS 4.7 MISCELLANEOUS 4.7 MISCELLANEOUS 5.2.1 Subroutine Calls 5.2.2 Argument Transmission 5.2.3 Subroutine Calls 5.2.3 Subroutine Return 5.2.4 PDP-11 Subroutine Advantage 5.3.1 INTERRUPTS 5.3.1 General Principles 5.3.2 Nesting 5.4 REENTRANCY 5.5 POSITION INDEPENDENT CODE 5.5.5 POSITION INDEPENDENT CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                     | 3-15 |

| 3.7 SUMMARY OF ADDRESSING MODES 3.7.1 General Register Addressing 3.7.2 Program Counter Addressing 4.0 INSTRUCTION S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.6       |                                     | 3-16 |

| 3.7.1 General Register Addressing 3.3.7.2 Program Counter Addressing 3.3.2 Program Counter Addressing 3.3.3.2 Program Counter Addressing 3.3.3.2 Program Counter Addressing 3.3.3.3.3.3.2 Program Counter Addressing 3.3.3.3.3.3.3.3.3.3.3.3.3.3.3.3.3.3.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                     | 3-16 |

| 3.7.2 Program Counter Addressing 3-  CHAPTER 4 INSTRUCTION SET 4-  4.1 INTRODUCTION 4- 4.2 INSTRUCTION FORMATS 4- 4.3 LIST OF INSTRUCTIONS 4- 4.4 SINGLE OPERAND INSTRUCTIONS 4- 4.5 DOUBLE OPERAND INSTRUCTIONS 4- 4.6 PROGRAM CONTROL INSTRUCTIONS 4- 4.7 MISCELLANEOUS 5-  5.1 THE STACK 5- 5.2 SUBROUTINE LINKAGE 5- 5.2.1 Subroutine Calls 5- 5.2.2 Argument Transmission 5- 5.2.3 Subroutine Return 5- 5.2.4 PDP-11 Subroutine Advantage 5- 5.3 INTERRUPTS 5- 5.3.1 General Principles 5- 5.3.2 Nesting 5- 5.4 REENTRANCY 5- 5.5 POSITION INDEPENDENT CODE 5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.7       | 3.7.1 General Register Addressing   | 3-16 |

| ### CHAPTER 4 INSTRUCTION SET   4-  4.1 INTRODUCTION   4- 4.2 INSTRUCTION FORMATS   4- 4.3 LIST OF INSTRUCTIONS   4- 4.4 SINGLE OPERAND INSTRUCTIONS   4- 4.5 DOUBLE OPERAND INSTRUCTIONS   4- 4.6 PROGRAM CONTROL INSTRUCTIONS   4- 4.7 MISCELLANEOUS   4-  **CHAPTER 5 PROGRAMMING TECHNIQUES   5- 5.2 SUBROUTINE LINKAGE   5- 5.2.1 Subroutine Calls   5- 5.2.2 Argument Transmission   5- 5.2.3 Subroutine Return   5- 5.2.4 PDP-11 Subroutine Advantage   5- 5.3.1 General Principles   5- 5.3.2 Nesting   5- 5.3.2 Nesting   5- 5.4 REENTRANCY   5- 5.5 POSITION INDEPENDENT CODE   5-  5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5.5 POSITION INDEPENDENT CODE   5- 5. |           |                                     |      |

| 4.1 INTRODUCTION       4-         4.2 INSTRUCTION FORMATS       4-         4.3 LIST OF INSTRUCTIONS       4-         4.4 SINGLE OPERAND INSTRUCTIONS       4-         4.5 DOUBLE OPERAND INSTRUCTIONS       4-         4.6 PROGRAM CONTROL INSTRUCTIONS       4-         4.7 MISCELLANEOUS       4-          5.1 THE STACK       5         5.2 SUBROUTINE LINKAGE       5         5.2.1 Subroutine Calls       5         5.2.2 Argument Transmission       5         5.2.3 Subroutine Return       5         5.2.4 PDP-11 Subroutine Advantage       5         5.3 INTERRUPTS       5         5.3.1 General Principles       5         5.3.2 Nesting       5         5.4 REENTRANCY       5         5.5 POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                     | 0.10 |

| 4.1 INTRODUCTION       4-         4.2 INSTRUCTION FORMATS       4-         4.3 LIST OF INSTRUCTIONS       4-         4.4 SINGLE OPERAND INSTRUCTIONS       4-         4.5 DOUBLE OPERAND INSTRUCTIONS       4-         4.6 PROGRAM CONTROL INSTRUCTIONS       4-         4.7 MISCELLANEOUS       4-          5.1 THE STACK       5         5.2 SUBROUTINE LINKAGE       5         5.2.1 Subroutine Calls       5         5.2.2 Argument Transmission       5         5.2.3 Subroutine Return       5         5.2.4 PDP-11 Subroutine Advantage       5         5.3 INTERRUPTS       5         5.3.1 General Principles       5         5.3.2 Nesting       5         5.4 REENTRANCY       5         5.5 POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                     |      |

| 4.2 INSTRUCTION FORMATS       4-         4.3 LIST OF INSTRUCTIONS       4-         4.4 SINGLE OPERAND INSTRUCTIONS       4-         4.5 DOUBLE OPERAND INSTRUCTIONS       4-         4.6 PROGRAM CONTROL INSTRUCTIONS       4-         4.7 MISCELLANEOUS       4-         CHAPTER 5 PROGRAMMING TECHNIQUES       5         5.1 THE STACK       5         5.2 SUBROUTINE LINKAGE       5         5.2.1 Subroutine Calls       5         5.2.2 Argument Transmission       5         5.2.3 Subroutine Return       5         5.2.4 PDP-11 Subroutine Advantage       5         5.3 INTERRUPTS       5         5.3.1 General Principles       5         5.3.2 Nesting       5         5.4 REENTRANCY       5         5.5 POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CHAPTER   | 4 INSTRUCTION SET                   | 4-1  |

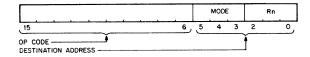

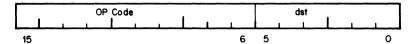

| 4.2 INSTRUCTION FORMATS       4-         4.3 LIST OF INSTRUCTIONS       4-         4.4 SINGLE OPERAND INSTRUCTIONS       4-         4.5 DOUBLE OPERAND INSTRUCTIONS       4-         4.6 PROGRAM CONTROL INSTRUCTIONS       4-         4.7 MISCELLANEOUS       4-         CHAPTER 5 PROGRAMMING TECHNIQUES       5         5.1 THE STACK       5         5.2 SUBROUTINE LINKAGE       5         5.2.1 Subroutine Calls       5         5.2.2 Argument Transmission       5         5.2.3 Subroutine Return       5         5.2.4 PDP-11 Subroutine Advantage       5         5.3 INTERRUPTS       5         5.3.1 General Principles       5         5.3.2 Nesting       5         5.4 REENTRANCY       5         5.5 POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.1       | INTRODUCTION                        | 4 1  |

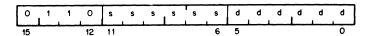

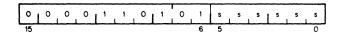

| 4.3       LIST OF INSTRUCTIONS       4-         4.4       SINGLE OPERAND INSTRUCTIONS       4-         4.5       DOUBLE OPERAND INSTRUCTIONS       4-         4.6       PROGRAM CONTROL INSTRUCTIONS       4-         4.7       MISCELLANEOUS       4-          CHAPTER 5       PROGRAMMING TECHNIQUES       5         5.1       THE STACK       5         5.2       SUBROUTINE LINKAGE       5         5.2.1       Subroutine Calls       5         5.2.2       Argument Transmission       5         5.2.3       Subroutine Return       5         5.2.4       PDP-11       Subroutine Advantage       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                     |      |

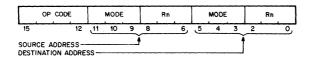

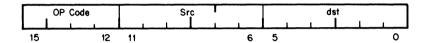

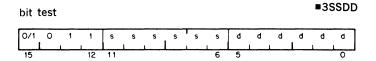

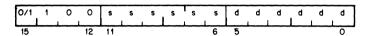

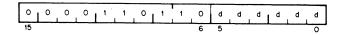

| 4.4       SINGLE OPERAND INSTRUCTIONS       4-         4.5       DOUBLE OPERAND INSTRUCTIONS       4-         4.6       PROGRAM CONTROL INSTRUCTIONS       4-         4.7       MISCELLANEOUS       4-         CHAPTER 5       PROGRAMMING TECHNIQUES       5-         5.1       THE STACK       5-         5.2       SUBROUTINE LINKAGE       5-         5.2.1       Subroutine Calls       5-         5.2.2       Argument Transmission       5-         5.2.3       Subroutine Return       5-         5.2.4       PDP-11       Subroutine Advantage       5-         5.3       INTERRUPTS       5-         5.3.1       General Principles       5-         5.3.2       Nesting       5-         5.4       REENTRANCY       5-         5.5       POSITION INDEPENDENT CODE       5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                     |      |

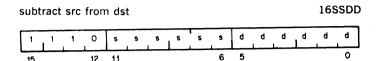

| 4.5       DOUBLE OPERAND INSTRUCTIONS       4-         4.6       PROGRAM CONTROL INSTRUCTIONS       4-         4.7       MISCELLANEOUS       4-         CHAPTER 5       PROGRAMMING TECHNIQUES       5         5.1       THE STACK       5         5.2       SUBROUTINE LINKAGE       5         5.2.1       Subroutine Calls       5         5.2.2       Argument Transmission       5         5.2.3       Subroutine Return       5         5.2.4       PDP-11 Subroutine Advantage       5         5.3       INTERRUPTS       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | CINCLE OPERAND INCEDITIONS          |      |

| 4.6       PROGRAM CONTROL INSTRUCTIONS       4-         4.7       MISCELLANEOUS       4-         CHAPTER 5       PROGRAMMING TECHNIQUES       5         5.1       THE STACK       5         5.2       SUBROUTINE LINKAGE       5         5.2.1       Subroutine Calls       5         5.2.2       Argument Transmission       5         5.2.3       Subroutine Return       5         5.2.4       PDP-11       Subroutine Advantage       5         5.3       INTERRUPTS       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | DOUBLE OPERAND INSTRUCTIONS         | 4.0  |

| 4.7 MISCELLANEOUS       4-         CHAPTER 5 PROGRAMMING TECHNIQUES       5         5.1 THE STACK       5         5.2 SUBROUTINE LINKAGE       5         5.2.1 Subroutine Calls       5         5.2.2 Argument Transmission       5         5.2.3 Subroutine Return       5         5.2.4 PDP-11 Subroutine Advantage       5         5.3 INTERRUPTS       5         5.3.1 General Principles       5         5.3.2 Nesting       5         5.4 REENTRANCY       5         5.5 POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                     | 4-22 |

| CHAPTER 5         PROGRAMMING TECHNIQUES         5           5.1         THE STACK         5           5.2         SUBROUTINE LINKAGE         5           5.2.1         Subroutine Calls         5           5.2.2         Argument Transmission         5           5.2.3         Subroutine Return         5           5.2.4         PDP-11         Subroutine Advantage         5           5.3         INTERRUPTS         5           5.3.1         General Principles         5           5.3.2         Nesting         5           5.4         REENTRANCY         5           5.5         POSITION INDEPENDENT CODE         5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                     | 4-74 |

| 5.1       THE STACK       5         5.2       SUBROUTINE LINKAGE       5         5.2.1       Subroutine Calls       5         5.2.2       Argument Transmission       5         5.2.3       Subroutine Return       5         5.2.4       PDP-11       Subroutine Advantage       5         5.3       INTERRUPTS       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.7       | MISCELLANEOUS                       | 4-74 |

| 5.1       THE STACK       5         5.2       SUBROUTINE LINKAGE       5         5.2.1       Subroutine Calls       5         5.2.2       Argument Transmission       5         5.2.3       Subroutine Return       5         5.2.4       PDP-11       Subroutine Advantage       5         5.3       INTERRUPTS       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                     |      |

| 5.2       SUBROUTINE LINKAGE       5         5.2.1       Subroutine Calls       5         5.2.2       Argument Transmission       5         5.2.3       Subroutine Return       5         5.2.4       PDP-11       Subroutine Advantage       5         5.3       INTERRUPTS       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CHAPTER   | 5 PROGRAMMING TECHNIQUES            | 5-1  |

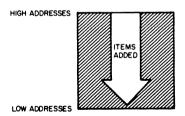

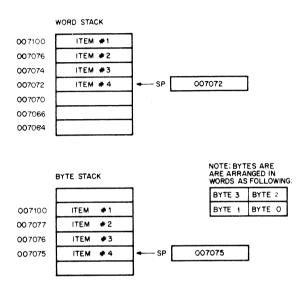

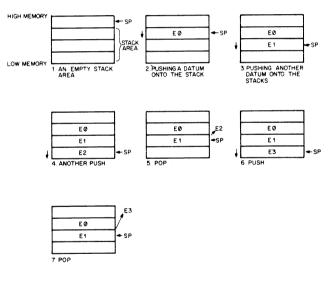

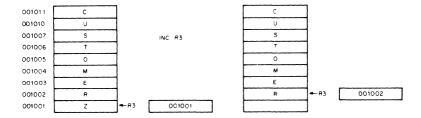

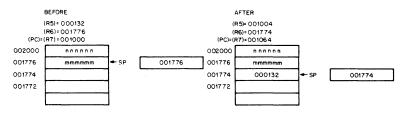

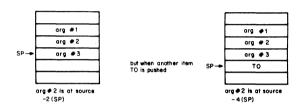

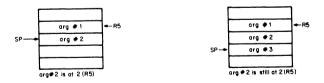

| 5.2       SUBROUTINE LINKAGE       5         5.2.1       Subroutine Calls       5         5.2.2       Argument Transmission       5         5.2.3       Subroutine Return       5         5.2.4       PDP-11       Subroutine Advantage       5         5.3       INTERRUPTS       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.1       | THE STACK                           | 5-1  |

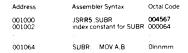

| 5.2.1       Subroutine Calls       5         5.2.2       Argument Transmission       5         5.2.3       Subroutine Return       5         5.2.4       PDP-11       Subroutine Advantage       5         5.3       INTERRUPTS       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.2       | SUBROUTINE LINKAGE                  | 5-5  |

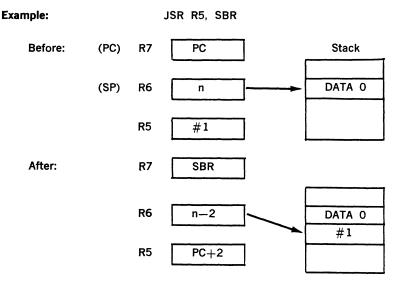

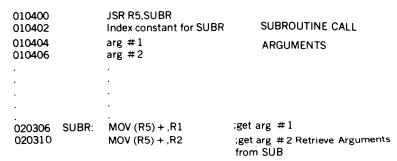

| 5.2.2 Argument Transmission       5         5.2.3 Subroutine Return       5         5.2.4 PDP-11 Subroutine Advantage       5         5.3 INTERRUPTS       5         5.3.1 General Principles       5         5.3.2 Nesting       5         5.4 REENTRANCY       5         5.5 POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                     | 5-5  |

| 5.2.3       Subroutine Return       5         5.2.4       PDP-11 Subroutine Advantage       5         5.3       INTERRUPTS       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                                     | 5-6  |

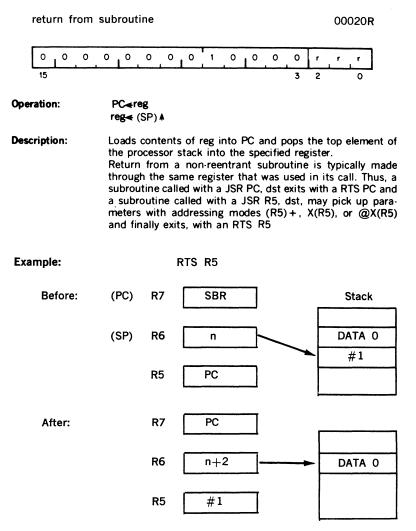

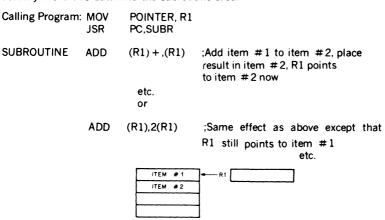

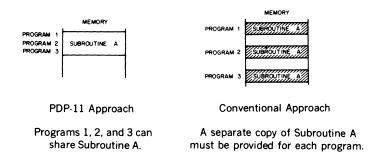

| 5.2.4 PDP-11 Subroutine Advantage       5         5.3 INTERRUPTS       5         5.3.1 General Principles       5         5.3.2 Nesting       5         5.4 REENTRANCY       5         5.5 POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                     | 5-9  |

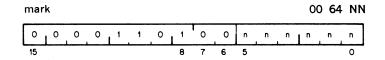

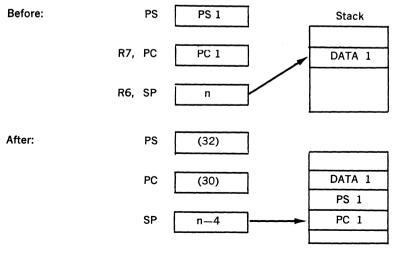

| 5.3       INTERRUPTS       5         5.3.1       General Principles       5         5.3.2       Nesting       5         5.4       REENTRANCY       5         5.5       POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | 5.2.4 PDP-11 Subroutine Advantage   | 5-9  |

| 5.3.2 Nesting       5         5.4 REENTRANCY       5         5.5 POSITION INDEPENDENT CODE       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.3       |                                     | 5-9  |