CPB-252A

## PROGRAMMING REFERENCE MANUAL

COMPUTER DEPARTMENT

### GE-225

## PROGRAMMING REFERENCE MANUAL

Revised May, 1964

COMPUTER DEPARTMENT

### **PREFACE**

The GE-225 Programming Reference Manual has been prepared both as a reference manual for programming the GE-225 information processing system and as a training aid. It includes a brief description of the major components of the system, machine language and number systems, central processor and console typewriter operations, controller selector operations, programming conventions, and an octal and alphabetical listing of General Assembly Program instructions.

The information in this manual also applies essentially to other members of the GE Compatibles/200 family of systems—the GE-200 Bank Transit System, and the GE-205 and GE-215 systems.

This manual is a condensed version of the previous edition which also contained information on the General Assembly Program, and the various peripheral subsystems used with the GE-225. Separate manuals have been published to cover these subjects, as listed below:

| Subject                                                                        | Manual Title and Publication No.                      |

|--------------------------------------------------------------------------------|-------------------------------------------------------|

| General Assembly Program                                                       | General Assembly Program II (CD225F1.006/007)         |

| 400-cpm Card Reader 1000-cpm Card Reader 100-cpm Card Punch 300-cpm Card Punch | Punched Card Subsystems Reference Manual (CPB-302)    |

| 15- & 15/41Kc. Magnetic Tape<br>Subsystems                                     | Magnetic Tape Subsystems Reference Manual (CPB-339)   |

| Paper Tape Reader/Punch                                                        | Paper Tape Subsystem Reference Manual (CPB-308)       |

| 900-Lpm On-Line High Speed Printer  900-Lpm Off/On-Line High Speed Printer     | High Speed Printer Reference Manual (CPB-321)         |

| 12-Pocket Document Handler (1200-dpm)                                          | Document Handler Reference Manual (CPB-307)           |

| 12- <b>Pock</b> et Document Handler (750-dpm)                                  | Document Handler Reference Manual (750-dpm) (CPB-333) |

c 1963,1964 by General Electric Co.

### CONTENTS

| Section |                                                                                                                                                                                                                                                                                                                      | Page                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| I       | THE GE-225 INFORMATION PROCESSING SYSTEM                                                                                                                                                                                                                                                                             |                                                                              |

|         | System Components<br>Simultaneous Operations                                                                                                                                                                                                                                                                         | I - 2<br>I - 8                                                               |

| II      | MACHINE LANGUAGE                                                                                                                                                                                                                                                                                                     |                                                                              |

|         | Number Systems<br>Data Words<br>Instruction Words                                                                                                                                                                                                                                                                    | II - 1<br>II - 7<br>II - 9                                                   |

| III     | CENTRAL PROCESSOR ORGANIZATION                                                                                                                                                                                                                                                                                       |                                                                              |

|         | Magnetic Core Storage<br>Arithmetic and Control Registers<br>Basic Operating Cycle                                                                                                                                                                                                                                   | III - 1<br>III - 3<br>III - 7                                                |

| IV      | GENERAL ASSEMBLY PROGRAM II                                                                                                                                                                                                                                                                                          |                                                                              |

|         | See new manual entitled General Assembly Program II (CD225F1.006/007)                                                                                                                                                                                                                                                | 1                                                                            |

| v       | CENTRAL PROCESSOR OPERATIONS                                                                                                                                                                                                                                                                                         |                                                                              |

|         | General Arithmetic Instructions Data Transfer Instructions Shift Instructions Internal Branch Instructions Modification Instructions Programming 16K Memory Systems Programming Central Processor Operations                                                                                                         | V - 1<br>V - 2<br>V - 14  <br>V - 24<br>V - 31<br>V - 34<br>V - 37<br>V - 41 |

| VI      | DIRECT INPUT-OUTPUT OPERATIONS                                                                                                                                                                                                                                                                                       |                                                                              |

|         | Control Console Operations Console Typewriter Operations Paper Tape Operations - See new manual entitled Compatibles/200 Paper Tape Subsystem Reference Manual (CPB-308) Card Reader Operations   See new manual entitled Compatibles/200 Punched Card Punch Operations   Card Subsystems Reference Manual (CPB-302) | VI - 1<br>VI - 6                                                             |

| VII     | CONTROLLER SELECTOR OPERATIONS                                                                                                                                                                                                                                                                                       |                                                                              |

|         | Controller Selector Priority Controller Selector Instructions Automatic Program Interrupt                                                                                                                                                                                                                            | VII - 1<br>VII - 1<br>VII - 2                                                |

Section

Page

### VIII MAGNETIC TAPE OPERATIONS

See new manual entitled Compatibles/200  $\underline{\text{Magnetic}}$   $\underline{\text{Tape}}$   $\underline{\text{Subsystems}}$   $\underline{\text{Reference}}$   $\underline{\text{Manual}}$  (CPB-339)

### IX HIGH-SPEED PRINTER OPERATIONS

See new manual entitled Compatibles/200  $\underline{\text{High}}$   $\underline{\text{Speed}}$   $\underline{\text{Printer}}$   $\underline{\text{Reference}}$   $\underline{\text{Manual}}$  (CPB-321)

### X DOCUMENT HANDLER OPERATIONS

See new manual entitled Compatibles/200  $\underline{\text{Document}}$   $\underline{\text{Handler}}$   $\underline{\text{Reference}}$   $\underline{\text{Manual}}$  (CPB-307)

### XI DISC STORAGE UNIT

See new manual entitled Compatibles/200 Disc Storage Unit Reference Manual (CPB-323)

### XII AUXILIARY ARITHMETIC UNIT OPERATIONS

See new manual entitled GE-215/225 <u>Auxiliary</u> <u>Arithmetic Unit Reference</u> <u>Manual</u> (CPB-325)

### XIII PROGRAMMING CONVENTIONS

| Memory Layouts             | XIII            | _   | 1  |

|----------------------------|-----------------|-----|----|

| Input/Output Documentation | XIII            |     | _  |

| Use of Symbols             | XIII            |     | -  |

| Subroutine Usage           |                 |     | _  |

| Typewriter Utilization     | XIII            |     | -  |

| Debugging Techniques       | XIII            |     | -  |

| Program Documentation      | XIII            | _   |    |

| 1 logiam Bocumentation     | $\mathbf{XIII}$ | - 1 | 12 |

### APPENDICES

| I.   | Representation of GE-225 Characters    | A-1  |

|------|----------------------------------------|------|

| II.  | Octal List of GE-225 Instructions      | A-3  |

| III. | Alphabetic List of GE-225 Instructions | A-11 |

### ILLUSTRATIONS

| Figure                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1 - 1<br>1 - 2<br>1 - 3<br>1 - 4<br>1 - 5                                                                                                     | GE-225 System Components<br>Central Processor and Controller Buffers<br>GE-225 Priority Access System<br>Large GE-225 System Configuration<br>Controller Selector Priority                                                                                                                                                                                                                                            | I - 8<br>I - 9<br>I - 11<br>I - 13<br>I - 14                                                                  |

| 2 - 1<br>2 - 2<br>2 - 3<br>2 - 4<br>2 - 5<br>2 - 6                                                                                            | Binary Addition Table Octal Addition Table Table of Powers of 2 and 8 Octal-to-Decimal Conversion Chart Decimal-to-Octal Conversion Charts Basic GE-225 Word                                                                                                                                                                                                                                                          | II - 2<br>II - 3<br>II - 4<br>II - 5<br>II - 6<br>II - 7                                                      |

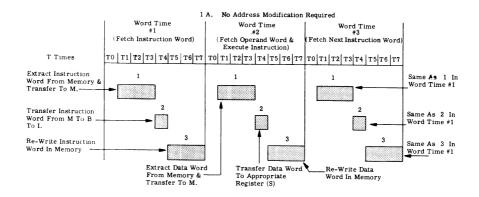

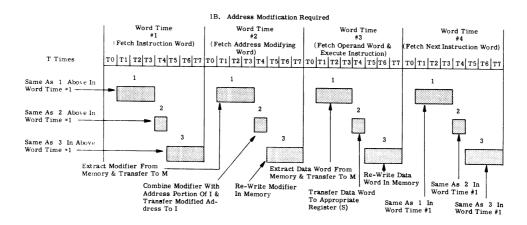

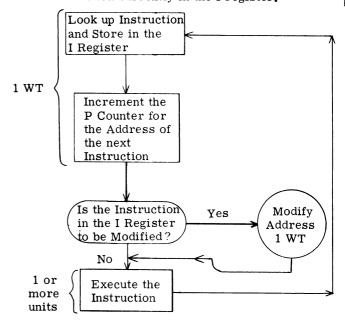

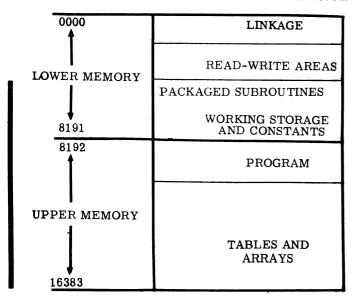

| 3 - 1<br>3 - 2<br>3 - 3<br>3 - 4<br>3 - 5<br>3 - 6<br>3 - 7<br>3 - 8                                                                          | Bit Storage in a Ferrite Core Representative Allocation of Memory GE-225 Arithmetic and Control Register GE-225 Arithmetic Registers GE-225 Control Registers Basic Timing for Single Length Word Operations GE-225 Instruction-Execution Cycle Flow Chart Showing Central Processor Operating Cycle                                                                                                                  | III - 1<br>III - 2<br>III - 4<br>III - 5<br>III - 6<br>III - 7<br>III - 8<br>III - 10                         |

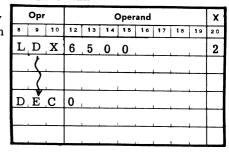

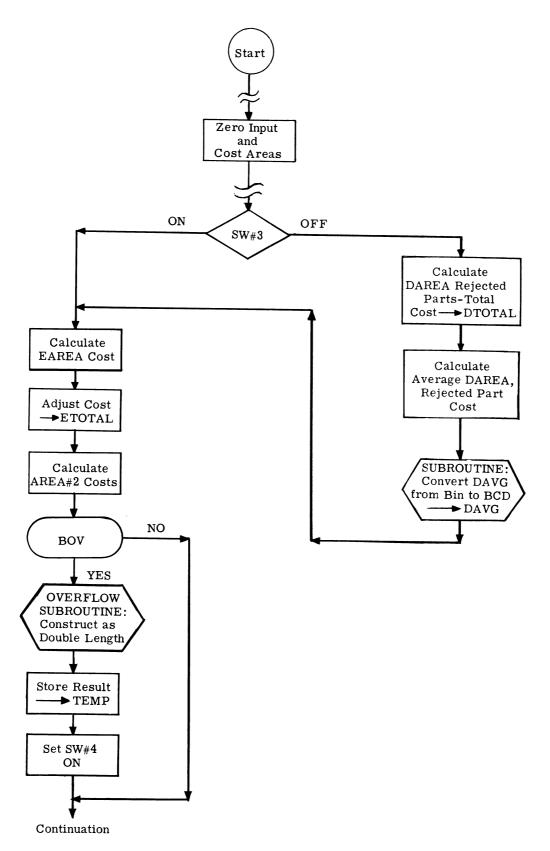

| 5 - 1<br>5 - 2<br>5 - 3<br>5 - 4<br>5 - 5<br>5 - 6<br>5 - 7<br>5 - 8<br>5 - 9<br>5 - 10<br>5 - 11                                             | Two Numbers in Memory before Scaling Incorrect Sum after Addition without Scaling Numbers in Memory after Scaling Using a Rounding Factor of .05 16K Memory Layout Instruction Characteristics when Addressing 16K Memories Rejected Parts Cost Flow Chart RPC Program - Initialization RPC Program - DPARTS Calculations RPC Program - EPARTS Calculations and Constants RPC Program - OVRFLO Routine                | V - 13<br>V - 13<br>V - 13<br>V - 14<br>V - 37<br>V - 38<br>V - 42<br>V - 43<br>V - 43<br>V - 44<br>V - 44    |

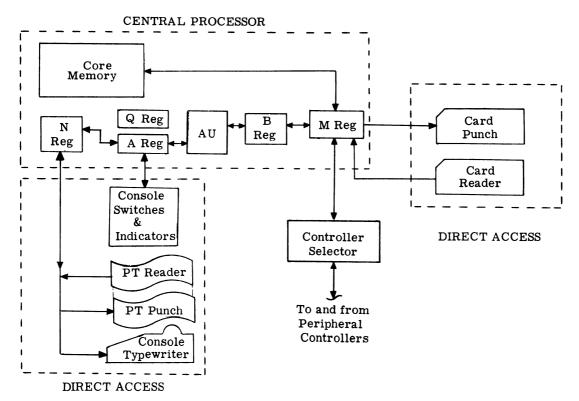

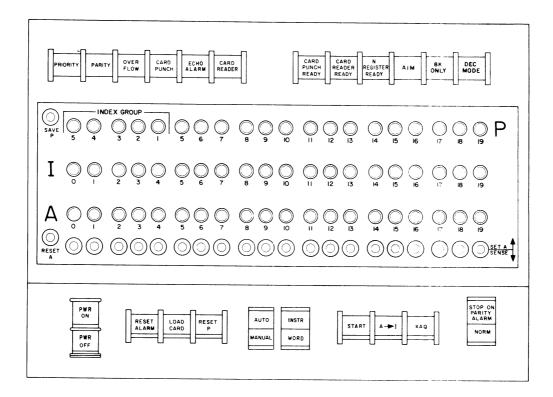

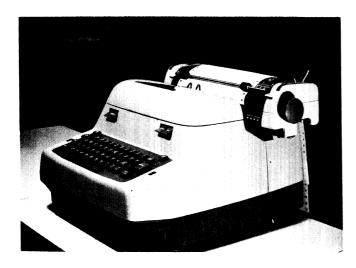

| 6 - 1<br>6 - 2<br>6 - 3<br>6 - 4<br>6 - 5                                                                                                     | Units Directly Accessing Memory The Control Console Panel Console Typewriter Typewriter Character Set Sample Typewriter Coding                                                                                                                                                                                                                                                                                        | VI - 1<br>VI - 2<br>VI - 7<br>VI - 7<br>VI - 9                                                                |

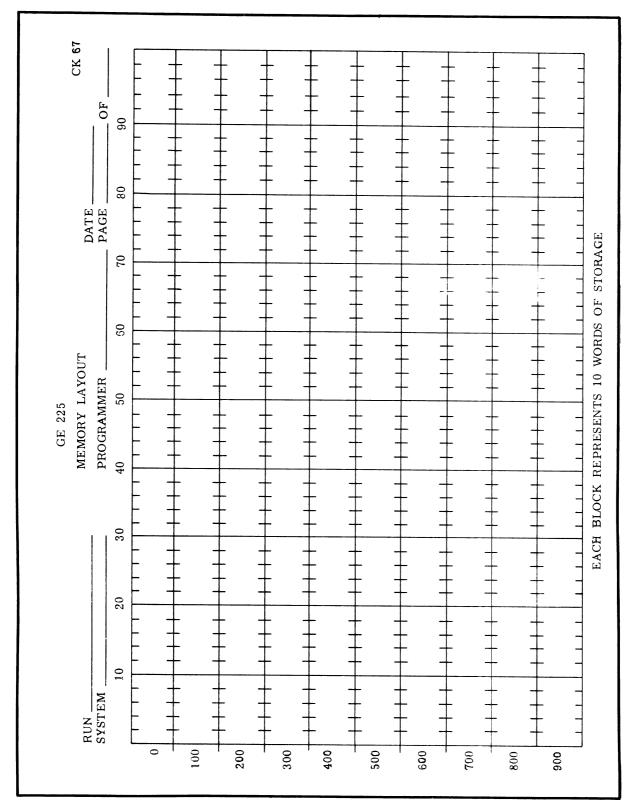

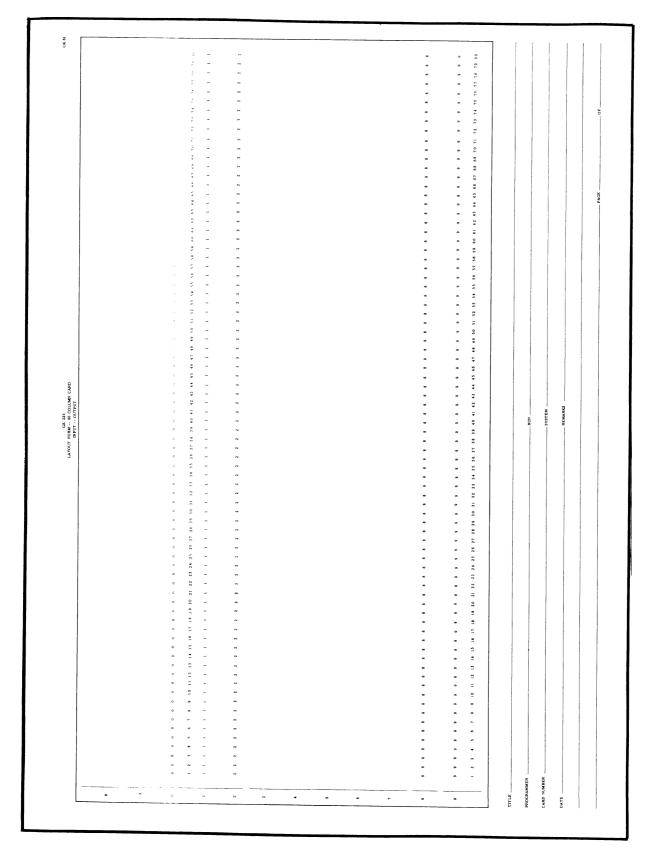

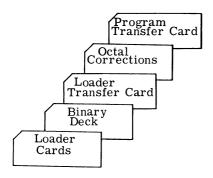

| 13 - 1<br>13 - 2<br>13 - 3<br>13 - 4<br>13 - 5<br>13 - 6<br>13 - 7<br>13 - 8<br>13 - 9<br>13 - 10<br>13 - 11<br>13 - 12<br>13 - 13<br>13 - 14 | Typical Memory Allocation Magnetic Tape Record Layout Magnetic Tape Record Layout Sheet Memory Layout Sheet BCD Multiple Card Layout Sheet Memory Allocation Layout Sheet 80-Column Card Layout Form Typical Symbolic Addresses Representative Subroutine Subroutine Requiring a Calling Sequence Subroutine Calling Sequence Printer Controller Octal Memory Dump Programmed Octal Memory Dump Octal Correction Card | XIII - 1 XIII - 2 XIII - 3 XIII - 4 XIII - 5 XIII - 6 XIII - 7 XIII - 8 XIII - 8 XIII - 9 XIII - 10 XIII - 11 |

GE-225 ----

### SECTION I

### THE GE - 225 INFORMATION PROCESSING SYSTEM

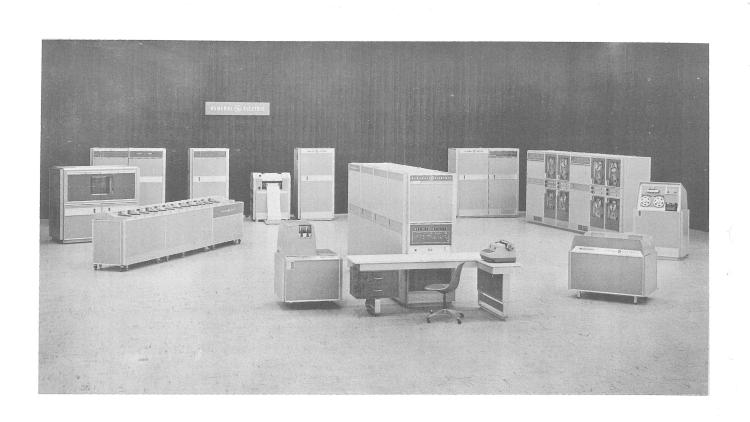

The GE-225 Information Processing System is a medium-scale, general-purpose digital computer that permits an integrated approach to the total information processing needs of business, government, and science, while providing an economical means of processing large volumes of data at high speed.

The modular design of the GE-225 system provides flexibility in meeting data processing requirements for a wide range of applications. A GE-225 system consists of reading (input) and writing (output) devices interconnected and controlled through a central pro-The number and types of input and output devices, as well as the configuration of the central processor, are determined largely by the desired applications. Input data can be from paper tape, magnetic tape, punched cards, and magnetically-encoded (MICR) paper documents. Output can be in the form of paper tape, magnetic tape, punched cards, and printed reports. Both alphabetic and numeric data can be received or produced by the computer, either locally, or over long distances from the central processor using peripheral data transmission equipment, such as the Datanet-15 and its associated terminals.

The GE-225 is a solid-state, single-address computer that operates under both stored program and operator control. Also, it is a buffered computer with an input-output priority system that permits simultaneous operations, such as reading, writing, and processing. Further flexibility is provided through the ability to operate internally in either the binary or the decimal modes.

The basic programming language for the GE-225 is provided by the General Assembly Program. It is an automatic assembly system that permits the programmer to prepare routines in meaningful symbolic language, rather than in the absolute machine language, or code, of the GE-225 and then utilize the GE-225 (and the assembly program) to assemble a computer-ready program. Extensive clerical effort is eliminated by using significant mnemonic codes that generally have a one-to-one correlation to basic machine instructions. Added flexibility is provided because addresses can be assigned using either decimal or symbolic notation. Capabilities of the General Assembly Program also include the ability to incorporate the many library routines provided by General Electric, such as input-output and mathematical packages.

I-1 October 1963

### SYSTEM COMPONENTS

The GE-225 system can assume various configurations, depending upon the application requirements. Brief descriptions of system components are given below. More detailed descriptions and information pertaining to their use are provided in appropriate programming sections of the manual.

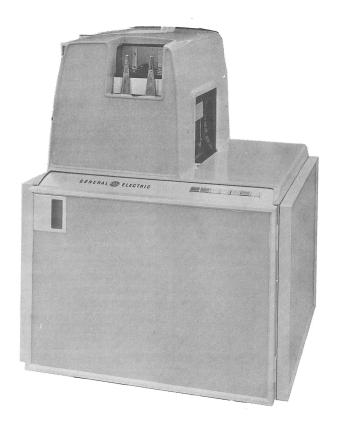

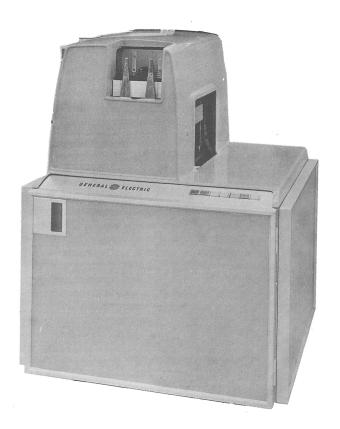

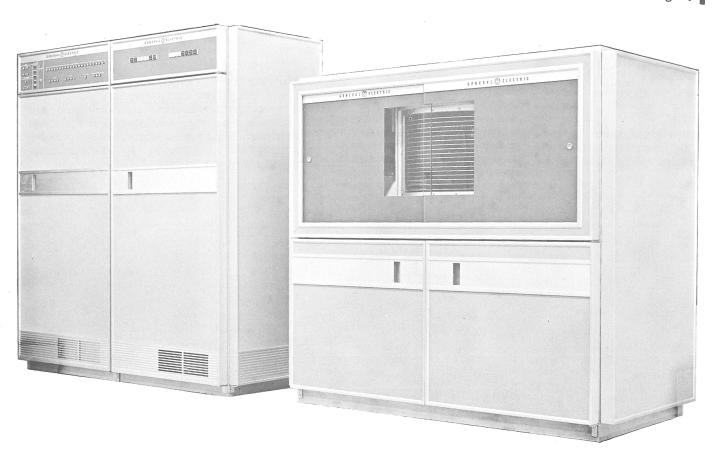

### Central Processor

The GE-225 Central Processor provides arithmetic, comparison, and decision circuits and automatic control facilities for the processing system. In addition, it houses the randomly-accessed magnetic core storage (or memory).

Core storage provides the main memory element for the system, although it can be augmented by external storage in the form of magnetic tape or disks. Both data to be processed and the controlling instructions are held in core storage and called forth by the control element as required. Information in storage is retained by tiny magnetic cores, each core capable of holding one bit (binary digit) of data. The basic unit of storage is the word, each word consisting of 20 bits (plus a check bit), and each word being individually addressable. The access time associated with transferring a word into or out of memory is 18 microseconds, or one word time. Core storage can consist of 4,096, 8,192, or 16,384 locations, each of which can contain a single-address instruction, a binary data word, or three alphanumeric or binary-codeddecimal (BCD) characters.

### Control Console

The GE-225 Control Console, attached to the central processor, provides manual control of operations, visual display of the contents of appropriate registers, program monitoring facilities for the operator, and typed output via the console typewriter, under program control. From the console, the operator controls the initial loading and starting of programs and can perform in-process modifications based upon processing results.

tapes at 250 or 1000 characters per second, and a mechanism for punching five-, six-, seven-, and eight-channel paper tapes at 110 characters per second. Provisions are made to accommodate all common paper tape codes.

The GE-225 Paper Tape Reader-Punch is two mechanically-independent units: a mechanism for reading five-, six-, seven-, and eight-channel perforated paper

Paper Tape Reader-Punch

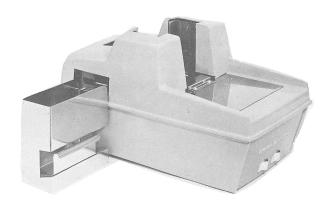

### Card Reader

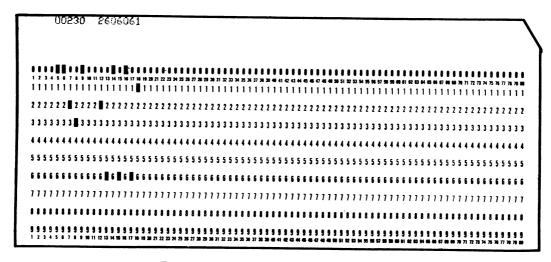

Either a 400 cardper minute or a 1000 card per minute card reader is available with the GE-225. Both readers can read standard 80-column punched cards in one of three modes: ten-row or twelve-row binary, or standard Hollerith (alphanumeric) mode. Cards are read serially (one column at a time) in all three modes.

Either card reader can operate simultaneously with the central processor and other peripheral operations. For example, cards can be read at the same time that data is input from magnetic tape or from a 12-pocket document handler; simultaneously, previously input data can be processed within the central processor.

Standard cards are 7-3/8 by 3-1/4 inches and consist of 80 columns along the long dimension and 12 rows along the short dimension. As cards are moved through the card reader mechanism, all twelve row positions of a column are simultaneously photoelectrically sensed. Card reader logic, which is contained within the central processor, permits cards to be read on demand by the processor or continuously.

### Card Punch

The card punch is an output device which punches standard 80-column cards at a rate of either 100 or 300 cards per minute, depending upon the model selected. Cards are punched in either of three modes: ten-row or twelve-row binary, or standard Hollerith mode, depending upon program control.

The card punch is primarily an on-line peripheral and receives basic control signals from the central processor. However, gang punching, or duplication of many cards from a master card, can be performed off-line.

As an on-line peripheral, the card punch can operate simultaneously with the central processor and other peripherals.

### Controller Selector

The GE-225 Controller Selector serves as a common control and data transfer point between the central processor and the peripheral controllers for magnetic tape handlers, document handlers, high-speed printers, mass random access data storage, Datanet-15 terminals, and the auxiliary arithmetic unit. The controller selector contains eight hubs or addresses to which eight controllers can be connected. By priority assignments, which are determined by the addresses, the controller selector controls access to core storage for the attached peripheral units. This permits simultaneous operation of as many as eight peripherals on the controller selector, plus the card reader and punch, for a total of 10 concurrent input/output operations.

The logic for the controller selector is contained within the central processor. Access to the central processor and memory for peripherals and their associated controllers is provided by cables between the controller selector and the controllers.

I-4

### Control Console

The GE-225 Control Console, attached to the central processor, provides manual control of operations, visual display of the contents of appropriate registers, program monitoring facilities for the operator, and typed output via the console typewriter, under program control. From the console, the operator controls the initial loading and starting of programs and can perform in-process modifications based upon processing results.

tapes at 250 or 1000 characters per second, and a mechanism for punching five-, six-, seven-, and eight-channel paper tapes at 110 characters per second. Provisions are made to accommodate all common paper tape codes.

### Card Reader

Either a 400 cardper minute or a 1000 card per minute card reader is available with the GE-225. Both readers can read standard 80-column punched cards in one of three modes: ten-row or twelve-row binary, or standard Hollerith (alphanumeric) mode. Cards are read serially (one column at a time) in all three modes.

### Paper Tape Reader-Punch

The GE-225 Paper Tape Reader-Punch is two mechanically-independent units: a mechanism for reading five-, six-, seven-, and eight-channel perforated paper

Either card reader can operate simultaneously with the central processor and other peripheral operations. For example, cards can be read at the same time that data is input from magnetic tape or from a 12-pocket document handler; simultaneously, previously input data can be processed within the central processor.

Standard cards are 7-3/8 by 3-1/4 inches and consist of 80 columns along the long dimension and 12 rows along the short dimension. As cards are moved through the card reader mechanism, all twelve row positions of a column are simultaneously photoelectrically sensed. Card reader logic, which is contained within the central processor, permits cards to be read on demand by the processor or continuously.

### Card Punch

The card punch is an output device which punches standard 80-column cards at a rate of either 100 or 300 cards per minute, depending upon the model selected. Cards are punched in either of three modes: ten-row or twelve-row binary, or standard Hollerith mode, depending upon program control.

The card punch is primarily an on-line peripheral and receives basic control signals from the central processor. However, gang punching, or duplication of many cards from a master card, can be performed off-line.

As an on-line peripheral, the card punch can operate simultaneously with the central processor and other peripherals.

### Controller Selector

The GE-225 Controller Selector serves as a common control and data transfer point between the central processor and the peripheral controllers for magnetic tape handlers, document handlers, high-speed printers, mass random access data storage, Datanet-15 terminals, and the auxiliary arithmetic unit. The controller selector contains eight hubs or addresses to which eight controllers can be connected. By priority assignments, which are determined by the addresses, the controller selector controls access to core storage for the attached peripheral units. This permits simultaneous operation of as many as eight peripherals on the controller selector, plus the card reader and punch, for a total of 10 concurrent input/output operations.

The logic for the controller selector is contained within the central processor. Access to the central processor and memory for peripherals and their associated controllers is provided by cables between the controller selector and the controllers.

I - 4

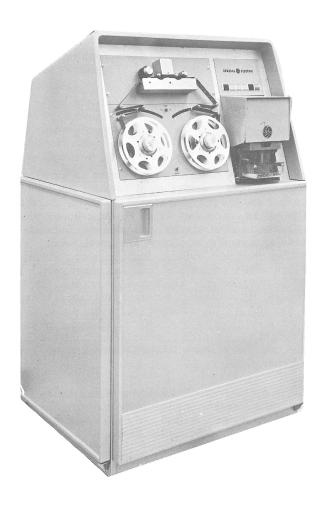

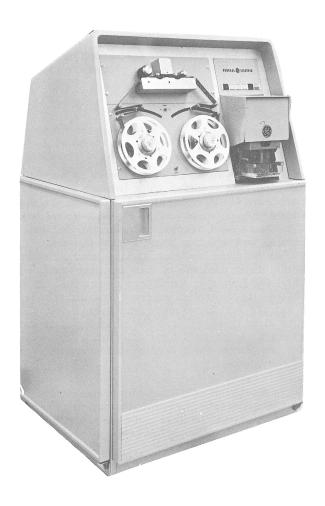

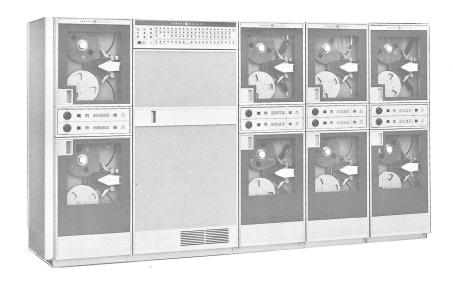

### Magnetic Tape

Magnetic tape provides a fast method of transmission of data between the central processor and bulk storage. Millions of bits of data can be recorded on a single reel of tape, thus providing a compact and economical storage medium. Magnetic tape can provide in-process (on-line) or static (off-line) storage for immediate or subsequent use, yet can be erased and be re-used repeatedly.

Up to eight magnetic tape controllers can be connected to the controller selector; up to eight magnetic tape handlers can be connected to each controller, providing a maximum of 64 magnetic tape handlers for the GE-225 system. Different models of magnetic tape handlers provide two data transfer rates: 15,000 and 41,700 characters per second. Data can be read or written either in standard binary or in binary-coded-decimal (BCD) mode.

The combination of a tape controller and its associated tape handlers comprises a magnetic tape subsystem. A subsystem of one tape controller and multiple tape handlers permits reading or writing concurrently with other operations. A subsystem containing two or more tape controllers permits reading and writing simultaneously with other operations.

# GENERAL & ELECTRIC

### High Speed Printer

The GE-225 High Speed Printer is an output unit for applications requiring presentation of large quantities of printed information. The printer produces alphanumeric output, up to 120 characters per line, 900 lines per minute. Printing format is governed by the printer controller, which contains logic for automatically editing the print line independent of the central processor. Editing features include zero suppression, deletion of data, and insertion of special symbols, constants, and spaces. Printing can also be performed completely off-line from the system by using magnetic tape as an interim storage medium. Printing and editing can proceed simultaneously with other peripheral and central processor operations.

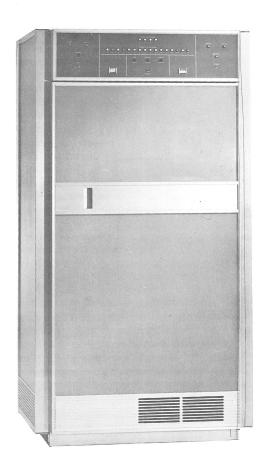

### Disc Storage Unit

Disc Storage Units, each consisting of 16 vertically-mounted rotating magnetic disks, are available for non-sequential file processing. Each DSU has a total capacity of 98,304 records, or over 6 million words. This provides storage for about 19 million alphanumeric characters or 34 million numeric digits.

One or two DSU controllers can be connected to the controller selector; up to four DSU units can be connected to each controller. DSU reading and writing operations can proceed simultaneously with other peripheral and central processor operations.

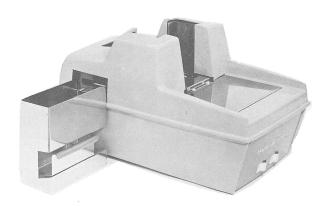

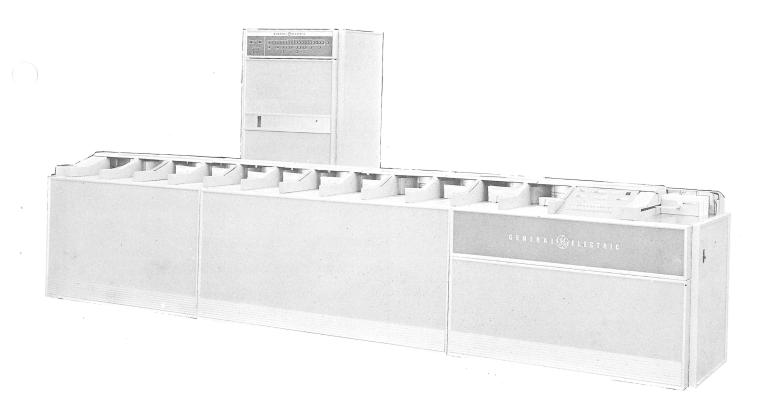

### 12-Pocket Document Handler

The 12-pocket document handler is an on-line or off-line peripheral that reads and sorts documents printed with magnetic ink in E13B font at a speed of 1200 documents per minute. The document handler can be used off-line as a document sorter, and it is possible to use two sorters simultaneously. The document handler adapter (controller) permits concurrent operation with other peripherals and the central processor. Two document handlers under the control of a single adapter permit an input rate to the central processor of 2400 documents per minute.

### Auxiliary Arithmetic Unit (AAU)

Although the AAU is connected to the central processor through the controller selector (address 7), it is more properly considered to be an extension of the central processor, rather than a peripheral unit. The AAU provides increased facility for double-length word binary arithmetic in either normalized or unnormalized floating-point modes or in fixed-point mode. The AAU can operate concurrently with normal central processor and peripheral operations.

### Datanet-15

Transmission and reception of data between the GE 225 Central Processor and remote locations is made possible by the Datanet-15, which can accept serial data at speeds from 60 to 2400 bits per second. The Datanet-15 can operate with as many as 15 remote stations, one at a time, in addition to controlling a paper tape reader-punch. Terminal devices include Teletype equipment, other Datanet-15 units, or virtually any terminal device utilizing five-, six-, seven-, or eight-channel bit codes.

### SIMULTANEOUS OPERATIONS

The logical design of the GE-225 permits up to eleven simultaneous input-output operations. That is, data can be transferred between core storage in the central processor and several direct and indirect peripherals at the same time that the central processor is engaged in processing data previously read in. Such operations are made feasible because of the vast differences in data transfer rates between core storage (18 microseconds per word), and peripherals, such as the 400 cpm card reader (5610 microseconds per BCD word).

|                                                                  | Maximun<br>Per |

|------------------------------------------------------------------|----------------|

| Name                                                             | System         |

| CENTRAL PROCESSOR (mandatory) CONTROL CONSOLE, including Console | 1              |

| Typewriter (mandatory)                                           | 1              |

| DIRECT INPUT-OUTPUT UNITS Paper Tape Reader-Punch                | 1              |

| Cand Boadon 400 cnm on High Spood                                |                |

| Card Reader, 400 cpm or High Speed<br>Card Punch, 100 or 250 cpm | 1              |

| PERIPHERAL CONTROLLERS                                           |                |

| Controller Selector                                              | 1              |

| Mass Random Access Data Storage                                  | 4              |

| Controller                                                       | 1              |

| Magnetic Tape Controller                                         | 8              |

| High-Speed Printer Controller                                    | 8              |

| Datanet-15                                                       | 8              |

| Document Handler Adapter                                         | 8<br>1         |

| Auxiliary Arithmetic Unit                                        | 1              |

| CONTROLLER SELECTOR PERIPHERALS                                  | <u>S</u>       |

| Mass Random Access Data Storage Units                            | 8              |

| Magnetic Tape Handlers                                           | 64             |

| High-Speed Printers                                              | 8              |

| Datanet Terminals                                                | 120            |

| 12-Pocket Document Handlers                                      | 16             |

| TE TOOMO BOOMMOND TONIOND                                        |                |

Figure 1-1. GE-225 System Components

To make optimum use of the high speed of core storage, the GE-225 makes provision for time sharing access to memory by buffering data transfers, assigning peripheral priorities for access to memory, and permitting simultaneous processing of two or more unrelated programs.

### Buffers and Buffering

Buffering is a technique for providing optimum data transfer between two components having different data transfer rates such as core storage and the 400 cpm card reader mentioned above. Buffering involves using a temporary storage device, or <u>buffer</u>, that can be filled with data at a rate governed by the data source component, and subsequently unleaded into the data receiving component at a rate governed by that component. This permits both components to function at their optimum speeds when processing unrelated data without the faster component being slowed down during data transfers by the slower one.

Thus, in transfers between core storage and the 400 cpm card reader, although it takes 150,000 microseconds to read all 80 card columns, core storage

### CORE STORAGE BUFFERS

Central Processor

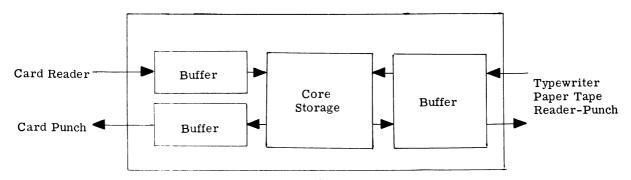

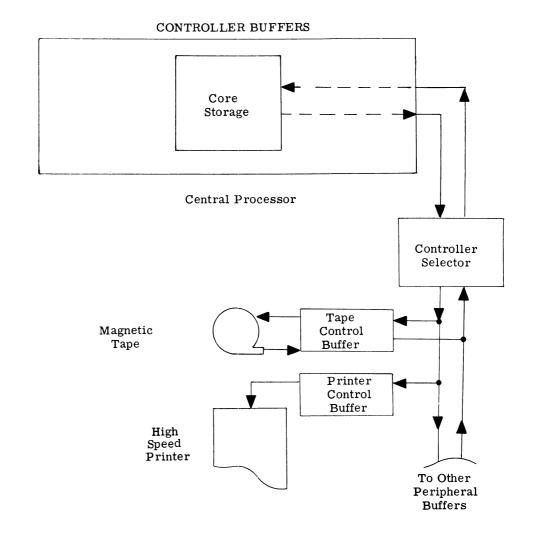

Figure 1-2. Central Processor and Controller Buffers

is occupied in receiving the dath read for only 1512 microseconds (one word time per column). The balance of the time it takes to read the card (148,560 microseconds) can be used for other data processing.

Buffers in the GE-225 are of two types: direct I-O buffers and controller buffers, as illustrated in Figure 1-2. Direct I-O buffers, located within the central processor, are for use with peripherals having direct access to core storage, such as the card reader and punch, the paper tape reader-punch, and the console typewriter. Controller buffers are located in the separate controllers for high-speed peripherals, such as magnetic tape handlers, MRADS units, and high-speed printers. Buffers for these units have access to core storage indirectly through the controller selector.

### The Interrupt Principle

The interrupt principle takes advantage of the significant difference in operating speeds of the central processor and the peripherals by permitting the normal 'fetch instruction, execute, fetch instruction, execute, fetch...etc.,' sequence of the central processor to be interrupted for data transfers.

Two kinds of interrupt are provided in the GE-225. One, related to normal program processing, is called priority interrupt; the other, related to multi-program processing, is called automatic program interrupt.

### PRIORITY INTERRUPT

In the GE-225, buffering permits two or more operations in a program to be performed simultaneously; for example, cards or tape can be read while computing occurs in the central processor and, at the same time, cards or tape can be written. In the example, computation and access to core storage by the central processor are interrupted whenever the input or output buffers are filled or emptied and a core storage access cycle is required to transfer data.

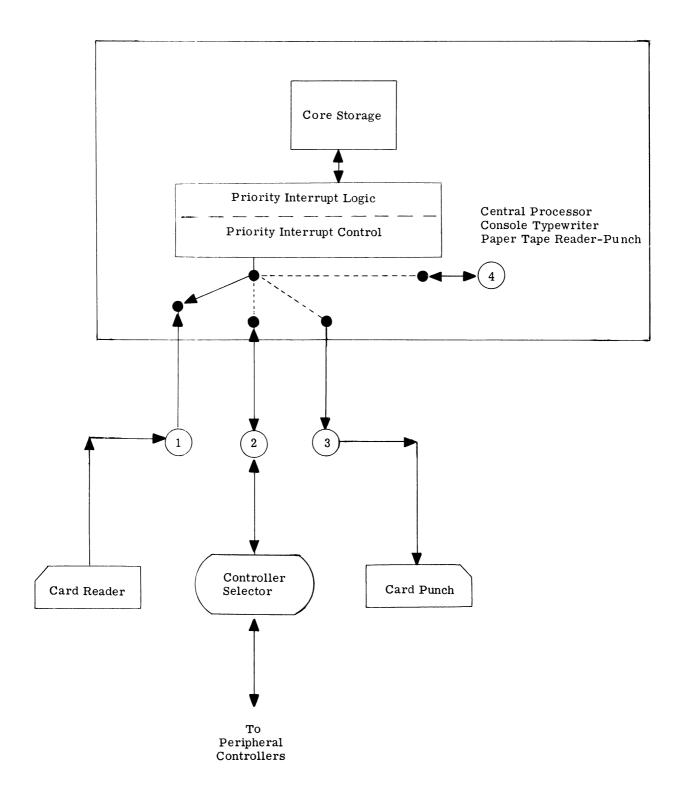

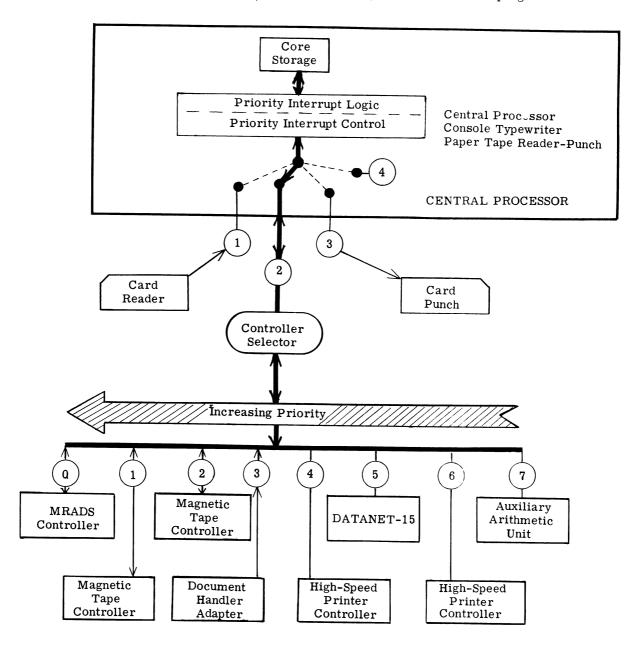

If the central processor requests memory access while input or output peripherals are requesting access, the processor obtains access on the first free cycle. Because several requests for access to core storage might be made at the same time, provision is made to grant only one request for access during a memory cycle. The priority interrupt logic incorporated into the system analyzes these requests for access and determines which of four possible channels is to have access during that particular cycle. Refer to Figure 1-3.

All access to memory, including that by the central processor, is controlled by the priority interrupt logic, which controls four channels. The first channel has

highest priority; the fourth channel has lowest priority. Normally, priority is assigned to components thusly:

| Channel and      | Peripheral                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Priority         | or                                                                                                                     |

| Assignment       | Equipment                                                                                                              |

| 1<br>2<br>3<br>4 | Card Reader Controller Selector Card Punch Central Processor, including Console Typewriter and Paper Tape Reader-Punch |

In general, priority is determined by the operating characteristics and buffering of system peripherals. Usually, the peripheral having a high data transfer rate will have a high priority; the peripheral with a low data transfer rate will have a low priority. Two major exceptions to this arrangement are the card reader and the central processor.

The card reader is buffered in such a way that it must have uninterrupted access to core storage while it is reading each character on a card, or data may be lost. The card reader is assigned the highest priority.

On the other hand, the central processor is assigned the lowest priority (with the console typewriter and paper tape reader-punch) because there is no danger of lost data if central processor operation is interrupted by higher-priority peripherals. Also, program-run-time is optimized if fully-buffered peripherals are permitted to operate at capacity.

The controller selector, through which all high-speed peripherals access core storage, is assigned the second-highest priority. These peripherals are fully buffered and there is little danger of data loss if their operation is interrupted. Controller selector priority is further discussed below.

The card punch which is a comparitively slow peripheral, is assigned the third priority channel because a card punch operation is initiated only when the card punch buffer is filled. The card punch buffer can maintain a partially-filled condition indefinitely; thus, interrupting card punch operations cannot cause inadvertent data loss.

Controller Selector Priority Interrupt. The controller selector is the common control and transfer point for input-output peripherals. Specifically, the controller selector: 1) provides peripheral configuration flexibility and 2) permits the establishment of user-determined priority systems.

Figure 1-3. GE-225 Priority Access System

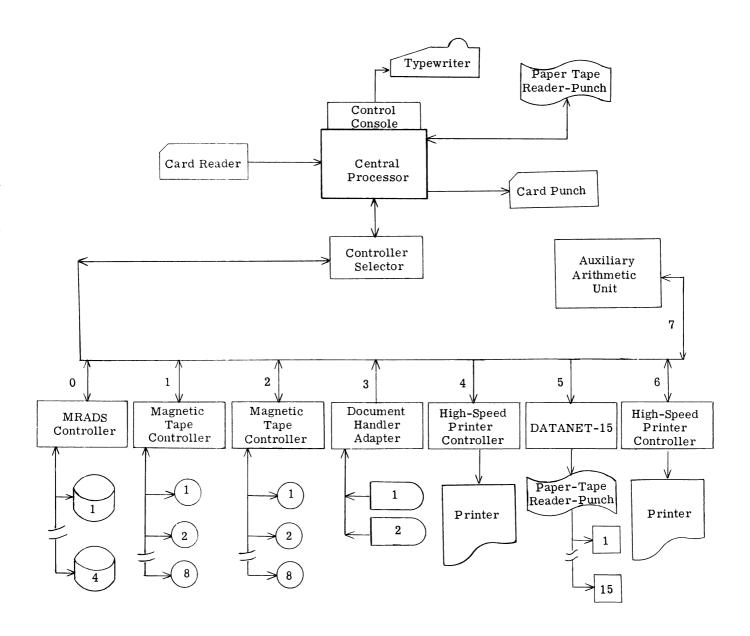

The controller selector permits the use of a wide variety of peripherals. Through plug-in connectors, peripheral controllers can be connected in many ways and changed to meet varying system requirements. This ability allows for addition of specific peripherals as the needs of an installation grow. It also allows for the addition of new or improved input-output units with little or no logic or wiring changes. Figure 1-4 illustrates one possible system configuration. Smaller or different configurations are also possible.

In Figure 1-4, the card reader, cardpunch, paper tape reader-punch, and console typewriter are connected directly to the central processor. The other peripherals, through their controllers, are connected to the central processor through the controller selector. As many as eight controllers can be connected to the controller selector through eight plug-in connectors, each with an individual address; these controllers can be a combination of the following:

1 or 2 DSU Controllers

ı

1 to 8 Magnetic Tape Controllers

1 to 8 High-Speed Printer Controllers

1 to 8 Datanet-15 Controllers

1 to 8 Document Handler Adapters (Controllers)

1 Auxiliary Arithmetic Unit (includes Controller)

As shown in Figure 1-4, controllers can direct the operation of several peripherals. The following list shows the maximum possible number of peripherals each respective controller can handle:

1 to 4 DSU Units

1 to 8 Magnetic Tape Handlers

1 High-Speed Printer

1 to 15 Datanet Terminals, plus a Paper Tape Reader-Punch

1 to 2 12-Pocket Document Handlers

1 Auxiliary Arithmetic Unit

The priority interrupt system actually operates on two levels. The first level assigns priority access to core storage through one of the four priority channels, with the controller selector being assigned the second-highest priority (channel 2). The second level exists within the channel 2 priority of the controller selector and is assigned through eight address hubs, numbered 0 through 7. Once a controller selector request for access is granted, the controller selector priority system determines which of two or more requesting controllers is to receive memory access. Which controller receives access is determined by its assigned priority, as evidenced by the controller selector address hub to which it is connected. The controller

connected to address hub 0 has highest priority; the controller on hub 7 has lowest priority within the controller selector priority.

Thus, any controller on the controller selector has a higher priority than the card punch (channel 3) or the central processor and its associated peripherals (channel 4).

Figure 1-5 is an expansion of the priority interrupt control system shown previously in Figure 1-3. This diagram further illustrates the relationship between overall system priority and controller selector priority.

The priority assignments for peripherals connected through the controller selector should be consistent with the data transfer rates and the relative amounts of data to be transferred by each peripheral. If requests for access are received from two units simultaneously, the one having the higher transfer rate will have the higher priority and be granted access first. The other unit, having the lower priority, must wait at least one memory cycle before attaining access. The reasoning behind this arrangement is that the slower unit can wait longer with less effect on total processing time and less danger of data loss than can the faster unit. A magnetic tape controller, for example, generally should have a higher priority (lower priority address) than does a printer controller. Once a magnetic tape controller initiates tape motion, the controller must have ready access to memory for optimum data transfer. The printer, on the other hand, does not start printing until it has received all requisite data, and can therefore afford to wait several cycles for data.

### AUTOMATIC PROGRAM INTERRUPT

Because the central processor will lose no information if program processing is temporarily interrupted, it is possible to provide instruction coding in a main program for an automatic interruption of the program to process one or more 'priority' programs.

Automatic program interrupt is an optional feature to control the simultaneous processing of two or more unrelated programs. This provides for concurrent operation of peripherals while the main program is being processed. Priority programs could include those in which it is desired to transfer data from cards, tape, or core storage to the high-speed printer, or to an MRADS unit.

Automatic program interrupt in the central processor monitors the card reader, card punch, and controller selector peripherals; the interrupt feature takes effect only when a peripheral that has previously been engaged returns to the idle status. Initial engagement of the peripheral is controlled by the stored program. An

Figure 1-4. Large GE-225 System Configuration

instruction early in the main program sets the automatic program interrupt to permit exit from the program when a peripheral signals the central processor that it is idle. Note that this differs from priority interrupt, which requires that a peripheral actively request access to memory. An automatic program interrupt causes a transfer from the main program to a 'priority' routine which initiates use of a peripheral and subsequently returns control to the main program; simultaneously, the peripheral continues operation. When interruption of the main program occurs, the

location of the next main program instruction to be executed is stored in a special modification word. When the 'priority' routine is completed, a branchinstruction returns control to the main program.

Entry to a 'priority' routine automatically turns off the automatic program interrupt. To permit further interruptions of the main program, the 'priority' routine must reset the automatic program interrupt before returning control to the main program.

Figure 1-5. Controller Selector Priority

### SECTION II

### MACHINE LANGUAGE

To efficiently program the GE-225, the programmer should have a certain amount of knowledge concerning numbering systems other than the familiar decimal notation. He should also know how to convert numbers from one system to another. The reasons for this are simple: 1) the GE-225 system holds and manipulates data in binary notation, 2) the programmer generally functions most effectively when working with numbers in the decimal form, and 3) because neither decimal nor binary notation is satisfactory as a common language between programmer and computer, an intermediate numbering system (octal notation) is often useful.

### NUMBER SYSTEMS

The decimal number system consists of ten digits, 0 through 9, which are used in combination to express values greater than 9. Depending upon their relative positions in a number, digits are considered to be equal to the digit times a positional factor. This factor is some exponential power of ten, the base of the decimal system. For example, the number 458 is actually an abbreviated way of expressing the following:

| Digit | P<br> | ositiona<br>factor | al<br>_ | Value |          |

|-------|-------|--------------------|---------|-------|----------|

| 4     | х     | $10^2$             | =       | 400   | hundreds |

| + 5   | х     | 101                | =       | + 50  | tenths   |

| + 8   | x     | 100                | =       | + 8   | units    |

|       |       |                    | =       | 458   |          |

Any value less than infinity can be expressed in the decimal system by expanding the number of positional factors as far as necessary.

Other number systems are possible, using bases other than ten. In each system, the number of digits used corresponds to the base. A number system with a base of 7 could have the digits 0 through 6, with positional values corresponding to the powers of 7. Note that, whatever the number system, the highest digit used is one less than the base of the system.

### Binary Number System

The binary number system uses two digits, 0 and 1, called binary digits or bits, and has a base of 2. Positional notation is similar to that of the decimal system. Successive positions in a binary number, from right to left, have values corresponding to increasing powers of 2. Thus, the binary number 11011101 is equal to  $1 \times 2^7 + 1 \times 2^6 + 0 \times 2^5 + 1 \times 2^4 + 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$ , or 221 in decimal notation.

Like the decimal system, any number less than infinity can be expressed by using enough positions.

Counting in binary is similar to decimal, beginning with 0, then 1. Once the highest digit is reached, a carry to the left adjacent digit position is made and the count starts at zero again. Thusly:

| Decimal | Binary |

|---------|--------|

| •       |        |

| 0       | 0      |

| 1       | 1      |

| 2       | 10     |

| 3       | 11     |

| 4       | 100    |

| 5       | 101    |

| 6       | 110    |

| 7       | 111    |

| 8       | 1000   |

| 9       | 1001   |

| etc.    | etc.   |

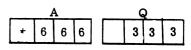

Addition in binary is simpler than decimal addition, as illustrated in Figure 2-1. Other arithmetic operations are similarly easy.

| + | 0 | 1  |

|---|---|----|

| 0 | 0 | 1  |

| 1 | 1 | 10 |

Figure 2-1. Binary Addition Table

The table shows that 0 + 0=0, 0 + 1=1, 1 + 0=1, and 1 + 1=0 plus a 1 carry. In a two-number addition, the largest intermediate sum is never more than 1 with a 1 carry.

$\frac{\text{Example:}}{11010110} \quad \text{Add the binary numbers 10110101 and}$

### Octal Number System

The octal number system uses eight digits, 0 through 7, and the base 8. Again, positional notation is similar to that of the decimal and binary systems. Successive positions in an octal number, from right to left, have values corresponding to increasing powers of 8. Thus the octal number 1376 is equal to  $1 \times 8^3 + 3 \times 8^2 + 7 \times 8^1 + 6 \times 8^0$ , or 766 in decimal notation.

The octal system can be extended to express any size number.

| Decimal<br>value     | eto | 26 <b>2</b> 6 | 2,144 | 32,768         | 4096           | 512            | 64             | 8              | 1  |

|----------------------|-----|---------------|-------|----------------|----------------|----------------|----------------|----------------|----|

| Positional<br>factor |     | ••••          | 86    | 8 <sup>5</sup> | 8 <sup>4</sup> | 8 <sup>3</sup> | 8 <sup>2</sup> | 8 <sup>1</sup> | 80 |

| Digit<br>position    | X   |               | X     | X              | x              | X              | x              | X              | X  |

Octal counting is also similar to decimal counting. The count begins with 0, proceeds to 7 (the largest octal digit), generates a carry into the adjacent left position, and starts again at zero. Thusly:

| Decimal          | Octal            |

|------------------|------------------|

|                  |                  |

| 0                | 0                |

| 1                | 1                |

| 2                | 2                |

| 2<br>3<br>4<br>5 | 2<br>3<br>4<br>5 |

| 4                | 4                |

| 5                | 5                |

| 6                | 6                |

| 7                | 7                |

| 8                | 10               |

| 9                | 11               |

| 10               | 12               |

| 11               | 13               |

| 12               | 14               |

| 13               | 15               |

| 14               | 16               |

| 15               | 17               |

| 16               | 20               |

| etc.             | etc.             |

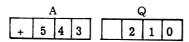

Octal addition and other arithmetic operations are more difficult than binary or the familiar decimal operations. The most useful is octal addition, which is facilitated by tables such as that shown in Figure 2-2.

| Octal Digits |   |   |    |    |    |    |    |    |    |   |

|--------------|---|---|----|----|----|----|----|----|----|---|

|              | + | 0 | 1  | 2  | 3  | 4  | 5  | 6  | 7  |   |

|              | 0 | 0 | 1  | 2  | 3  | 4  | 5  | 6  | 7  |   |

|              | 1 | 1 | 2  | 3  | 4  | 5  | 6  | 7  | 10 |   |

| Digits       | 2 | 2 | 3  | 4  | 5  | 6  | 7  | 10 | 11 |   |

|              | 3 | 3 | 4  | 5  | 6  | 7  | 10 | 11 | 12 |   |

| Octal        | 4 | 4 | 5  | 6  | 7  | 10 | 11 | 12 | 13 |   |

| J            | 5 | 5 | 6  | 7  | 10 | 11 | 12 | 13 | 14 |   |

|              | 6 | 6 | 7  | 10 | 11 | 12 | 13 | 14 | 15 |   |

|              | 7 | 7 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |   |

|              |   | 1 |    |    |    |    |    |    |    | į |

Figure 2-2. Octal Addition Table

The table is useful in adding two octal numbers, which is the most common application the programmer will require.

Example: Add the octal numbers 642351 and 162534.

### Notation Convention

Wherever the possibility of confusion exists, a subscript notation is used to indicate to which system a given number belongs. For example, 1010 could be a binary representation of the decimal number 10, an octal representation of the decimal number 520, or the decimal number 1010<sub>10</sub>. If a number is expressed in binary notation the subscript is used: 1010<sub>2</sub>. Octal numbers are shown with a subscript 123<sub>8</sub>. Decimal numbers are shown with a subscript 10: 876<sub>10</sub>. If it is evident from the text which notation is used, the subscript is omitted.

### Decimal-To-Binary Conversion

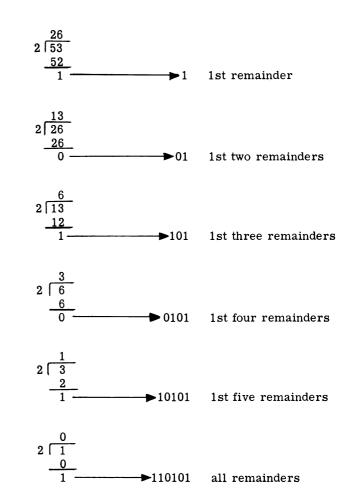

To convert a decimal number to binary, divide the decimal number repeatedly by 2. After each division,

write down the remainder in sequence from right to left. The remainders will be the binary equivalent of the initial decimal number. Note that each division by two leaves either a 0 or a 1 as a remainder.

Example: Find the binary equivalent of the decimal 53.

### Binary-to-Decimal

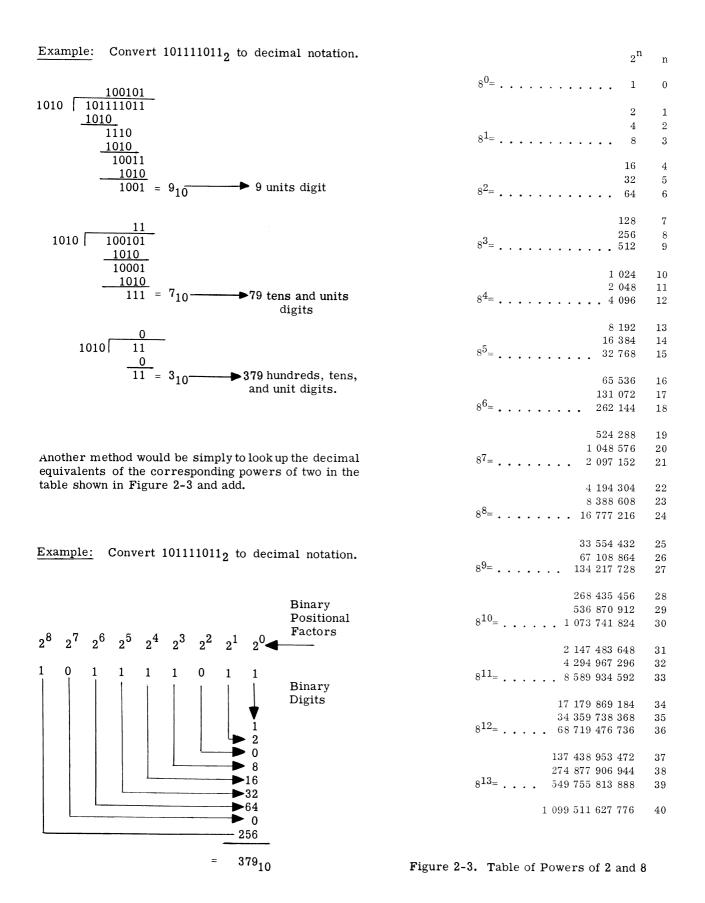

Binary numbers can be converted to decimal by the same method as decimal-to-binary conversion, except that the division is by  $10_{10}$  expressed in binary (1010) and the arithmetic is in binary. After each division, the binary remainder is converted to a decimal digit.

The remainders, in reverse sequence, are the decimal equivalent of the original binary number.

(6) = 225

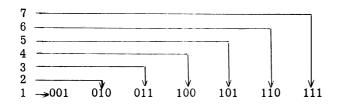

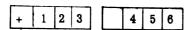

### Binary-To-Octal Conversion

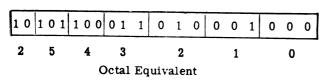

Converting numbers from binary to octal notation is a simple mechanical procedure. Three binary digit positions are the equivalent of one octal bit position. Thus, a 15-bit number, such as 101 001 110 111 001<sub>2</sub>, is a 5 digit octal number when converted. To convert, the binary digits are separated into groups of three, beginning on the right. Each group of three is evaluated individually; the right-most bit has a weight of 1, the center bit is 2, and the left-most bit equals 4. Assuming 1-bits in all three positions of a group, the highest value expressible is 7, which is the largest octal digit.

Example: Convert 1010011101110012 into octal notation.

| 84         | 83       | 8 <sup>2</sup> | 81       | 80       | Octal Position Factors            |

|------------|----------|----------------|----------|----------|-----------------------------------|

| 421        | 421      | 421            | 421      | 421      | Conversion Weight                 |

| 101<br>= 5 | 001<br>1 |                | 111<br>7 | 001<br>1 | Binary Number<br>Octal Equivalent |

### Octal-to-Binary Conversion

By reversing the above process, conversion from octal to binary notation is simplified. Beginning with the right-most digit of the octal number, each digit is converted to its binary equivalent. Each octal digit, upon conversion, requires three bit positions.

Example: Convert 12345678 into binary notation.

### Octal-to-Decimal Conversion

One method of converting octal numbers to their decimal equivalents is to 1) convert the octal number to binary and 2) convert the binary equivalent to decimal, by the previously described procedures.

Another method is to use a conversion table and merely look up the equivalent decimal number. For large octal numbers, such conversion tables often run to many pages. The short conversion table in Figure 2-4 is useful in converting octal numbers up to 3777777 (sufficient for GE-225 programming) directly to decimal notation. The table shows the decimal equivalents of all octal digits as a function of their position in the octal number.

To illustrate the use of the table, consider the octal number 1761354. To convert this number to its decimal equivalent, read the equivalent decimal value of each octal digit from the table and add them to find the total decimal equivalent, as shown below:

| Octal Positions               |    |                               |    |            |                 | Decimal Positions |                 |                       |                            |                                 |  |

|-------------------------------|----|-------------------------------|----|------------|-----------------|-------------------|-----------------|-----------------------|----------------------------|---------------------------------|--|

| 8 <sup>6</sup> 8 <sup>5</sup> | 84 | 8 <sup>3</sup> 8 <sup>2</sup> | 81 | 80         | 10 <sup>5</sup> | 10 <sup>4</sup>   | 10 <sup>3</sup> | 10 <sup>2</sup>       | 10 <sup>1</sup>            | 10 <sup>0</sup>                 |  |

| 1 7                           | 6  | 1 3                           | 5  | 4 -> =<br> | 2 2             | 2<br>2<br>6       | 4,<br>9,<br>2,  | 1<br>5<br>5<br>3<br>1 | 4<br>9<br>1<br>7<br>7<br>4 | 4<br>0<br>2<br>2<br>6<br>6<br>4 |  |

| thus, 1761354 <sub>8</sub> =  |    |                               |    |            |                 | 1                 | 6,              | 8                     | 4                          | 410                             |  |

| OCTAL<br>DIGIT | OCTAL DIGIT POSITION |         |        |       |     |    |    |  |  |  |

|----------------|----------------------|---------|--------|-------|-----|----|----|--|--|--|

| VALUE          | 86                   | 85      | 84     | 83    | 82  | 81 | 80 |  |  |  |

| 1              | 262,144              | 32,768  | 4,096  | 512   | 64  | 8  | 1  |  |  |  |

| 2              | 524,288              | 65,536  | 8,192  | 1,024 | 128 | 16 | 2  |  |  |  |

| 3              | 786,432              | 98,304  | 12,288 | 1,536 | 192 | 24 | 3  |  |  |  |

| 4              | _                    | 131,072 | 16,384 | 2,048 | 256 | 32 | 4  |  |  |  |

| 5              | _                    | 163,840 | 20,480 | 2,560 | 320 | 40 | 5  |  |  |  |

| 6              | -                    | 196,608 | 24,576 | 3,072 | 384 | 48 | 6  |  |  |  |

| 7              | -                    | 229,376 | 28,672 | 3,584 | 448 | 56 | 7  |  |  |  |

Figure 2-4. Octal-to-Decimal Conversion Chart

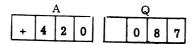

### Decimal-To-Octal Conversion

Decimal-to-octal conversion can be done by first converting the decimal number to its binary equivalent, then reconverting the resulting binary number to octal notation.

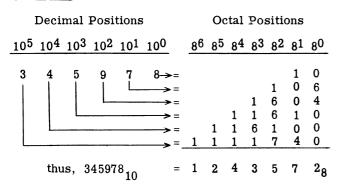

Another method involves the use of the two tables in Figure 2-5. The octal equivalents of the decimal digits are found in the upper table and are then added octally. The lower table assists in the required octal addition by permitting the octal equivalents to be added in decimal, a column at a time, then converted to octal notation.

### CONVERSION CHART

| DECIMAL | DECIMAL POSITION |          |                 |          |                 |     |  |  |  |

|---------|------------------|----------|-----------------|----------|-----------------|-----|--|--|--|

| DIGIT   | 10 <sup>5</sup>  | $10^{4}$ | 10 <sup>3</sup> | $10^{2}$ | 10 <sup>1</sup> | 100 |  |  |  |

| 1       | 303, 240         | 23,420   | 1,750           | 144      | 12              | 1   |  |  |  |

| 2       | 606,500          | 47,040   | 3,720           | 310      | 24              | 2   |  |  |  |

| 3       | 1,111,740        | 72,460   | 5,670           | 454      | 36              | 3   |  |  |  |

| 4       | 1,415,200        | 116,100  | 7,640           | 620      | 50              | 4   |  |  |  |

| 5       | 1,720,440        | 141,520  | 11,610          | 764      | 62              | 5   |  |  |  |

| 6       | 2,223,700        | 165,140  | 13,560          | 1,130    | 74              | 6   |  |  |  |

| 7       | 2,527,140        | 210,560  | 15,530          | 1,274    | 106             | 7   |  |  |  |

| 8       | 3,032,400        | 234,200  | 17,500          | 1,440    | 120             | 10  |  |  |  |

| 9       | 3,335,640        | 257,620  | 21,450          | 1,604    | 132             | 11  |  |  |  |

OCTAL EQUIVALENTS OF DECIMAL NUMBERS

| DECIMAL | OCTAL | DECIMAL | OCTAL | DECIMAL | OCTAL           |

|---------|-------|---------|-------|---------|-----------------|

| 1       | 1     | 15      | 17    | 29      | $3\overline{5}$ |

| 2       | 2     | 16      | 20    | 30      | 36              |

| 3       | 3     | 17      | 21    | 31      | 37              |

| 4       | 4     | 18      | 22    | 32      | 40              |

| 5       | 5     | 19      | 23    | 33      | 41              |

| 6       | 6     | 20      | 24    | 34      | 42              |

| 7       | 7     | 21      | 25    | 35      | 43              |

| 8       | 10    | 22      | 26    | 36      | 44              |

| 9       | 11    | 23      | 27    | 37      | 45              |

| 10      | 12    | 24      | 30    | 38      | 46              |

| 11      | 13    | 25      | 31    | 39      | 47              |

| 12      | 14    | 26      | 32    | 40      | 50              |

| 13      | 15    | 27      | 33    | 41      | 51              |

| 14      | 16    | 28      | 34    | 42      | 52              |

Figure 2-5. Decimal-to-Octal Conversion Charts

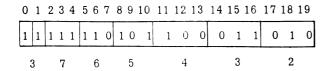

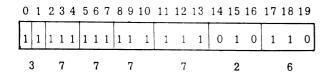

Example: Convert 345978<sub>10</sub> to octal notation.

Adding the  $8^0$  column in decimal gives  $10_{10}$ , which is  $12_8$ , according to the lower table in Figure 2-5. Writing the 2, carrying a 1 into the  $8^1$  column, and adding in decimal gives  $7_8$  and no carry; write the 7. Adding the  $8^2$  column in decimal gives  $21_{10}$ , which is  $25_8$ . Writing the 5, carrying a 2 into the  $8^3$  column, and adding gives  $11_{10}$  or  $13_8$ . Writing the 3 and carrying the 1 into the  $8^4$  column gives  $4_8$ , no carry; write the 4. The  $8^5$  column gives 2 and the  $8^6$  column is 1.

GE-225

II-6 October 1963

### DATA WORDS

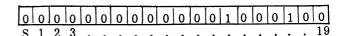

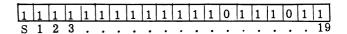

In the GE-225, the word (or basic unit of information) consists of 20 binary digits. Words can be stored in 4096 to 16,384 core storage locations, each of which is individually addressable. Additional random access and sequential access storage is available in MRADS units and magnetic tape.

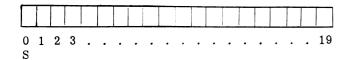

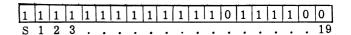

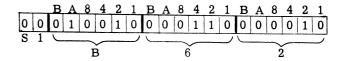

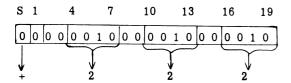

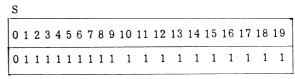

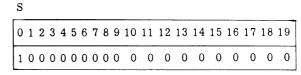

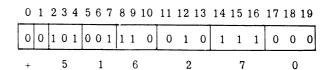

A word can be an instruction, a binary data word or number, a binary-coded-decimal word (for expressing either alphabetic or numeric characters), or any pattern of 20 bits the programmer so desires. The 20 bit positions of the GE-225 word are depicted in Figure 2-6. S (or 0) refers to the sign position, 1 indicates the high-order bit position, 2 the next highest, and so on. Bit position 19 indicates the low-order bit position.

Figure 2-6. Basic GE-225 Word

### Binary Data Words

When a word is interpreted by the GE-225 as binary data, the 0 (or S) position acts as the arithmetic sign. A 0-bit in the sign position indicates that the word is positive; a 1-bit indicates that the word or number is negative. In binary words, 1-bits in positions 1 through 19 indicate values corresponding to the powers of two. A 1-bit in bit position 1 equals  $2^{18}$  or  $262,144_{10}$ ; in position 2, a 1-bit equals  $2^{17}$  or  $131,072_{10}$ ; in position 19,  $2^0$  or 1. The largest positive decimal number that can be expressed in the 20-bit binary word is  $2^{19}$  - 1, or  $524,287_{10}$ .

Negative numbers are expressed in binary form by placing a 1-bit in the sign position and the 2's complement of the desired number in bit positions 1 through 19.

To express a given negative number:

- 1. Write the positive number in binary

- Change it to the 2's complement form by

a) converting all 1-bits to 0-bits and all 0

- bits to 1-bits andb) adding a 1-bit to the least significant bit position.

For example, to express the decimal  $-68_{10}$  in binary,

Inverting all bit positions gives:

Adding a 1-bit to bit position 19:

The largest negative number that can be expressed in the 20-bit binary word is  $2^{19}$ , or  $524,288_{10}$ .

A machine instruction is provided for automatically converting a positive number to a negative number. Also, in subtract operations involving positive numbers, the required complements are automatically formed.

### Double Length Binary Words

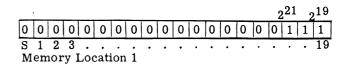

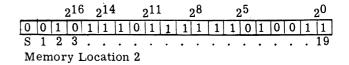

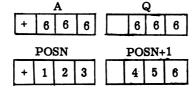

The GE-225 can perform double length data word operations. Double length words consist of two 20-bit words which are normally stored in adjacent memory locations. For processing, they are treated as a single word consisting of a sign bit and 38 data bits.

For illustration, consider the decimal 3,862,483<sub>10</sub>. In binary, this number would be stored in two adjacent memory locations:

write  $+68_{10}$  in binary:

The most significant half of the double word is stored in the first memory location. The adjacent (higher) location contains the least significant half of the word. Bit positions in the second memory location have values corresponding to the first nineteen powers of two ( $2^0$  through  $2^{18}$ ), while those of the first (lower) memory location correspond to the second nineteen powers of two ( $2^{19}$  through  $2^{37}$ ). The signs of both locations are the same, 0 for plus or 1 for minus. Double length negative numbers are expressed in the 2's complement form.

### Floating-Point Notation

The auxiliary arithmetic unit (AAU) expands the arithmetic capability of the GE-225 to include normalized and unnormalized floating-point operations. Representation of floating-point numbers is discussed in the section, Auxiliary Arithmetic Unit Operations.

GE-225 installations, with or without the AAU, can process floating point arithmetic with utility subroutines provided by General Electric for this purpose. However, for voluminous floating point calculations, the AAU provides greater efficiency, because of its speed and capacity.

### Binary-Coded-Decimal Data Words

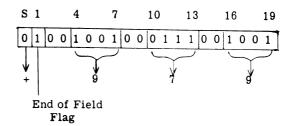

In addition to its basic binary capability, the GE-225 can process binary-coded-decimal (BCD) or alphanumeric data. The six bit positions of the BCD code may be used to express 64 character configurations, including all alphanumeric and special characters of the GE-225 character set.

The 6-bit code consists of two groups:

| ZONE<br>GROUP | NUMERIC<br>GROUP |  |  |  |  |  |  |

|---------------|------------------|--|--|--|--|--|--|

| ВА            | 8 4 2 1          |  |  |  |  |  |  |

|               |                  |  |  |  |  |  |  |

The numeric bits correspond to the first four powers of two, as they do in the binary system, and can express up to 16 numeric values, 0 through 15. The zone bits provide for coding alphabetic and special characters.

Selected characters are shown below in BCD. All GE-225 characters and their equivalent BCD codes are shown in the Appendix.

In the BCD mode, the GE-225 word can contain three characters, occupying 18 bit positions (2 through 19).

|    | В | A | 8 | 4 | 2 | 1 |

|----|---|---|---|---|---|---|

| 1  | 0 | 0 | 0 | 0 | 0 | 1 |

| 5  | 0 | 0 | 0 | 1 | 0 | 1 |

| 9  | 0 | 0 | 1 | 0 | 0 | 1 |

| Α  | 0 | 1 | 0 | 0 | 0 | 1 |

| N  | 1 | 0 | 0 | 1 | 0 | 1 |

| R  | 1 | 0 | 1 | 0 | 0 | 1 |

| /  | 1 | 1 | 0 | 0 | 0 | 1 |

| Z  | 1 | 1 | 1 | 0 | 0 | 1 |

| \$ | 1 | 0 | 1 | 0 | 1 | 1 |

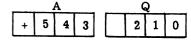

The remaining two bit positions (S and 1) do not normally contain data, but are used for program and printer control purposes discussed later. A representative GE-225 BCD word is shown:

Double length BCD words are possible to express alphanumerics consisting of as many as six characters.

Optional instructions permit variable length BCD aritmetic operations. Negative numbers must be expressed in 10's complement form with a 1-bit in the sign position. Note that, in BCD numerics, the zone bits (2, 3, 8, 9, 14, 15 bit positions) are set to zero. Although the BCD word contains only three numerics, the variable length feature permits operations with BCD numbers of any practical length.

### Examples of BCD quantities:

| Decimal | BCD word(s)     |

|---------|-----------------|

| + 10    | + 0 1 0         |

| + 989   | + 9 8 9         |

| - 10    | _ 9 9 0         |

| - 989   | - 0 1 1         |

|         |                 |

| + 87649 | + 0 8 7 + 6 4 9 |

| - 87649 | - 9 1 2 - 3 5 1 |

### INSTRUCTION WORDS

Instructions are expressed as 20-bit words. Three different formats are used.

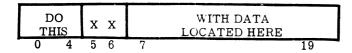

Format I. All instructions involving reference to memory are written in Format I. Included are arithmetic, memory transfer, and certain branch instructions. Complete descriptions of these instructions are provided in subsequent sections.

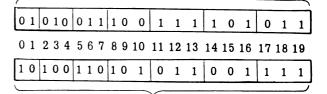

The format for memory reference instructions is:

OR

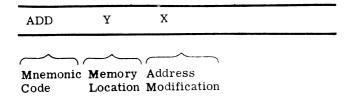

The five bits (0 through 4) indicate the operation to be performed, such as add, subtract, read cards, etc.

Bits 5 and 6 provide for automatic address modification by stipulating whether the contents of one of several X registers are to be used to modify the operand address. Automatic address modification is treated in Section V.

Bits 7 through 19 designate the operand address; that is, the memory location where the data to be added, subtracted, etc., is stored.

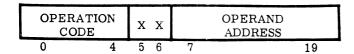

About 60 of the over 300 instructions in the GE-235 repertoire require operand addresses. Instructions without operand addresses cannot be address modified. This permits bits 5 and 6, and 7 through 19 to be used for other purposes. Instructions in this category (no operand address) are called general instructions, Format III.

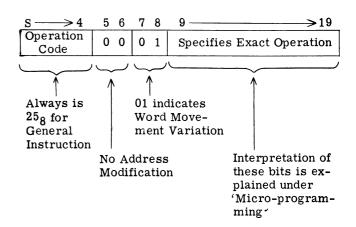

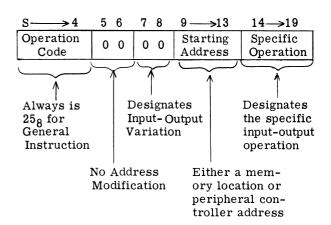

Format II. All instructions in data transfer (excluding memory transfer) and input-output categories and most internal test-and-branch instructions are written in Format II. Instructions in this format are commonly called general instructions and have the same operation code in bit positions Sthrough 4 (10 101, or 25<sub>8</sub>). Format II has three variations, corresponding to the three general categories mentioned.

The <u>word movement</u> variation is for instructions involving full word transfers between arithmetic registers and the arithmetic unit. They assume this format:

The <u>input-output</u> variation is used for instructions involving the central processor and peripherals. Bits S through 4 contain 25<sub>8</sub> (10 101) and bits 7 and 8 are 0's. The remaining bits specify the input-output operation. The format is as follows:

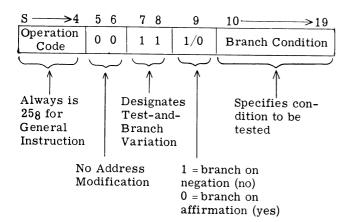

The <u>test-and-branch</u> variation is used for instructions that provide for breaking the normal sequence of instruction execution. These instructions are identified by  $25_8$  (10 101) in bit positions S through 4 and 1-bits

GE-225

II-9 October 1963

in positions 7 and 8. The test condition for determining a branch to another instruction is specified by bit positions 9 through 19. The format is:

The specific bit patterns for all Format II instructions can be found by converting the octal equivalent of the instructions to binary. The octal form of each instruction is included in the instruction descriptions in subsequent sections.

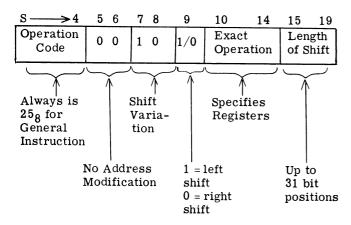

Format III. Only shift instructions are written in Format III. Shift instructions are used to shift one or more bits within or between arithmetic registers. Bit positions S through 4, designating the operation code, contain 258; bits 7 and 8 contain 1 and 0 respectively, identifying a shift operation; bit 9 indicates direction of shift (right or left); bits 10 through 14 identify the registers involved; bits 15 through 19 designate the number of bits to be shifted. The format is:

While it is possible to prepare programs for GE-225 processing directly in binary notation, it is infrequently done because such programming is tedious and subject to clerical error. However, a knowledge of binary notation and instruction structure is essential in micro-programming (the building or creating of instructions by the programmer). Micro-programming is discussed in a later section.

In program debugging and patching, octal notation is frequently used for 3 reasons: 1) octal notation provides the programmer with a more meaningful presentation than does binary, 2) the GE 225 provides printed outputs (during GAP program assembly) and memory dumps in octal notation, and 3) octal can easily be converted to binary or decimal. On the other hand, binary is difficult to reador write; also it is tedious to convert to the familiar decimal notation.

### GE-225 Octal Notation

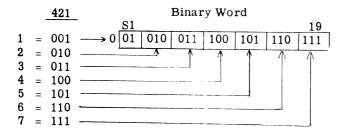

Conversion of GE-225 words from binary to octal or octal to binary is a simple mechanical procedure.

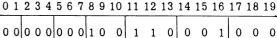

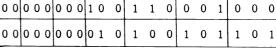

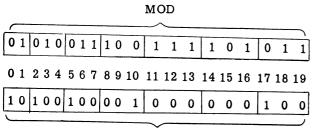

Given the GE-225 binary word:

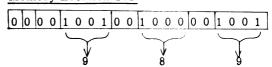

Starting on the right, divide the word into groups of three bits (giving six groups of three, and one group of two) and assign octal values to the bit positions as shown:

| 01 | 101 | 011 | 100 | 101 | 100 | 111 | ←—Bits          |

|----|-----|-----|-----|-----|-----|-----|-----------------|

| 1  | 2   | 3   | 4   | 5   | 6   | 7   | Coctal<br>Group |

| •  | •   | •   |     | •   |     |     | No.             |

Evaluate each group and write the equivalent octal digit:

The result of the binary-to-octal conversion is a 7-digit number in place of the longer, less meaningful 20-bit binary word.

Note that any GE-225 word can be represented as a 7-digit octal number, whether it be a data word or an instruction.

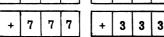

The representation of the number 12345678 in binary is accomplished by reversing the above process:

Because of the simplicity and convenience of octal notation, it is used freely in the balance of the manual to simplify explanations and to provide familiarity.

### SYMBOLIC PROGRAMMING

Programs for the GE-225 information processing system are generally written in symbolic coding. The programmer is thus able to write instructions in meaningful symbolic codes, rather than the absolute numeric code language of the computer. This relieves him of much time-consuming clerical detail, especially important in writing lengthy programs.

### The General Assembly Program

The General Assembly Program transforms symbolic mnemonic codes into numeric machine language for each instruction in the repertoire of the GE-225 system. These mnemonic codes have been chosen to provide significance and easy recognition of the operation performed. For example, the mnemonic code "ADD" instructs the General Assembly Program to build a numeric instruction by which the GE-225 system performs algebraic addition.

- 1. The symbolic language used by the programmer in coding the source program.

- The actual assembly program (on punched cards, perforated tape, or magnetic tape) supplied by General Electric that processes the source (or symbolic) program into a ready to execute machine language (or object) program.

The symbolic language consists of these standardized mnemonic codes divided into two general categories:

- 1. The pseudo-instructions used by the General Assembly Program for memory location assignments, program control constants, program constant storage, and program control during the assembly operation. These do not correspond to "real" GE-225 machine instructions.

- 2. The mnemonic operation codes corresponding to the more than 300 machine instructions of the GE-225 system.

There generally is a one-to-one relationship between the mnemonic operation code prepared by the programmer and the machine instruction appearing in the object program as assembled by the General Assembly Program. A single pseudo-instruction, however, can result in the generation of from one to several machine instructions during the assembly operation. The pseudo-instructions are described in a separate manual, General Assembly Program II (CD225F1.006/007), which also discusses all phases of the assembly operation and operating procedures.

The machine instructions for the GE-225 central processor are described in Sections V, VI, and VII of this manual. Instructions for the various peripheral subsystems are described in the separate manuals covering these subsystems, as listed in the "Preface" and "Contents."

A complete, brief listing of General Assembly Program instructions in both alphabetical and octal order is given in Appendices II and III.

# SECTION III

# CENTRAL PROCESSOR ORGANIZATION

The central processor performs all arithmetic and logical functions in the GE-225 system and acts as a central control for all internal and peripheral operations. Because the program (or instructions for data processing) is held in memory like the data to be processed, the GE-225 is known as a stored program computer.

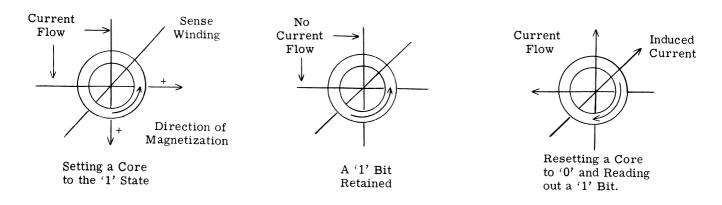

#### MAGNETIC CORE STORAGE