QUANTUM

# PRODUCT DESCRIPTION TECHNICAL REFERENCE MANUAL

Q500 51/4" Media Fixed Disk Drive

QUANTUM CORPORATION 1804 McCarthy Boulevard Milpitas, California 95035 (408) 262-1100 TWX 910 338 2203

© Copyright QUANTUM CORPORATION 1983 All Rights Reserved

# Q500 SERIES DISK DRIVE

Technical Reference Manual

81-50466 Rev A

September 1984

This manual does not contain certain items of information not available at the time of printing. These omissions are noted, where possible, in the manual.

Quantum reserves the right to make changes and/or improvements to its products without incurring any obligation to incorporate such changes or improvements in units previously sold or shipped.

Quantum publishes descriptive Brochures and Data Sheets, a Product Description/OEM Manual, and a Technical Reference Manual for each product line. In addition, important changes to a product are conveyed in the form of a Technical Support Bulletin sent to all product customers of record. Those changes which alter manual content are covered by publishing Addenda to the affected manual.

Quantum publications may be requested from your Quantum Sales Representative, or may be ordered from Quantum in the same manner as spare parts.

Comments on all Quantum publications or their use are invited. Please use the Comment Form at the back of this manual.

© Copyright 1984 by Quantum Corporation, Milpitas, California, USA

Publication No. 81-50466, Rev A

#### **UL/CSA**

UL recognition granted under File No. E78106 Project #83SC5587 CSA certification applied for under File No. LR49896-4

#### WARRANTY

Quantum Model Q500 series disk drives are warranted against defects in material and workmanship for a period of one year from the date of shipment. The warranty includes parts and labor. This is a limited warranty and further details can be obtained from your Quantum sales representative. All requests for service should be directed to the Quantum service center in your area.

#### **PATENTS**

Product described herein is covered by Patent #4396959 and other U.S. and foreign pending patent applications.

#### **SERVICE CENTERS**

Eastern United States Quantum Service Center 2 Industrial Way Salem, New Hampshire 03079 603-893-2672

International

Computer Repair Center, Ltd. Thame Park Industrial Estate Thame, Oxon OX93RS England 084-421-5471 Western United States Quantum Service Center 1804 McCarthy Boulevard Milpitas, California 95035 408-262-1100

Europe

Quantum Service Center Hahnstrasse 70 B-6000 Frankfurt/M 71 West Germany

© Quantum Corporation 1984 All rights reserved. Q500 Series and AIRLOCK are registered trademarks of Quantum Corporation. Printed in U.S.A.

# REVISION CONTROL RECORD

Quantum Q500 Series Manual — Publication No. 81-50466

| Page / | REV |

|--------|-----|--------|-----|--------|-----|--------|-----|

| i      | A   | 1-14   | A   | 1-34   | A   | 2-7    | A   |

| ii     | A   | 1-15   | A   | 1-35   | A   | 2-8    | A   |

| iii    | A   | 1-16   | A   | 1-36   | A   |        |     |

| iv     | Α   | 1-17   | A   | 1-37   | A   | 3-1    | A   |

| V      | A   | 1-18   | A   | 1-38   | A   | 3-2    | Α   |

| vi     | A   | 1-19   | Α   | 1-39   | A   | 3-3    | Α   |

| vii    | A   | 1-20   | Α . | 1-40   | A   | 3-4    | Α   |

|        |     | 1-21   | Α   | 1-41   | A   | 3-5    | Α   |

| 1-1    | A   | 1-22   | A   | 1-42   | A   |        |     |

| 1-2    | A   | 1-23   | A   | 1-43   | A   | 4-1    | A   |

| 1-3    | A   | 1-24   | A   | 1-44   | A   | 4-2    | A   |

| 1-4    | A   | 1-25   | A   | 1-45   | A   | 4-3    | A   |

| 1-5    | A   | 1-26   | Α   | 1-46   | A   |        |     |

| 1-6    | A   | 1-27   | A   |        |     | 5-1    | A   |

| 1-7    | A   | 1-28   | A   | 2-1    | A   | 5-2    | A   |

| 1-8    | A   | 1-29   | Α   | 2-2    | A   | 5-3    | Α   |

| 1-9    | A   | 1-30   | Α   | 2-3    | A   | 5-4    | A   |

| 1-10   | A   | 1-31   | Α   | 2-4    | A   | 5-5    | A   |

| 1-11   | A   | 1-32   | Α   | 2-5    | A   | 5-6    | Α   |

| 1-12   | A   | 1-33   | Α   | 2-6    | A   | 5-7    | Α   |

| 1-13   | A   |        |     |        |     | 5-8    | A   |

# TABLE OF CONTENTS

| Preface |                                           | vi     |

|---------|-------------------------------------------|--------|

| SECTION | I – PRINCIPLES OF OPERATION               |        |

|         |                                           | 1.1    |

| 1.1     | Model Q500 Block Diagram                  | . 1-1  |

| 1.2     | Model Q500 Drive Mechanism                | . 1-2  |

|         | 1.2.1 Optical Encoder                     | . I-2  |

|         | 1.2.2 Rotary Positioner Assembly          |        |

|         | 1.2.3 Head Stack Assembly                 | . I-3  |

|         | 1.2.4 Disk Stack Assembly                 | . I-3  |

|         | 1.2.5 Base Casting Assembly               |        |

|         | 1.2.6 DC Drive Motor                      |        |

|         | 1.2.7 EMI Band                            |        |

|         | 1.2.8 Air Filtration                      |        |

|         | 1.2.9 Automatic Actuator Lock             |        |

| 1.3     | Drive Electronics                         |        |

|         | 1.3.1 General Features                    |        |

|         | 1.3.2 Data Interface                      | . 1-5  |

|         | 1.3.3 Control Signal Descriptions         | . 1-8  |

|         | 1.3.4 Power Requirements                  | . 1-11 |

|         | 1.3.5 Interface and Drive Select Logic    |        |

|         | 1.3.6 Encoder Board                       |        |

|         | 1.3.7 Drive Control Board                 |        |

|         | 1.3.8 AGC Circuit                         |        |

|         | 1.3.9 P1 and P2 Generation                |        |

|         | 1.3.10 Track 0                            |        |

|         | 1.3.11 Actuator Positioning Circuits      | 1-19   |

|         | 1.2.12 Head Switching Matrix              | . 1-27 |

|         | 1.3.13 Write Data Circuits                |        |

|         | 1.3.14 Read Data Circuits                 |        |

|         | 1.3.15 Motor Microprocessor               | 1-37   |

|         | 1.3.16 Power-On Reset and Power Sense     | 1-43   |

|         | 1.3.17 DC Power, Filter, and Regulators   | 1-44   |

| SECTION | 2: LOGIC CONVENTIONS AND CIRCUIT DIAGRAMS |        |

| 2.1     | Introduction                              |        |

| 2.2     | Logic Symbology                           |        |

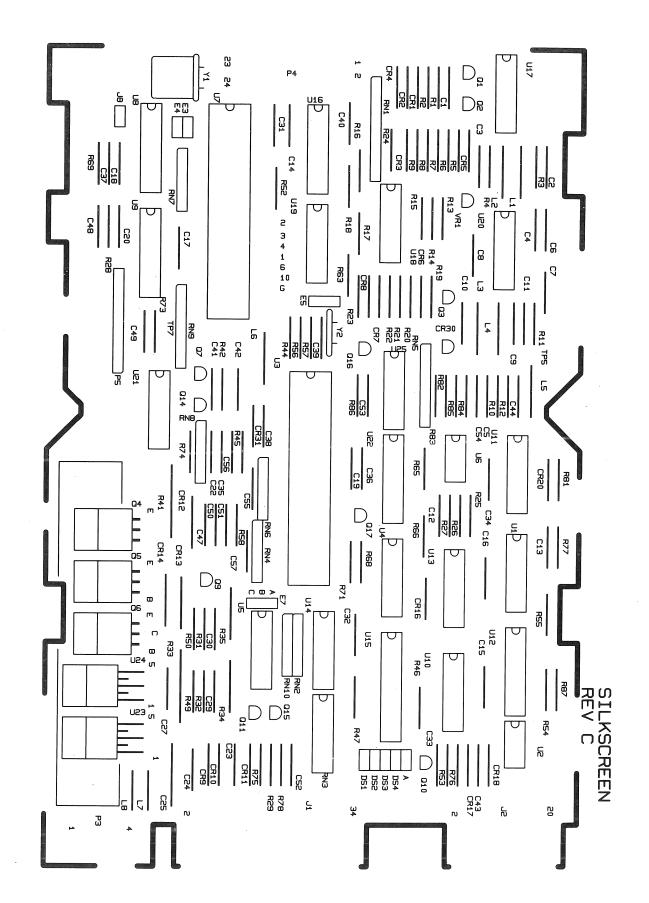

| 2.3     | Component Locations                       |        |

| 2.4     | Circuit Diagrams                          | . 2-2  |

| SECTION | 3: APPLICATIONS                           |        |

| 3.1     | Introduction                              | . 3-1  |

| 3.2     | Special Considerations                    |        |

|         | 3.2.1 Write Fault                         |        |

|         | 3.2.2 Track-To-Track Access Time          |        |

| 3.3     | Errors and Media Defects                  |        |

| 2.0     | 3.3.1 Introduction                        |        |

|         | 3.3.2 Errors                              |        |

|         | 3.3.3 Defect Detection and Reporting      |        |

|         | 3.3.4 Media Quality Criteria              |        |

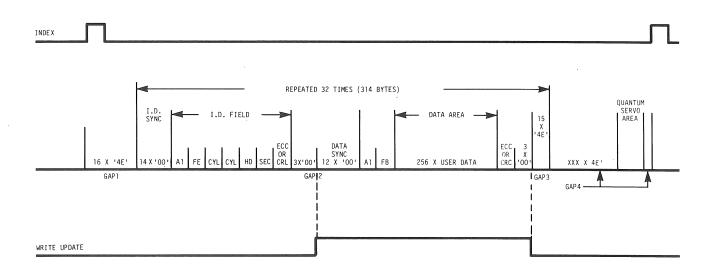

| 3.4     | Track Formatting                          |        |

| 5.1     | 3.4.1 Introduction                        |        |

|         | 3.4.2 Track Format                        |        |

|         | 3.4.3 Sample Format                       |        |

|         | A                                         |        |

# TABLE OF CONTENTS (continued)

| 3.5     | Write Pre-Compensation               | 3-4 |

|---------|--------------------------------------|-----|

| 3.6     | Grounding Procedures                 |     |

| 3.7     | Write Pre-Compensation               | 3-5 |

| 3.8     | Daisy Chain Termination              |     |

| 3.9     | Self Diagnostics                     |     |

| SECTION | N 4: MAINTENANCE                     |     |

| 4.1     | General Information                  | 4-1 |

| 4.2     | Maintenance Precautions              | 4-1 |

| 4.3     | Jumpers and Test Points              | 4-2 |

| 4.4     | Level 1 Maintenance                  | 4-3 |

| 4.5     | Level 2 Maintenance                  | 4-3 |

| SECTION | N 5: Q500 DESCRIPTION AND PARTS LIST |     |

| 5.1     | Illustrated Parts                    |     |

| 5.2     | Parts List                           | 5-3 |

# LIST OF FIGURES

| FIGURE |                                                  | PAGE   |

|--------|--------------------------------------------------|--------|

| 1-1    | Model Q500 Block Diagram                         | 1-1    |

| 1-2    | Model Q500 Mechanical Layout                     | 1-2    |

| 1-3    | Data Signal Driver/Receiver                      |        |

| 1-4    | MFM WRITE DATA Timing                            |        |

| 1-5    | MFM READ DATA Timing                             |        |

| 1-6    | Single Step Mode Timing                          |        |

| 1-7    | Buffered Step Mode Timing                        |        |

| 1-8    | Index Timing                                     |        |

| 1-9    | General Control Timing Requirements              |        |

| 1-10   | Drive Start-Up Current Profile (12V Line)        |        |

| 1-11   | Encoder PCB Block Diagram                        |        |

| 1-12   | Drive Control PCB Block Diagram                  |        |

| 1-13   | AGC Circuit                                      | 1-16   |

| 1-14   | P1 and P2 Generation                             | . 1-17 |

| 1-15   | P1 and P2 Signals vs. Position                   | . 1-18 |

| 1-16   | Track 0 Detector                                 |        |

| 1-17   | Actuator Microprocessor Block Diagram            |        |

| 1-18   | Actuator Drive Block Diagram                     |        |

| 1-19   | Actuator Drive Circuit                           |        |

| 1-20   | Actuator Driver Stage                            |        |

| 1-21   | Servo Peak Detector                              |        |

| 1-22   | Servo Peak Detector Signals                      |        |

| 1-23   | Head Switching Matrix                            |        |

| 1-24   | Write Circuit Block Diagram                      |        |

| 1-25   | Write Data Circuit                               |        |

| 1-26   | Read Channel Block Diagram                       |        |

| 1-27   | Read Channel Front End                           |        |

| 1-28   | U17 Current Source                               |        |

| 1-29   | Cascode Amplifier                                |        |

| 1-30   | Low Pass Filter/Differentiator                   |        |

| 1-31   | Comparator and Simplified Internal Circuit       |        |

| 1-32   | Simplified Circuit Output                        |        |

| 1-33   | Droop Ignore Circuit Waveforms                   |        |

| 1-34   | Zero-Crossing Detector/Droop Ignore Circuit      |        |

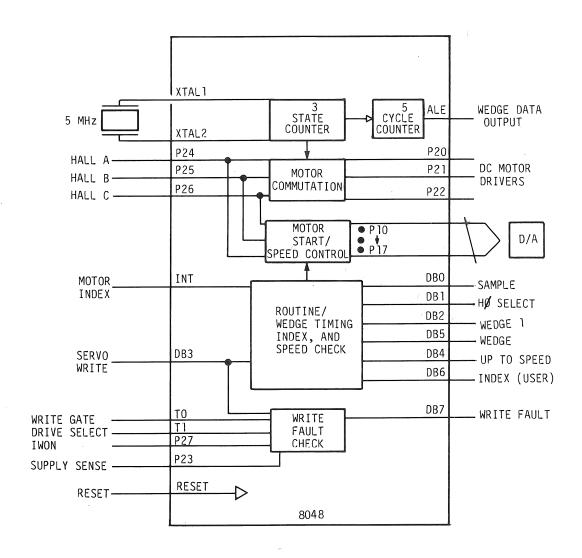

| 1-35   | Motor Microprocessor Block Diagram               |        |

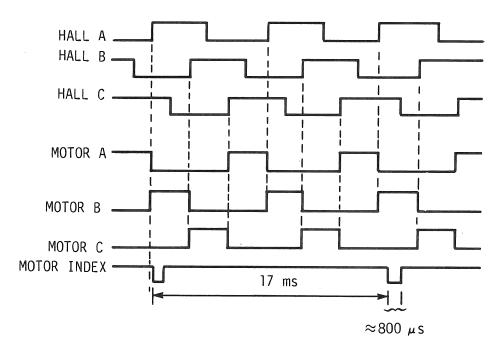

| 1-36   | DC Motor Commutation Timing Diagram              |        |

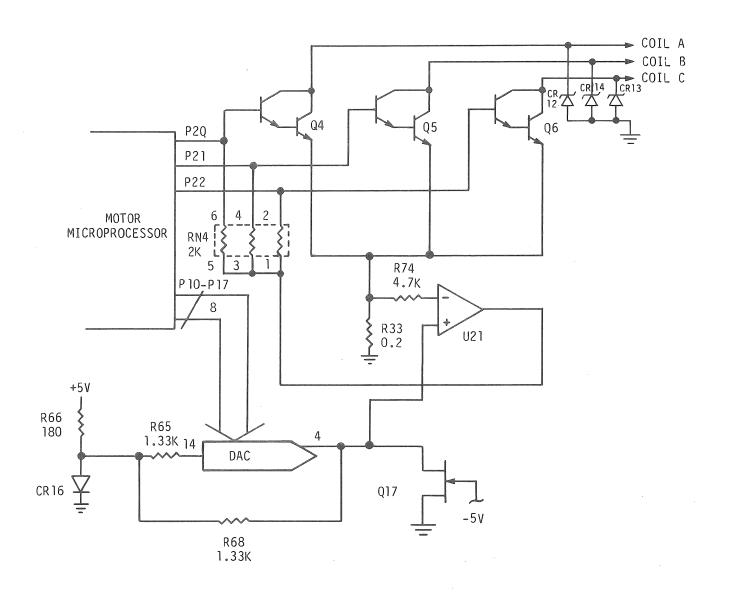

| 1-37   | Motor Drive Circuit (Simplified)                 |        |

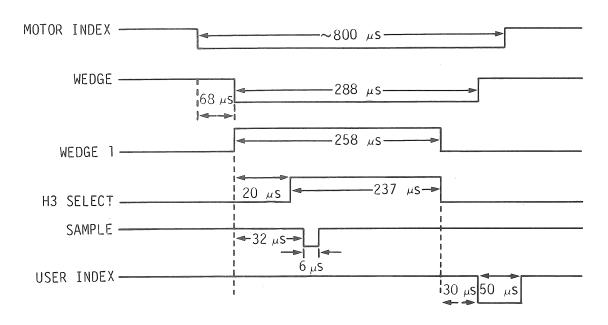

| 1-38   | Wedge and Index Timing                           |        |

| 1-39   | Write Fault Determination                        |        |

| 1-40   | Power-On Reset Circuit                           |        |

| 1-41   | -5V Converter Circuit Schematic                  |        |

| 1-42   | Waveform in -5V Converter Circuit                |        |

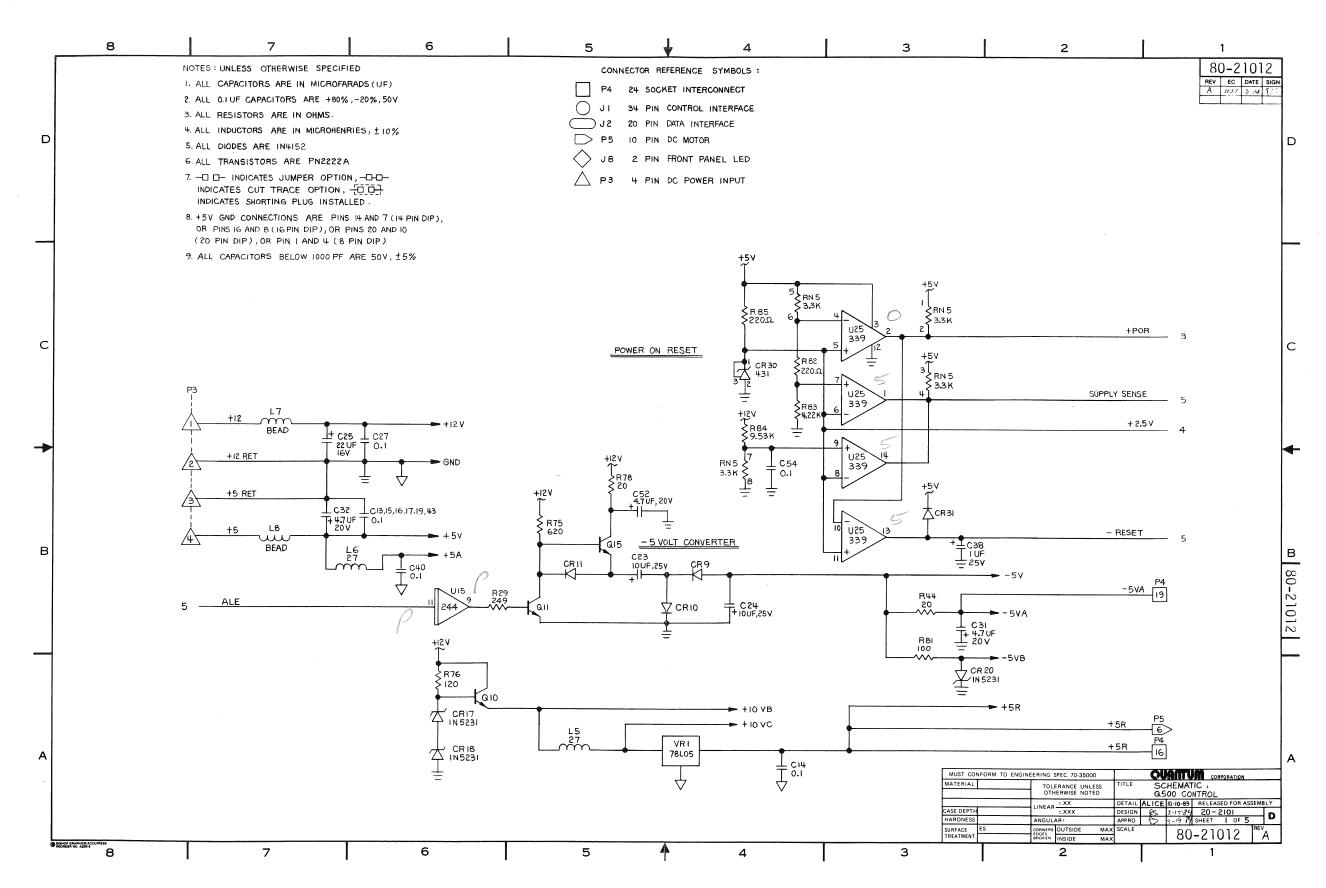

| 2-1    | Power-On Reset, Regulators, and Filters Circuits |        |

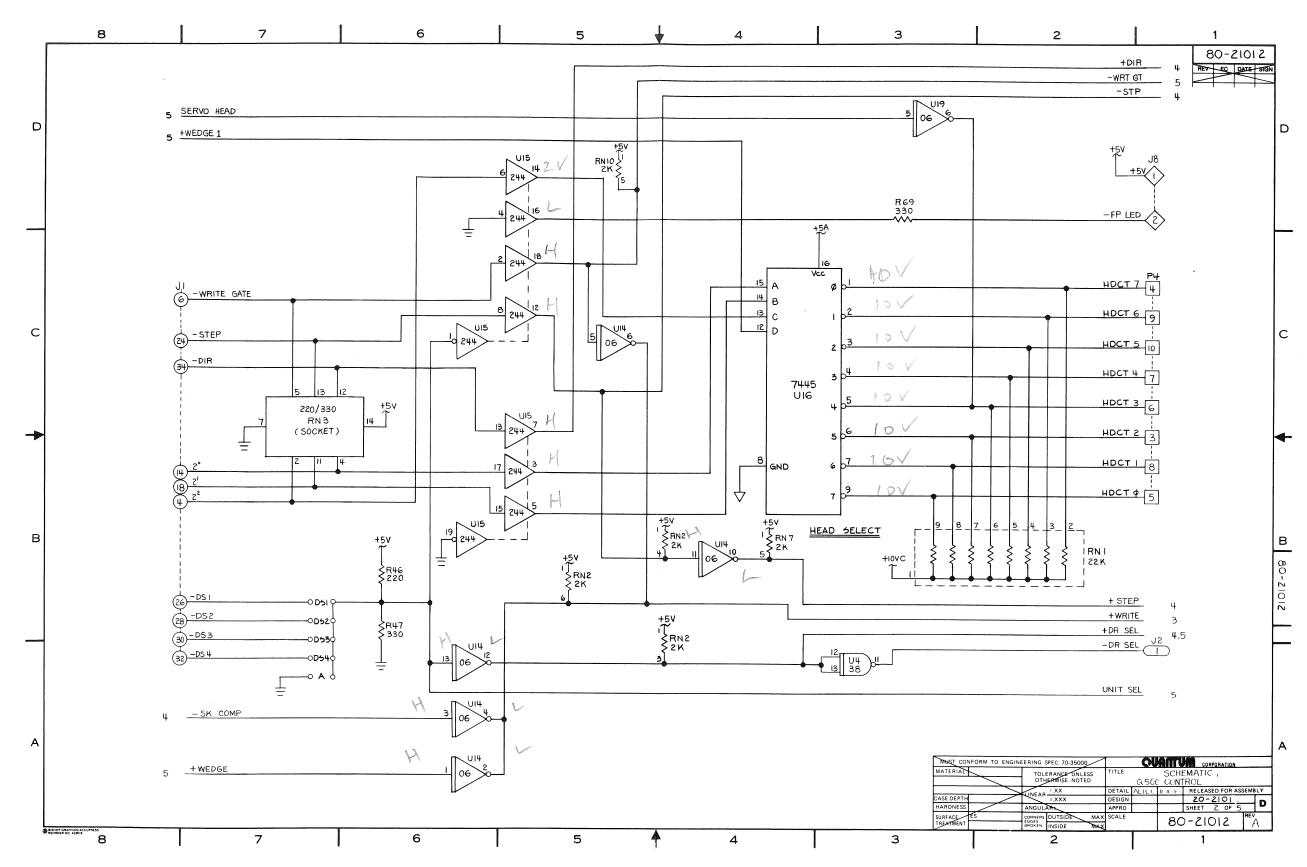

| 2-2    | Interface Control and Head Select Circuits       |        |

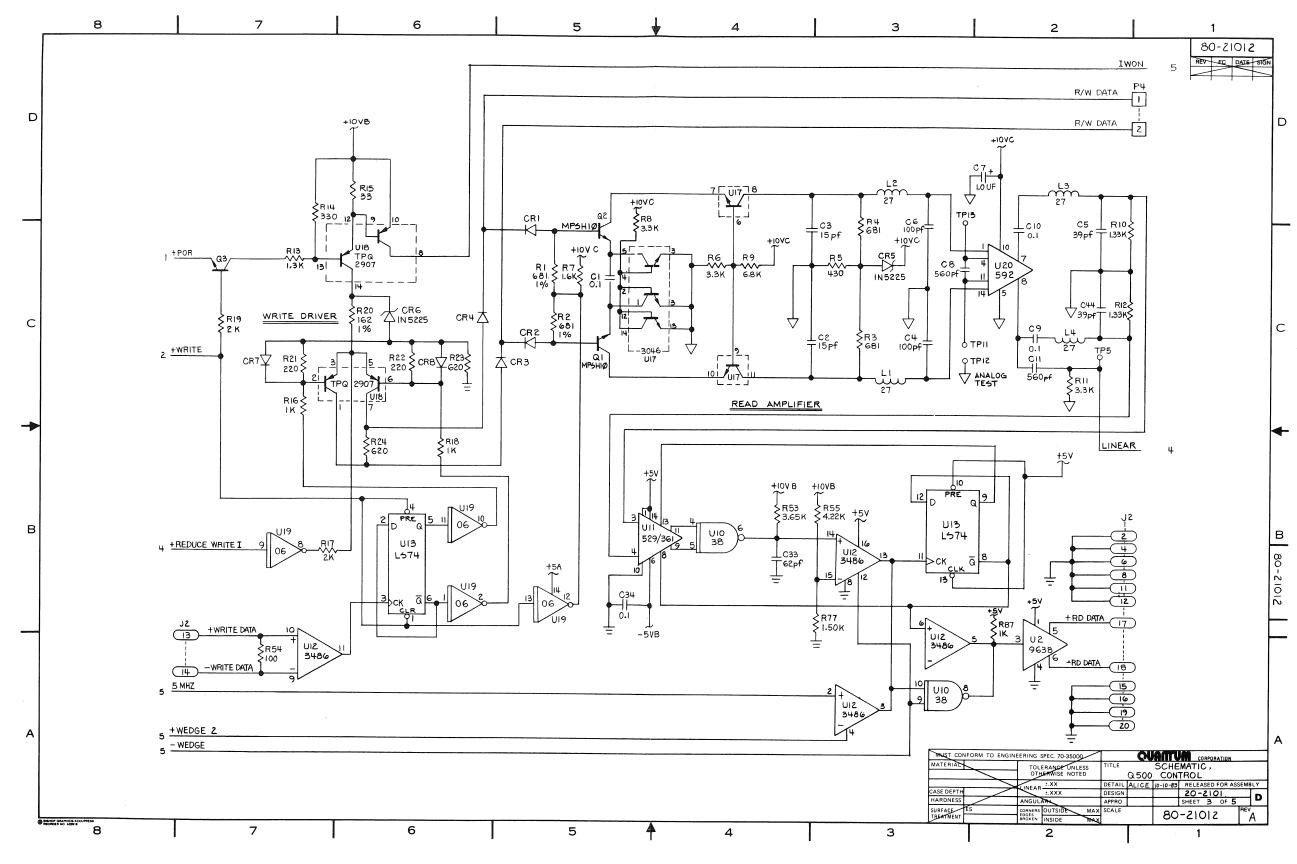

| 2-3    | Read/Write Circuits                              |        |

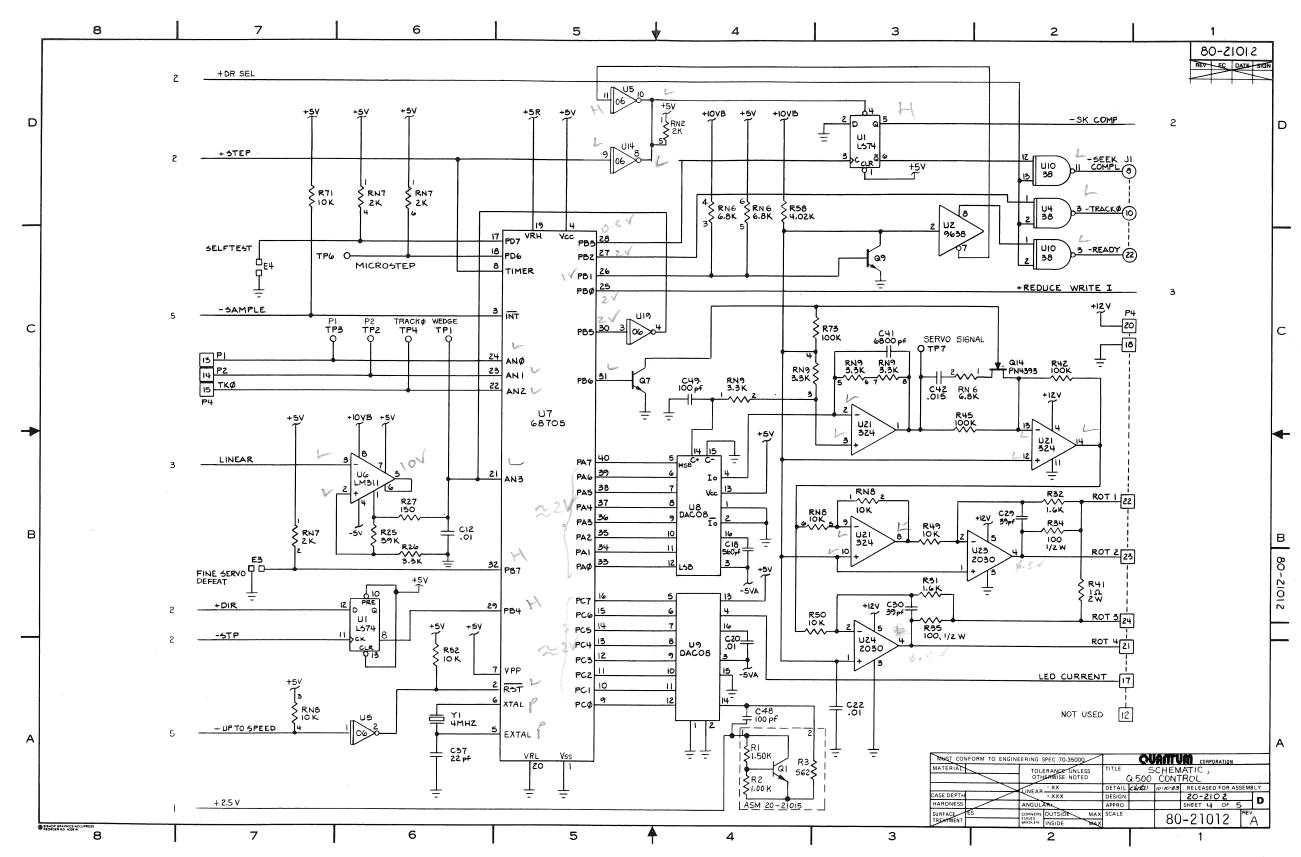

| 2-4    | Actuator Positioning and Control Logic Circuits  |        |

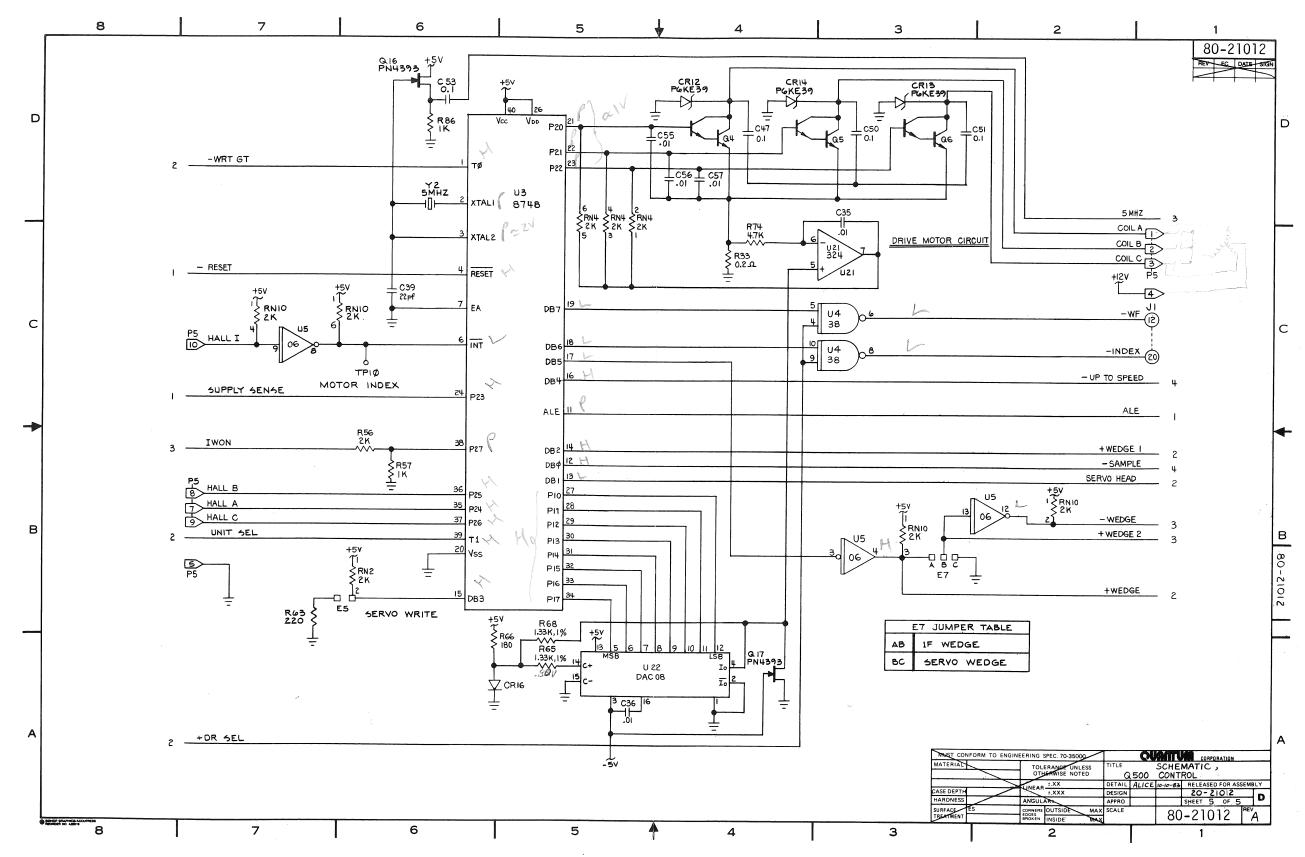

| 2-5    | Motor Microprocessor and Motor Driver Circuits   |        |

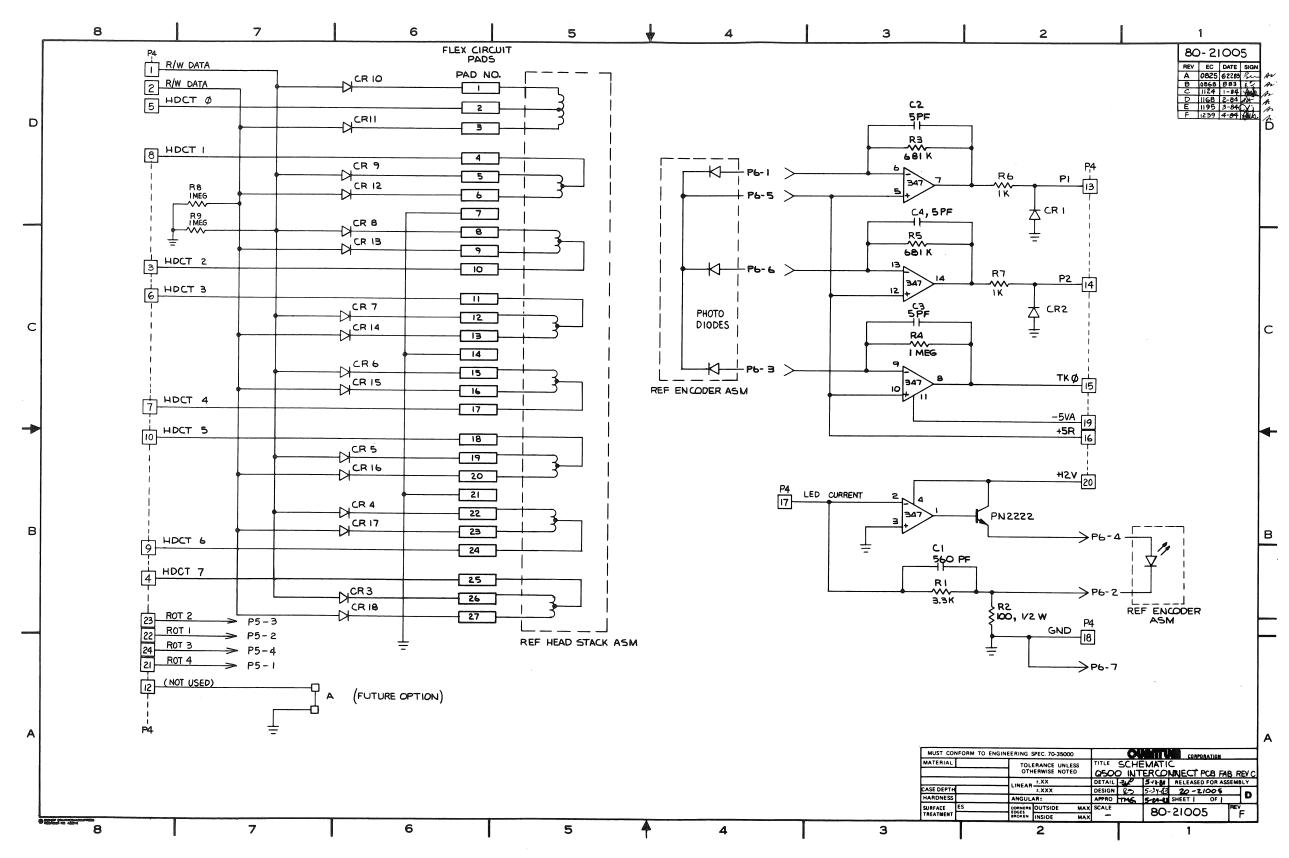

| 2-6    | Encoder PCB (Under Bubble)                       |        |

| 2-7    | Sample Track Format                              |        |

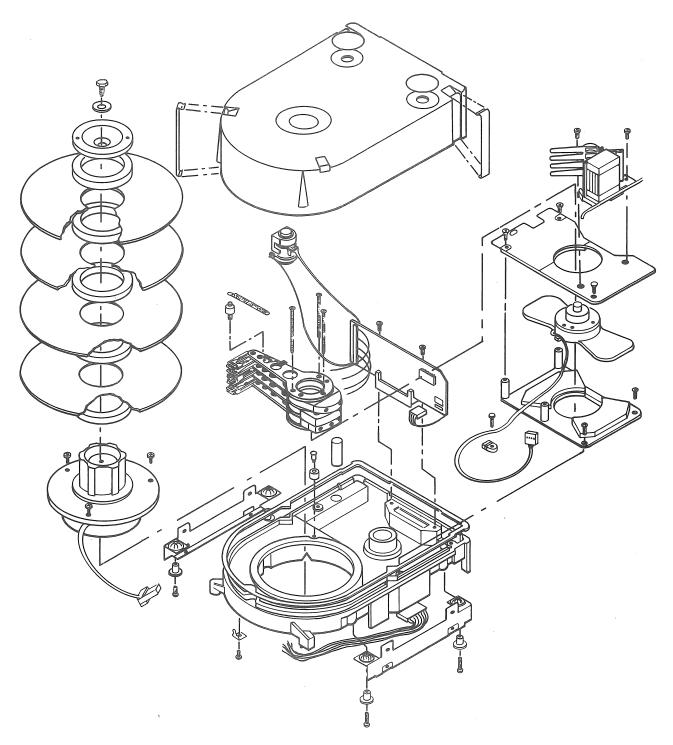

| 2-8    | Q500 Exploded Parts Diagram                      |        |

| 2-9    | Drive Control PCB Layout                         |        |

# LIST OF TABLES

| TABLE |                                | PAGE |

|-------|--------------------------------|------|

| 1-1   | Data Cable Pin Designations    | 1-6  |

| 1-2   | Control Cable Pin Designations | 1-8  |

| 1-3   | DC Power Requirements          | 1-11 |

| 1-4   | D/A Actuator Signals           | 1-22 |

| 2-1   | Q500 Component Codes           | 2-2  |

| 3-1   | Write Precompensation          | 3-4  |

| 4-1   | Jumper Definitions             |      |

| 4-2   | Test Point Definitions         | 4-2  |

| 4-3   | Connector Descriptions         | 4-2  |

#### **PREFACE**

## **DOCUMENT OBJECTIVE**

The Quantum Q500 Disk Drive Technical Reference Manual describes the principles of operation, major circuits, component parts, maintenance, and applications of the Q500 drive.

#### INTENDED AUDIENCE

This manual is intended for experienced Design Engineers, Applications Engineers, Software Programmers, and Repair Technicians using the Q500 for OEM applications.

#### **DOCUMENT STRUCTURE**

- Section 1 describes the principles of operation of the drive mechanics and electronics.

- Section 2 contains schematics of the Q500 circuits.

- Section 3 describes errors and media defects, self-diagnostics, track format, and other applications.

- Section 4 summarizes maintenance procedures.

Section 5 includes an exploded parts diagram of the major subassemblies and a complete parts list for the Drive Control PCB.

#### ASSOCIATED DOCUMENTS

Additional information on the Q500 drive, including general specifications and installation procedures, is contained in the Q500 Product Description OEM Manual.

# SECTION 1 PRINCIPLES OF OPERATION

# 1.1 MODEL Q500 BLOCK DIAGRAM

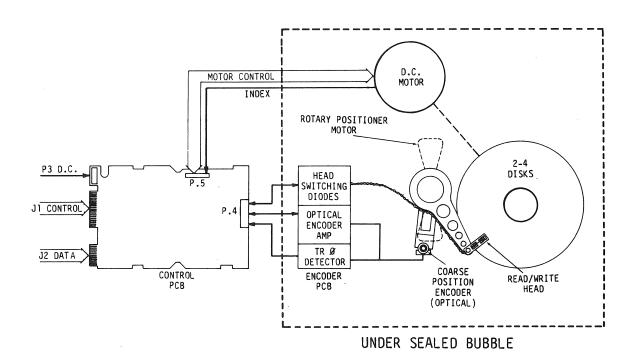

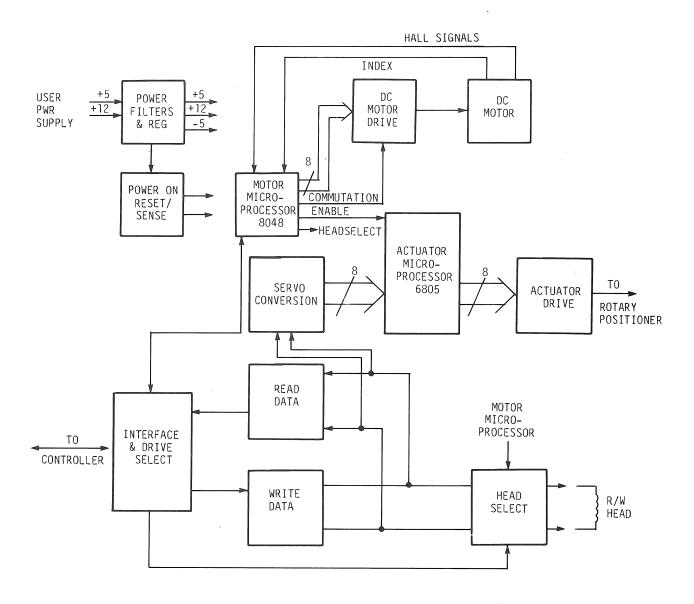

Figure 1-1 shows a block diagram of the Model Q500 Disk Drive. The spindle is driven from a dc motor mounted on the spindle shaft. The dc motor is powered by the +12V supplied to the drive via the P3 connector. The motor spindle rotates the disk at 3529 rpm. The read/write head stack assembly is mounted directly on the rotor of the rotary positioner assembly (proprietary to Quantum). The rotary positioner is driven by power drivers controlled by microprocessor-based circuitry on the control printed circuit board assembly (PCBA). Head stack track and position feedback signals are provided by an optical encoder and glass scale assembly via the encoder PCB. On-track thermal compensation is obtained from servo data written in a 290  $\mu$ s wedge on Physical Disk Surface 3. Optical position feedback and a servo wedge (which gives a hard track center) allow all the disk surfaces to be used for data storage and yet remain soft-sectored. Read/write signals are obtained from or written to the disk via the head switching matrix on the encoder PCB and the heads mounted on the head stack. The drive control PCB contains the electronics for servo position decoding, the head stack positioner drive, the microprocessor that controls these functions, and the read/write amplification and drive.

FIGURE 1-1 Model Q500 Block Diagram

## 1.2 MODEL Q500 DRIVE MECHANISM

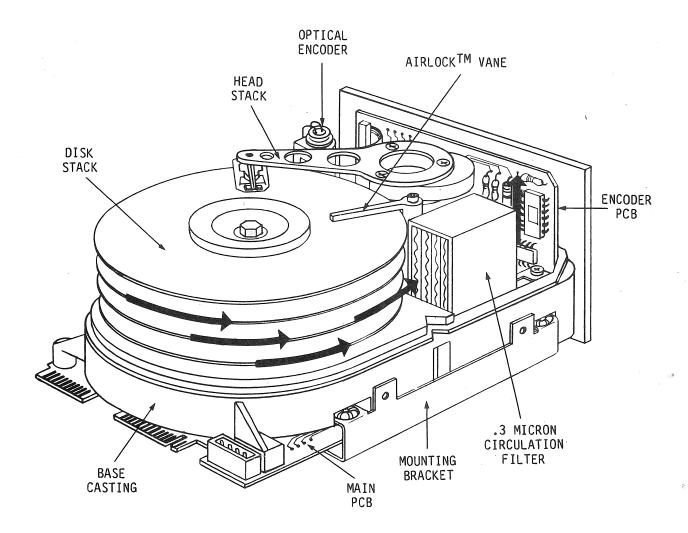

The drive's mechanical subassemblies are sealed under a metal bubble. None of these subassemblies is adjustable and none can be repaired in the field. Refer to Figure 1-2 for an illustration of the mechanical components of the drive.

FIGURE 1-2 Model Q500 Mechanical Layout

## 1.2.1 OPTICAL ENCODER

The optical encoder is the position-sensing device that provides feedback for the closed-loop system that controls head stack positioning. The encoder assembly is clamped to a post in the base of the drive. The encoder consists of a housing, an infrared LED, an optical reticle, and a photo diode matrix.

The infrared LED is mounted in the housing above the reticle. The reticle, which sits above the photo diodes, acts as a light mask to control the amount of light reaching the photo diodes. The reticle is matched to an optical scale mounted on the head stack. As the head stack moves, light reaching the photo diodes varies according to the match between the glass scale and the reticle; the light intensity is decoded into position information. The clearance and angular position of the reticle relative to the scale are adjusted during manufacture.

#### 1.2.2 ROTARY POSITIONER ASSEMBLY

The positioner used in the Q500 is a rotary torque actuator (a design proprietary to Quantum). The rotor of the positioner consists of two flat, triangular coils. These coils are molded so that they are perpendicular to the spindle shaft. This assembly is then mounted to the base so that the coils are suspended in a permanent magnetic field. The field is created by two magnetic segments — one mounted above the coils and one below. The segments are polarized so that current passing through the coils causes the positioner to rotate. Variations in current cause the positioner to rotate in either direction or to stop.

#### 1.2.3 HEAD STACK ASSEMBLY

The head stack assembly is mounted directly on the rotor and consists of the heads, head arms and their counter balances, and the optical scale. The counter balances are castings whose shape and weight ensure that the center of the mass of the entire stack is at the center of the mounting hub. The optical scale is bonded to the second-to-lowest counter balance, the optical scale provides position feedback via the optical encoder (see section 1.2.1). The heads are Winchester slider-types with a .0011 inch track width. They are mounted to spring steel flexures staked to the head arm. The head conductors are flex cables routed in plastic guides and attached with an adhesive. All head stack assemblies have an upper and lower head arm assembly and may have one to three dual head arm assemblies A spring is attached from the head stack assembly to the casting and is used to pull the heads into the landing zone when no power is applied to the actuator.

#### 1.2.4 DISK STACK ASSEMBLY

The disk stack assembly is secured to the dc spindle motor which is bolted to the base casting. The disk stack consists of disks, disk spacers, a disk clamp, and a grounding system for the spindle. Depending on the capacity of the drive, two to four disks and spacers are placed on the disk mounting hub and are clamped in place. The disks are made of an aluminum alloy with a magnetic oxide coating, which is polished and lubricated. The lubrication prevents head and media wear when the heads are in contact with the disk surface. Such contact only occurs outside the data area and when the disks are not rotating. The grounding system for the spindle consists of a steel button bonded to the bottom of the dc motor and a carbon button bonded to a spring contact on the control PCB.

#### 1.2.5 BASE CASTING ASSEMBLY

The base casting is a single piece of cast aluminum alloy. The drives subassemblies are mounted on this base. It has two machined holes for mounting the motor/spindle assembly and the positioner assembly. The outside top edge is flat to ensure an airtight seal with the metal bubble cover. The optical encoder, encoder PCB, and the upper magnet plate for the rotary positioner assembly are mounted inside the bubble area. Mounting holes are also provided, outside the bubble area, for the control PCB and faceplate. A grounding lug allows connection between the chassis ground and logic/power ground if desired. Shock mount brackets are provided for isolation from shock and vibration.

#### 1.2.6 DC DRIVE MOTOR

The Q500 is equipped with a dc spindle drive motor. The motor is controlled by a single-chip microprocessor. The dc motor assembly is bolted to the base casting and consists of a dc motor, a spindle-bearing assembly, a disk-mounting hub, and a ferro-fluid magnetic seal. This seal prevents outside air from entering the drive through the bearing bore or along the bearing shaft. Mounted in the dc motor are three Hall effect devices and an optical transducer which provide motor commutation, servo timing, and position feedback to the microprocessor. An index signal is generated from an LED/phototransistor pair; output is generated as a TTL lever from the motor. The LED shines light on the rim of the motor rotor; this light is reflected and the phototransistor detects it as INDEX when the unpainted portion of the rotor rim passes across the detector pair.

#### **1.2.7 EMI BAND**

A Winchester drive is sensitive to electromagnetic interference (EMI) due to the low signal level at the read/write heads. Therefore, it is necessary to shield the heads from EMI. On the Q500, most of the shielding is provided by the base casting and the cast cover. However, at the intersection of these two castings, a gap caused by the sealing gasket requires shielding. This is provided by a band (wire mesh attached to a rubber strip) placed over the gap and clamped in place with a stainless steel strap.

#### 1.2.8 AIR FILTRATION

Because the Model Q500 is a Winchester-type drive, the heads fly very close to the media surface. The nominal flying height is 18 microinches, or roughly 1600 times smaller than the diameter of the period at the end of this sentence.

It is absolutely essential that the air circulating within the drive be kept clean and free of particles. The drive is assembled in a Class 100 purified air environment and then is sealed in a metal bubble. During the life of the drive, the rotating disks act as an air pump to force the air through two internal filters. Figure 1-2 shows the airflow in the enclosed area of the drive. The lowest pressure area within the drive is located at the top in the center of the spindle. A 0.3 micron breather filter is bonded in this area of the bubble. This filter allows outside air into the bubble enclosure to equalize internal and external pressures. The highest pressure area within the drive is located at the outer edges of the disks. Bonded to the AIRLOCK base at this location is another 0.3 micron filter called the circulation filter. Air is constantly pumped into the side of the filter nearest the disks and then filtered and expelled from the side of the filter away from the disks. This area of the drive is at a lower pressure than at the edge of the disks so that air will circulate through the filter. This ensures a continuous flow of filtered air as soon as the disks start to rotate. Because stringent cleanliness is required, the bubble and seals should not be tampered with.

#### 1.2.9 AUTOMATIC ACTUATOR LOCK

A dedicated landing zone is used in the Q500 to ensure data integrity and prevent damage during shipment. AIRLOCK is an entirely mechanical means of locking the head stack in the landing zone; it is proprietary to Quantum. The AIRLOCK consists of an airvane mounted close to the edge of the disk stack, with an arm that intersects the actuator to hold the head stack in the landing zone when the disk is not rotating. As dc power is applied to the motor and the disk stack starts rotating, an airflow is generated around the disk. As airflow increases with disk rotation, the airvane and its arm will rotate, allowing the head stack to move freely out of the landing zone.

#### **NOTE**

The air-actuated lock (AIRLOCK) takes an average of 22 seconds and a maximum of 27 seconds to lock the actuator after dc power is removed.

## 1.3 DRIVE ELECTRONICS

#### 1.3.1 GENERAL FEATURES

This section briefly describes the functions performed by the Model Q500 electronics. The drive electronics contain the following circuitry:

#### **Interface Buffers**

The interface buffers are drivers and receivers that buffer the control and data signals between the drive and the drive controller. The function of the various interface signals is described in Sections 1.3.2 and 1.3.3.

#### **DC Power Circuits**

The dc power circuitry provides power decoupling and regulation as well as the power-up reset signal.

#### Read/Write Circuits

The read/write circuitry provides the write current to record data and the circuits to detect recorded data.

#### **Encoder PCBA**

The encoder printed circuit board assembly contains the head switching matrix and the circuits that generate track position signals from the signals provided by the scale and optical encoder.

#### **Servo Position Detection**

The servo position detection circuitry uses the signals from the factory-recorded servo to fine position the heads.

#### **Actuator Drive Circuits**

The actuator drive circuits provide the power to drive the actuator to position the head stack assembly.

#### **Actuator Microprocessor**

The actuator microprocessor is a single-chip processor which controls the drive during its various modes of operation and uses the output of the encoder PCBA and servo position-detection circuitry to generate track position signals used to position the actuator.

#### **Motor Microprocessor**

The motor microprocessor is a single-chip processor which controls start-up and speed of the dc motor. It also provides index timing for the interface and performs write fault detection.

#### **Motor Drive Circuit**

The motor drive circuit provides the power to drive the spindle motor.

#### 1.3.2 DATA INTERFACE

#### **General Description**

There are three signals on the data interface cable. None of these signals is multiplexed. One signal, DRIVE SELECTED, is a TTL open collector output. Two of the signals are differential: MFM WRITE DATA (input) and MFM READ DATA (output). The differential signals have the electrical characteristics described below.

Driver output current is 50 mA maximum on the driven line and 50 mA on the nondriven line. The output range is 0.5 to +3.5 Vdc. The receiver input voltage is 0.8 V to +2.0 Vdc on either line. The circuit will detect a differential voltage of 30 mV. Table 1-1 shows the pin designations of the data signals.

**TABLE 1-1 Data Cable Pin Designations**

| GROUND RETURN | SIGNAL PIN | SIGNAL NAME             |

|---------------|------------|-------------------------|

| 2             | 1          | -DRIVE SELECTED         |

| 4             | 3          | NA                      |

| 6             | 5          | NA                      |

|               | 7          | RESERVED (To J1 Pin 16) |

| 8             |            |                         |

|               | 9          | NA                      |

|               | 10         | NA                      |

| 11            |            |                         |

| 12            |            |                         |

|               | 13         | +MFM WRITE DATA         |

|               | 14         | -MFM WRITE DATA         |

| 16            |            |                         |

|               | 17         | +MFM WRITE DATA         |

|               | 18         | -MFM WRITE DATA         |

| 19            |            |                         |

| 20            |            |                         |

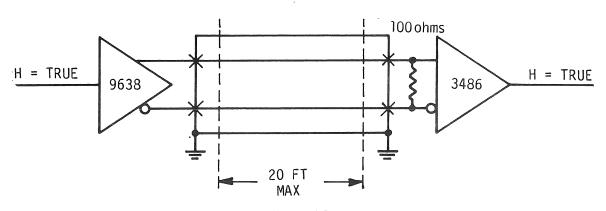

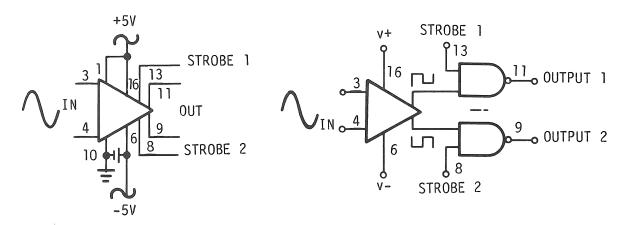

#### Driver Receiver

Figure 1-3 shows the recommended differential data signal driver/receiver combination. The maximum recommended cable length is 20 feet (6 m).

FIGURE 1-3

Data Signal Driver/Receiver

#### **Data Signal Descriptions**

The function of each of the three data signals is described below.

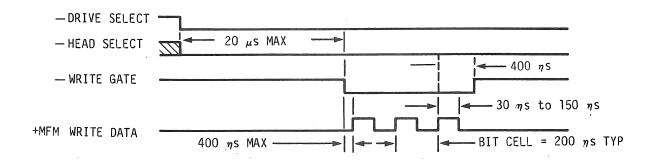

• MFM WRITE DATA — Provided the drive is selected and there is LO level on the WRITE GATE control line, the transition of the +MFM WRITE DATA line to a line more positive than the -MFM WRITE DATA line will cause a flux reversal to be written on the disk. Figure 1-4 shows the WRITE DATA timing.

FIGURE 1-4

MFM Write Data Timing

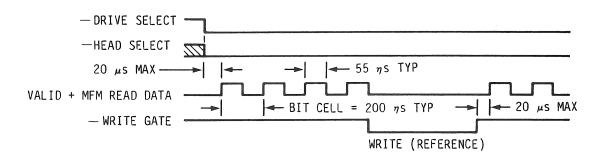

• MFM READ DATA — Provided the drive is selected and there is a HI level on the WRITE GATE control line, the transition of the +MFM READ DATA line to a line more positive than the -MFM READ DATA line indicates that a flux reversal was detected on the track. Figure 1-5 shows the READ DATA timing.

FIGURE 1-5

MFM Read Data Timing

• DRIVE SELECTED — This open collector line will go to a LO level when this drive is selected by the appropriate drive select line.

# 1.3.3 CONTROL SIGNAL DESCRIPTIONS

Unless otherwise stated, all control signals are enabled with DRIVE SELECT. The function of each of the fifteen control signals is described below. Table 1-2 summarizes the pin designations for the control signals.

TABLE 1-2 Control Cable Pin Designations

| GROUND RETURN | SIGNAL PIN | SIGNAL NAME                                                             |

|---------------|------------|-------------------------------------------------------------------------|

| 1             | 2          | -N/A (Reduced write current<br>done automatically by<br>microprocessor) |

| 3             | 4          | -Head Select 2 <sup>2</sup>                                             |

| 5             | 6          | -Write Gate                                                             |

| 7             | 8          | -Seek Complete                                                          |

| 9             | 10         | -Track 0                                                                |

| 11            | 12         | -Write Fault                                                            |

| 13            | 14         | -Head Select 2º                                                         |

| 15            | 16         | -Reserved (to J2 PIN 7)                                                 |

| 17            | 18         | -Head Select 2 <sup>1</sup>                                             |

| 19            | 20         | -Index                                                                  |

| 21            | 22         | -Ready                                                                  |

| 23            | 24         | -Step                                                                   |

| 25            | 26         | -Drive Select 1                                                         |

| 27            | 28         | -Drive Select 2                                                         |

| 29            | 30         | -Drive Select 3                                                         |

| 31            | 32         | -Drive Select 4                                                         |

| 33            | 34         | -Direction In                                                           |

#### **Input Signals**

- DRIVE SELECT 1,2,3, or 4 A LO level on this line logically connects the drive to the control lines. Only one drive select line may be active at a time. The active DRIVE SELECT line selects the drive which has the matching drive select jumper installed.

- HEAD SELECT 2<sup>0</sup>, 2<sup>1</sup>, 2<sup>2</sup> these three lines provide a binary code to select one of the heads. 2<sup>0</sup> is the least significant bit. The heads are numbered 0 through 7. When all lines are LO, head 7 is selected. Conversely, if all lines are HI, head 0 is selected.

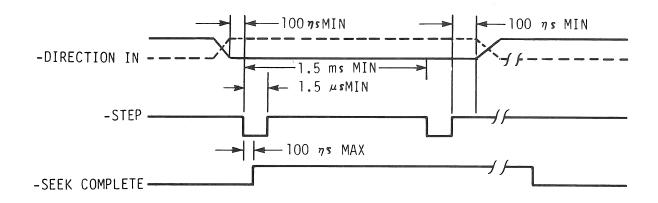

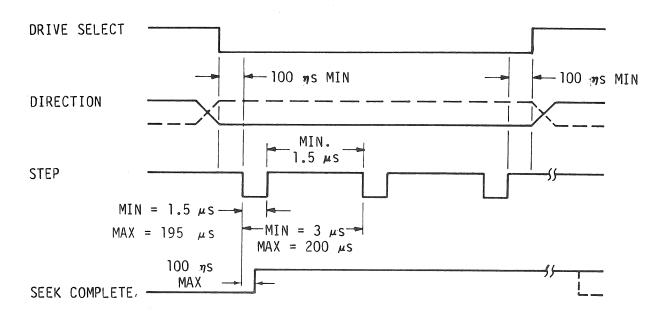

- DIRECTION IN a LO level on this line defines the R/W head motion as in, or toward the center of the disk (away from Track 000). A HI level on this line defines the R/W head motion as out, or toward the edge of the disk (toward Track 000). See Figures 1-6 and 1-7 for timing direction.

FIGURE 1-6 Single Step Mode Timing

FIGURE 1-7

Buffered Step Mode Timing

- STEP a LO pulse of at least 1.5 μs duration on this line causes the R/W head to move in the direction defined by the DIRECTION IN line. If step pulses occur at an internal equal to or greater than 1.5 ms between pulses, the heads will move at approximately the rate of incoming steps (single step mode). If the incoming step pulse rate is equal to or less than 200 μs between pulses, the pulses are buffered into a counter and motion occurs after the last step pulse is received (buffered mode). See Figures 1-6 and 1-7 for Step Timing.

- WRITE GATE a LO level enables the write circuitry which allows data to be written on the disk.

#### **Output Signals**

- READY a LO level on this line indicates the disks are up to speed and the interface signals are valid. When READY and SEEK COMPLETE are true, the drive is ready to read, write, or seek. (If a seek error occurs, READY will go false for approximately 60 µs. Then the drive will recalibrate itself and return the heads to TK0, which can take up to 9 seconds.)

- WRITE FAULT a LO level on this line indicates any of the following conditions have been sensed, and writing and reading have been inhibited:

- 1. DRIVE SELECT is selected, WRITE GATE is true, and no write current is detected.

- 2. Write current is detected and either WRITE GATE or DRIVE SELECT is unselected.

- 3. DC voltages are too low, thresholds are set below the normal ranges of operation.

- 4. Writing is attempted on heads 7 and 8 (in a 30-Mb drive) or heads 5, 6, 7, and 8 (in a 20-Mb drive).

WRITE FAULT can be cleared by deselecting and reselecting the drive, or by cycling the power off, then on.

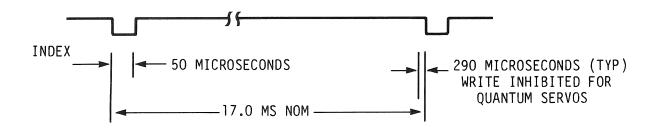

• INDEX — a LO pulse of approximately 50 μs once per revolution (or every 17 ms) indicates the beginning of a track. The leading edge of this pulse should be used for all timing requirements. See Figure 1-8 for INDEX timing.

# FIGURE 1-8 Index Timing

- SEEK COMPLETE a LO level on this line indicates the R/W heads have settled on a cylinder and a read, write, or another seek may take place. Writing is inhibited while this signal is false (HI). (Seek complete may go false during recovery from a seek error.)

- TRACK ∅ a LO on this line indicates that the R/W heads are positioned at cylinder 000 (the outermost cylinder).

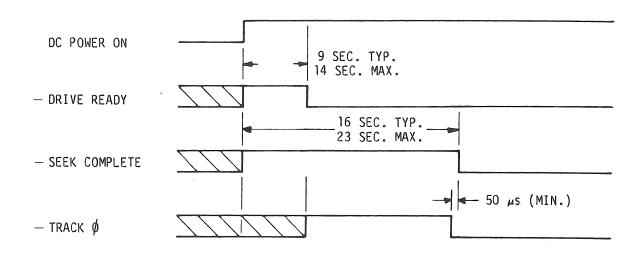

Figure 1-9 shows the general timing relationships between some of the control signals found in the Model Q500 during the POWER ON cycle of the drive.

FIGURE 1-9

General Control Timing Requirements

# 1.3.4 POWER REQUIREMENTS

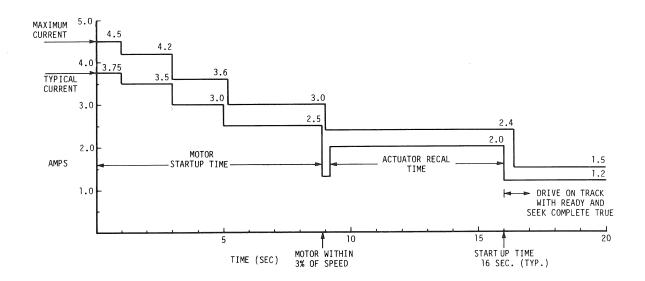

The voltage and current requirements of the dc power supplied to the drive are listed in Table 1-3. No power sequencing, either off or on, is required by the Q500. Figure 1-10 shows the start-up current profiles of the drive.

TABLE 1-3

DC Power Requirements

| VOLTAGE<br>NOMINAL       | 12V                    | 5V        |

|--------------------------|------------------------|-----------|

| Current                  |                        |           |

| Typical                  | 2.0A (Seeking)         | .7A       |

| Maximum                  | 2.4A (Seeking)         | 1.0A      |

| Maximum                  | 4.5A (Motor Start 1 s) |           |

| Regulation               | <u>+</u> 1.2V          | ±.25V     |

| Ripple and Noise Maximum | 100 mV P-P             | 50 mV P-P |

|                          |                        |           |

FIGURE 1-10

Drive Start-Up Current Profile (12V line)

#### 1.3.5 INTERFACE AND DRIVE SELECT LOGIC

This logic performs three functions in the Q500:

- 1. Provides cable drivers and receivers for the interface signal

- 2. Allows for gating these signals with the DRIVE SELECT line

- 3. Provides for interface cable terminator on the last drive on the cable

Input signals for HEAD SELECT, DIRECTION IN, STEP, and WRITE GATE control signals are received by a 74LS244 at U15 and may be terminated by installing a 220/330 ohm resistor pack at RN3.

The DRIVE SELECT jumper block and the DRIVE SELECT terminator R46 and R47 are shown in coordinates 7B and 6B in Figure 2-2. Placing a jumper across point A causes continuous selection and is normally used for test purposes. Otherwise, when a LO signal on a DRIVE SELECT line matches with a jumper, reception is enabled of input signals STEP, DIRECTION IN, and HEAD SELECT signals 2° and 2¹. Additionally, an active DRIVE SELECT line causes the following to occur:

- 1. Front plate LED lights.

- 2. Outputs -SEEK COMPLETE, -TRACKO, -WRITE FAULT, -READY and -INDEX are enabled at interface connector J1.

- 3. -DRIVE SELECTED output at data cable (J2-1) goes active via U4-11.

The motor microprocessor also uses the state of DRIVE SELECT to determine Write Fault conditions.

# 1.3.6 ENCODER BOARD

Figure 1-11 is a functional block diagram of the encoder PCB. The board contains the components listed below:

- the diodes used for head switching

- a through-bubble connector (which connects to the head signals, actuator drive signals, and actuator position signals)

- the op amps used to condition the encoder photocell outputs

- the AGC amplifier used to control the infrared LED drive current

FIGURE 1-11

Encoder PCB Block Diagram

## 1.3.7 DRIVE CONTROL BOARD

Figure 1-12 is a functional block diagram of the drive control board. The board is mounted on the top of the drive. One end of the drive control board connects to the encoder PCB. The other end of the board has edge contact fingers for control signal and data interface connectors. The drive control board also has connectors for dc power, the dc spindle motor, and the faceplate LED.

FIGURE 1-12 Drive Control PCB Block Diagram

Applying dc power to the drive starts the dc motor spinning after voltage levels have exceeded the minimum limit determined by the POR circuit. Once the voltage has exceeded this limit, the heads lift off the disk surface and fly above the landing zone. When the motor microprocessor (via the INDEX signal) detects that the dc motor speed is within 3% of nominal speed (3423 rpm), the motor microprocessor generates an UP TO SPEED signal to the actuator microprocessor to recalibrate the actuator to Track 0. When the actuator is recalibrated, the drive sets READY, Track 0 and SEEK COMPLETE signals at the control interface.

When -DRIVE SELECT "X" is driven true and matches the drive select jumper, the drive select logic enables the interface logic to gate control signals to and from the drive. The drive will read or write data on the selected head at the present track, depending on the state of the WRITE GATE line.

The track location of the heads may be changed by selecting the appropriate direction via the DIRECTION IN line and issuing step pulses. The step pulse can be sent in one of two modes: normal (single step) mode in which step pulses are sent less frequently than every 1.5 ms and buffered mode (in which step pulses are sent more frequently than every 200  $\mu$ s).

#### 1.3.8 AGC CIRCUIT

The AGC circuit is used to compensate for the effects of temperature and aging on the signals generated in the encoder assembly.

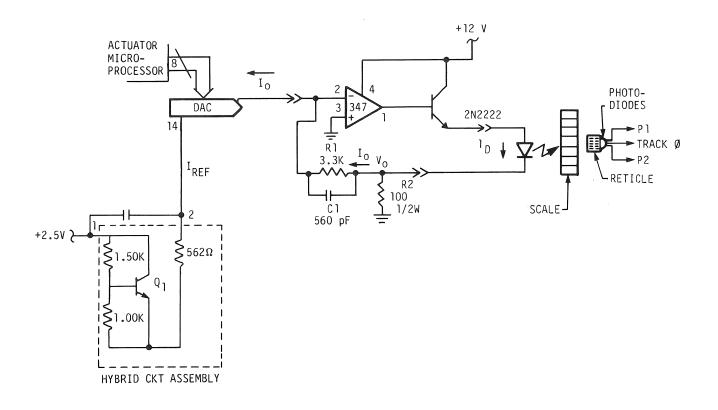

Figure 1-13 shows the AGC circuit. Section 1.2.1 describes the mechanical operation of the optical scale, reticle, and photo diode. Section 1.3.11 presents a description of how current is supplied to the LED by the actuator microprocessor.

A 347 Op amp drives the base of the 2N2222, which provides current to the LED.

The LED current, ID is given by the equation:

$$I_{D} = I_{0} + \frac{V_{0}}{100Q}$$

Since the inverting input is approximately ground,

$$V_0 = I_0 (3.3 \text{ k}\Omega)$$

Therefore:

$$I_D = I_0 + \frac{I_0 (3.3k\Omega)}{100\Omega} = 34(I_0)$$

The current through the LED is 34 times the DAC current I<sub>0</sub> which is:

$$I_0 = I_{REF} \left( \frac{A1}{2} + \cdots + \frac{A8}{256} \right)$$

where I<sub>REF</sub> is provided by a hybrid circuit assembly that compensates for variations of LED intensity due to temperature change.

FIGURE 1-13 AGC Circuit

#### 1.3.9 P1 AND P2 GENERATION

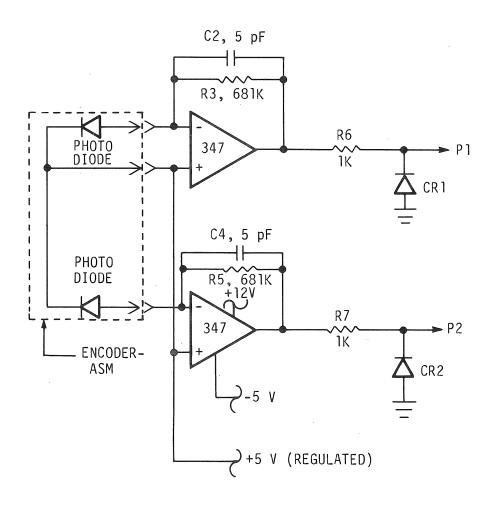

Refer to Figure 1-14 for a schematic illustration of P1 and P2 generation.

P1 and P2 are derived from two photo diodes located on the encoder PCB. The resulting signals determine coarse track position and track crossings. Section 1.2.1 describes the mechanical operation of the optical scale, reticle, and photo diode.

As the optical scale moves through the encoder gap, pseudo-sinusoidal signals are generated at P1 and P2 with a 90° phase difference created from the offset windows the reticle provides. The infrared light which passes through the scale/reticle filter causes a current to flow in each photo diode. This current varies since the amount of light detected by the photo diode varies with the movement of the scale. Current flow through the photo diode causes current flow in R3 and R5, which causes the voltage to swing proportionately at P1 and P2.

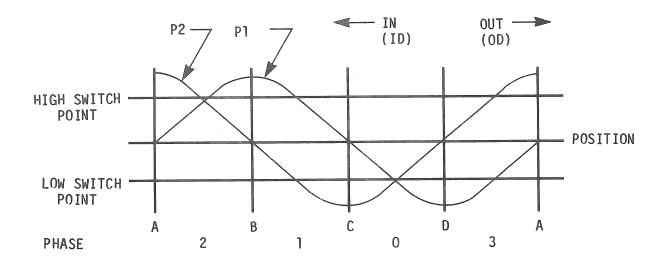

Sample P1 and P2 signals are shown in Figure 1-15. Four zero crossings (one corresponding to each peak of the signal) occur during a period on P1 and P2, marking the track center value. The track crossings are defined by the high and low switch points which are calculated during recalibration.

FIGURE 1-14 P1 and P2 Generation

FIGURE 1-15

P1 and P2 Signals vs. Position

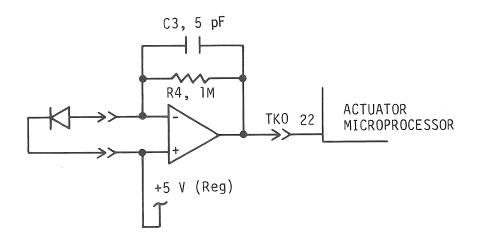

# 1.3.10 TRACK 0

A separate photocell determines Track 0 in the encoder assembly. An opaque rectangle on the scale restricts LED light from the photo diode when the signal is near Track 0. The phases of P1 and P2 signals determine the actual "rough" Track 0 location after the Track 0 signal was switched at some point within the "first" period of the P1 and P2 signals. An op amp is used to detect the photo diode current and drive the input of the actuator microprocessor (see Figure 1-16).

FIGURE 1-16

Track 0 Detector

When light enters the photo diode, current flows causing the output of the op amp to be low. When the light beam is broken by the Track 0 area on the scale, current no longer flows and the output of the op amp is 5V, signaling Track 0.

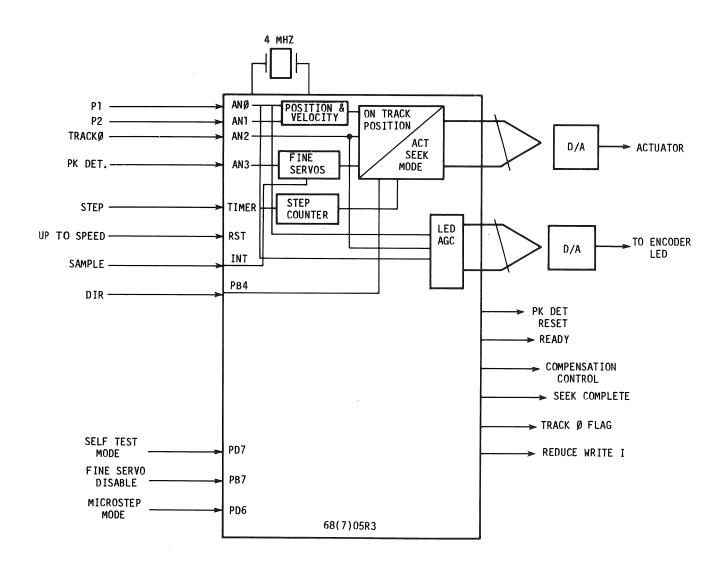

#### 1.3.11 ACTUATOR POSITIONING CIRCUITS

#### **Actuator Microprocessor**

The actuator microprocessor is an 8-bit microcomputer with 112 bytes of RAM, time/counter, and I/O functions. It has 32 I/O lines, four of which are analog inputs (0-5V). The RAM includes registers for the I/O ports and timers. It has 3.8 kbytes of (E)PROM for program storage. Figure 1-17 illustrates the organization of the actuator microprocessor.

FIGURE 1-17 Actuator Microprocessor Block Diagram

#### Recalibration

Upon power-up, the microprocessor initializes certain I/O pins, RAM locations, and INTERRUPT lines. It then determines the phase orientation of the position signals, P1 and P2. The initial P1 and P2 position signals are then calibrated by adjusting their respective LED current values. The actuator then is stepped out to Track 0, which is located by the level of the Track 0 photocell and the relationship of the position signals, P1 and P2. A handshake is established with the 8048 dc motor microprocessor for index time. The zone timers are initialized and the zone table offsets are initialized to the present Track 0 values. At this point, positioning control of the actuator is passed to the main loop, SEEK COMPLETE is set, and the drive may seek at the command of the controller.

#### **AGC Function**

The actuator microprocessor performs the AGC function at index time and at the end of a seek. The LED current values for the P1 and P2 position signals are increased or decreased based on the value (level) of the Track 0 signal. This Track 0 reference level is originally stored in RAM during recalibration at approximately Track 256. The AGC function is not used when the position signals are within four tracks of Track 0, since the Track 0 signal begins the transition toward +5V beyond this point.

#### On Track Servoing (coarse)

The drive uses servoing to maintain the actuator in an on-track (stationary) position. The microprocessor controls head position by comparing the difference between the position signal voltage level (P1 or P2) and a reference value. The difference between these values is the error, and a correction value will be output from the microprocessor to the actuator DAC. This coarse servo loop occurs approximately every 150  $\mu$ s or about 100 times per revolution.

#### **Fine Servoing**

The microprocessor applies fine servo correction to the reference value to compensate for changes in head positioning accuracy due to thermal conditions.

Once per revolution, 290 µs prior to USER INDEX, the drive peak detects and samples the factory-written servo bursts. The servo bursts consist of an A and B burst placed between the data tracks on surface 3. When reading the servo bursts (wedge time), the drive switches from the selected head to head 3. See the section on WEDGE and INDEX signals on page 1-69. After SEEK COMPLETE, the microprocessor limits fine servo corrections to the reference value to one DAC step per revolution. Prior to SEEK COMPLETE, the microprocessor sends the full value required for correction.

#### Thermal Zones

For long term temperature compensation, the 512 cylinders are divided into eight zones of 64 cylinders each. During driver operation the amplitude of the thermal offtrack correction factor (described above) is stored in a zone table in the actuator control microprocessor RAM. The necessity for eight thermal zones was derived from the inner track to the outer track differential thermal offtrack measurements. The quadrature nature of the optical encoder used in the Q500 dictates that the offtrack error will repeat every four tracks. Therefore, within each of the eight zones it is necessary to save four offtrack values, one for each of the four phases of the quadrature encoder (as described above). Thus, the zone table consists of 32 RAM bytes. The requirement for the zone table is to predict the thermal offset based on the lst time the actuator was positioned at that location. When a seek is initiated from one zone to another the current track thermal offset amplitude is stored in the zone table for future use. The destination track thermal offset correction factor is retrieved from the zone table and the head will settle to this predicted offset before seek complete is TRUE. This eliminates the need to wait for the once around fine servo information at the end of each seek, which would otherwise add an average of half a revolution to the seek time.

Upon power up the Q500 will automatically position the actuator at the outermost track, Track 0. Before seek complete is TRUE the fine servo information is read and the actuator position is updated accordingly. This offset amplitude at Track 0 is used to initialize all thermal zone locations. However, it is not accurate enough across the entire surface of the data area and is considered a rough initialization. Upon the first seek to a yet unvisited zone, seek complete will not be TRUE until the fine servo information had been read and the actuator position updated accordingly.

#### Ramped Mode Seeking

The ramped mode is used for single step seeks and buffered seeks of 17 or fewer tracks. In ramped mode, the actuator arm accelerates linearly until it is half the distance to its destination track.

Then the actuator arm decelerates linearly until it settles on the destination track. The actuator microprocessor controls positioning during a ramped mode seek by looking at the positive and negative slopes of the P1 and P2 signals (analog inputs).

When the STEP counter is loaded with fewer than 18 STEP pulses, the reference value is changed up or down depending on the desired direction of movement. On the first slope (of P1 or P2), the reference value is changed in increments of 8 DAC steps. When the limit of the first slope (HI or LO) is reached, the microprocessor looks at the next slope (P1 or P2) and begins to change the reference value in steps of 16. See Section 1.3.9 for an explanation of P1 and P2 signals. Each slope represents a track and, with each track crossed, the change in the reference value increases until the actuator reaches the halfway point. The microprocessor uses the reverse process to decelerate the actuator until it finally reaches the destination track.

#### Slew Mode Seeking

The slew mode of seeking is used for buffered seeks of 18 or more tracks. During the slew mode, the actuator is accelerated to a terminal velocity. This is controlled for the first half of the seek. During the second half of the seek, the actuator is decelerated to a velocity determined by the number of TRACKS TO GO.

If the seek length is an even number of tracks, the current position signal being servoed on will be the position signal used at the destination track. This will be the same phase or plus two phases.

If the seek length is an odd number of tracks, position signals switch and the first crossing of a switch point will decrease the number of TRACKS TO GO. This results in an even number of TRACKS TO GO. The position signal that was switched to becomes the destination position signal. Center crossings of this position signal are counted, decreasing the TRACKS TO GO by twos as with an even track seek.

Upon entering a slew mode seek, the terminal velocity is determined from a table. The number of analog-to-digital conversions between center crossings of the position signal provides the velocity feedback. To maintain this velocity, the full acceleration value is output to the actuator (00H or FFH, depending on direction) until the velocity is greater than desired. At that time, a coast value is issued to the actuator (which also depends on direction). Terminal velocity is maintained for half of the way to the destination track. At that time the full deceleration value is issued. While monitoring the time between center crossings (velocity) and the number of TRACKS TO GO, the seek profile table is followed down to the destination track, slowing down the actuator.

Prior to the beginning of any seek, the internal timer counter has been "primed" with the counter set at "1" and the timer interrupt enabled. With the receipt of the first step pulse the counter is decremented to zero, generating an interrupt.

Upon receipt of the first STEP pulse, the microprocessor saves the current prediction and other values. This is a buffered seek mode. Preparing to seek, the microprocessor rechecks the counter for any more STEP pulses. If more STEP pulses have been received, it will continue through a loop of approximately  $200 \,\mu s$ , rechecking the last and current counter values until all STEP pulses are received. If, after the first STEP pulse, no additional steps were seen, the microprocessor would proceed in the single step mode.

The single step mode means STEP pulses are received by the drive with more than 1.5  $\mu$ s between STEP pulses. Buffered mode seeks are defined as 3 to 200  $\mu$ s between STEP pulses. However, STEP pulses issued between 200  $\mu$ s and 1.5 ms will be accepted.

When entering the seek mode, the microprocessor also tests the condition of the microstep line. Microstep is used only for servo writing.

Buffered seeks of 17 or fewer tracks are handled as single steps in a ramped mode. An 18-track seek will take less time than a 17-track seek, therefore, because buffered seeks greater than 17 tracks are in the slew mode.

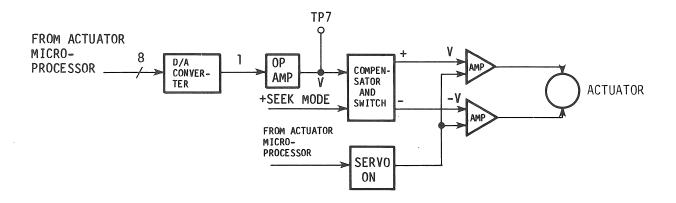

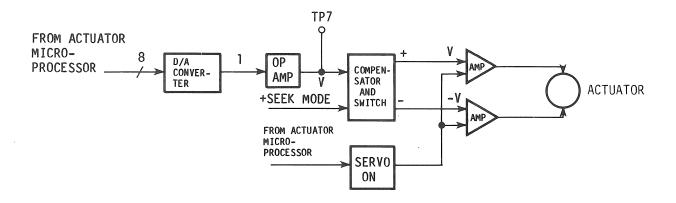

#### **Actuator Drive Circuits**

Figure 1-18 shows a block diagram of the actuator drive circuits. The microprocessor enables power to the amplifiers at power-up via the enable driver. Additionally, the microprocessor generates a series of 8 digital line-signals that correspond to specific currents to the actuator, as shown in Table 1-4.

TABLE 1-4 D/A Actuator Signals

| DIGITAL  | HEXIDECIMAL | CURRENT              |

|----------|-------------|----------------------|

| 11111111 | (FF)        | Full Outward Current |

| 10000000 | (80)        | Zero Current (Coast) |

| 00000000 | (00)        | Full Inward Current  |

A digital-to-analog converter (DAC) transforms the eight digital lines to a current that an op amp converts to voltage (TP 7). The voltage goes into a lead-lag compensator to stabilize the loop. Finally, the compensator output passes through voltage to current amplifiers that send current to the actuator.

FIGURE 1-18

Actuator Drive Block Diagram

#### Actuator Current

The actuator microprocessor U7 sends an 8-bit word to the actuator DAC U8 to select the actuator current as one of 256 values. The range of values is 128 steps of positive current for outward movement of the actuator (towards Track 0), and 128 steps of negative current for inward movement of the actuator (towards Track 511).

The actuator microprocessor controls the actuator current in two modes: seeking and servoing. The first mode in which the actuator microprocessor controls the actuator current is the seeking mode. Seeking can be further divided into two modes: slew mode and ramped mode. During slew mode, the current to the actuator is one of three values depending on the direction and acceleration/deceleration of the actuator. See Table 1-4.

During ramped mode seeking, the actuator current is incremented or decremented in eight DAC step increments to control velocity.

The second mode in which the actuator microprocessor controls the actuator current is the servoing mode. During servoing, the output current to the actuator is determined by the following expression (all values are in hex).

$$DACOUT = (REF - POS) + NOPOWER$$

where DACOUT is the 8-bit word to the DAC, U8; REF is the desired position signal value; POS is the measured position signal value; and NOPOWER is the DAC value that would result in no movement of the actuator (close to zero current).

#### Actuator Drive Circuit

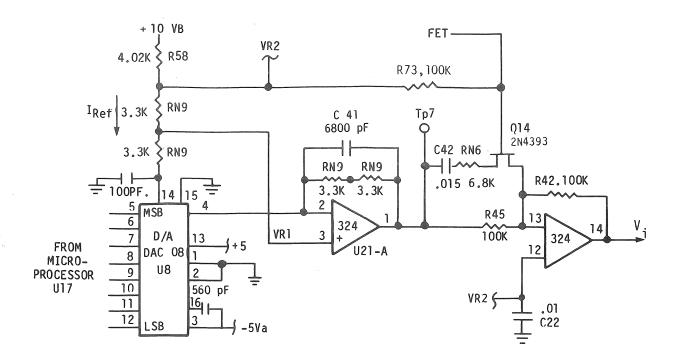

Figure 1-19 shows a schematic of the actuator drive circuit. R58 (4.02K) and the two resistors of RN9 (3.3K each) add up to 10.62K. This determines the full scale reference current Iref as well as reference voltages VR1 and VR2.

Iref =

$$\frac{+10VB}{4.02k + 6.6k} = \frac{+10VB}{10.62k} = .94 \text{ mA full scale}$$

Therefore, output current per step =  $\frac{.94 \text{ mA}}{256}$  = 3.67  $\mu$ A per DAC step.

The output of the DAC is converted to a voltage by U21-A, LM324. The input to pin 3, VR1, is determined by R58 and the two 3.3K resistors of RN9.

$$VR_1 = \left(\frac{3.3k}{6.6K + 4.02k}\right) 10_{VB} = \left(\frac{3.3k}{10.62k}\right) 10_{VB} = 3.1V$$

The voltage at TP7 is determined by the gain resistors of RN9 which add up to 6.6K. The output voltage is:

TP7 voltage =

$$6.6K$$

(I) +  $VR_1$

Therefore minimum output is:

$$VR1 + 6.6K(0) = 3.1 + 0 = 3.1V$$

Full scale output is:

$$VR1 + 6.6K (.94 \text{ mA}) = 3.1 + 6.2 = 9.3V$$

Output change per DAC step is 24.22 mV. Therefore, the range of the output voltage is 3.1V to 9.3V.

Capacitor C41, 6800PF in conjunction with the resistors in RN9 (6.6K) stabilize the output for high frequencies, as well as control the bandwidth of the driver stage.

U21-B is an inverting gain stage with compensation network formed by C42, .015  $\mu$ F, and RN6, 6.8K. The compensation is needed to stabilize the transfer function during position control. The FET device, Q14, is used to disable this network during slew mode seeking.

The reference voltage for U21-B, C and U23, U24 is used to determine the output range of these stages. This reference, VR2 is:

$$VR_2 = \frac{6.6k}{10.62k} 10_{VB} = 6.2V$$

U21-C is another inverting unity gain stage to provide complementary drive, along with U21-B to the output drivers U23 and U24.

#### Recalibration

Upon power-up, the microprocessor initializes certain I/O pins, RAM locations, and INTERRUPT lines. It then determines the phase orientation of the position signals, P1 and P2. The initial P1 and P2 position signals are then calibrated by adjusting their respective LED current values. The actuator then is stepped out to Track 0, which is located by the level of the Track 0 photocell and the relationship of the position signals, P1 and P2. A handshake is established with the 8048 dc motor microprocessor for index time. The zone timers are initialized and the zone table offsets are initialized to the present Track 0 values. At this point, positioning control of the actuator is passed to the main loop, SEEK COMPLETE is set, and the drive may seek at the command of the controller.

#### AGC Function

The actuator microprocessor performs the AGC function at index time and at the end of a seek. The LED current values for the P1 and P2 position signals are increased or decreased based on the value (level) of the Track 0 signal. This Track 0 reference level is originally stored in RAM during recalibration at approximately Track 256. The AGC function is not used when the position signals are within four tracks of Track 0, since the Track 0 signal begins the transition toward +5V beyond this point.

#### On Track Servoing (coarse)

The drive uses servoing to maintain the actuator in an on-track (stationary) position. The microprocessor controls head position by comparing the difference between the position signal voltage level (P1 or P2) and a reference value. The difference between these values is the error, and a correction value will be output from the microprocessor to the actuator DAC. This coarse servo loop occurs approximately every 150  $\mu$ s or about 100 times per revolution.

#### **Fine Servoing**

The microprocessor applies fine servo correction to the reference value to compensate for changes in head positioning accuracy due to thermal conditions.

Once per revolution, 290  $\mu$ s prior to USER INDEX, the drive peak detects and samples the factory-written servo bursts. The servo bursts consist of an A and B burst placed between the data tracks on surface 3. When reading the servo bursts (wedge time), the drive switches from the selected head to head 3. See the section on WEDGE and INDEX signals on page 1-69. After SEEK COMPLETE, the microprocessor limits fine servo corrections to the reference value to one DAC step per revolution. Prior to SEEK COMPLETE, the microprocessor sends the full value required for correction.

#### Thermal Zones

For long term temperature compensation, the 512 cylinders are divided into eight zones of 64 cylinders each. During driver operation the amplitude of the thermal offtrack correction factor (described above) is stored in a zone table in the actuator control microprocessor RAM. The necessity for eight thermal zones was derived from the inner track to the outer track differential thermal offtrack measurements. The quadrature nature of the optical encoder used in the Q500 dictates that the offtrack error will repeat every four tracks. Therefore, within each of the eight zones it is necessary to save four offtrack values, one for each of the four phases of the quadrature encoder (as described above). Thus, the zone table consists of 32 RAM bytes. The requirement for the zone table is to predict the thermal offset based on the 1st time the actuator was positioned at that location. When a seek is initiated from one zone to another the current track thermal offset amplitude is stored in the zone table for future use. The destination track thermal offset correction factor is retrieved from the zone table and the head will settle to this predicted offset before seek complete is TRUE. This eliminates the need to wait for the once around fine servo information at the end of each seek, which would otherwise add an average of half a revolution to the seek time.

Upon power up the Q500 will automatically position the actuator at the outermost track, Track 0. Before seek complete is TRUE the fine servo information is read and the actuator position is updated accordingly. This offset amplitude at Track 0 is used to initialize all thermal zone locations. However, it is not accurate enough across the entire surface of the data area and is considered a rough initialization. Upon the first seek to a yet unvisited zone, seek complete will not be TRUE until the fine servo information had been read and the actuator position updated accordingly.

#### Ramped Mode Seeking

The ramped mode is used for single step seeks and buffered seeks of 17 or fewer tracks. In ramped mode, the actuator arm accelerates linearly until it is half the distance to its destination track.

Then the actuator arm decelerates linearly until it settles on the destination track. The actuator microprocessor controls positioning during a ramped mode seek by looking at the positive and negative slopes of the P1 and P2 signals (analog inputs).

When the STEP counter is loaded with fewer than 18 STEP pulses, the reference value is changed up or down depending on the desired direction of movement. On the first slope (of P1 or P2), the reference value is changed in increments of 8 DAC steps. When the limit of the first slope (HI or LO) is reached, the microprocessor looks at the next slope (P1 or P2) and begins to change the reference value in steps of 16. See Section 1.3.9 for an explanation of P1 and P2 signals. Each slope represents a track and, with each track crossed, the change in the reference value increases until the actuator reaches the halfway point. The microprocessor uses the reverse process to decelerate the actuator until it finally reaches the destination track.

#### Slew Mode Seeking

The slew mode of seeking is used for buffered seeks of 18 or more tracks. During the slew mode, the actuator is accelerated to a terminal velocity. This is controlled for the first half of the seek. During the second half of the seek, the actuator is decelerated to a velocity determined by the number of TRACKS TO GO.

If the seek length is an even number of tracks, the current position signal being servoed on will be the position signal used at the destination track. This will be the same phase or plus two phases.

If the seek length is an odd number of tracks, position signals switch and the first crossing of a switch point will decrease the number of TRACKS TO GO. This results in an even number of TRACKS TO GO. The position signal that was switched to becomes the destination position signal. Center crossings of this position signal are counted, decreasing the TRACKS TO GO by twos as with an even track seek.

Upon entering a slew mode seek, the terminal velocity is determined from a table. The number of analog-to-digital conversions between center crossings of the position signal provides the velocity feedback. To maintain this velocity, the full acceleration value is output to the actuator (00H or FFH, depending on direction) until the velocity is greater than desired. At that time, a coast value is issued to the actuator (which also depends on direction). Terminal velocity is maintained for half of the way to the destination track. At that time the full deceleration value is issued. While monitoring the time between center crossings (velocity) and the number of TRACKS TO GO, the seek profile table is followed down to the destination track, slowing down the actuator.

Prior to the beginning of any seek, the internal timer counter has been "primed" with the counter set at "1" and the timer interrupt enabled. With the receipt of the first step pulse the counter is decremented to zero, generating an interrupt.

Upon receipt of the first STEP pulse, the microprocessor saves the current prediction and other values. This is a buffered seek mode. Preparing to seek, the microprocessor rechecks the counter for any more STEP pulses. If more STEP pulses have been received, it will continue through a loop of approximately  $200 \,\mu s$ , rechecking the last and current counter values until all STEP pulses are received. If, after the first STEP pulse, no additional steps were seen, the microprocessor would proceed in the single step mode.

The single step mode means STEP pulses are received by the drive with more than 1.5  $\mu$ s between STEP pulses. Buffered mode seeks are defined as 3 to 200  $\mu$ s between STEP pulses. However, STEP pulses issued between 200  $\mu$ s and 1.5 ms will be accepted.

When entering the seek mode, the microprocessor also tests the condition of the microstep line. Microstep is used only for servo writing.

Buffered seeks of 17 or fewer tracks are handled as single steps in a ramped mode. An 18-track seek will take less time than a 17-track seek, therefore, because buffered seeks greater than 17 tracks are in the slew mode.

#### **Actuator Drive Circuits**

Figure 1-18 shows a block diagram of the actuator drive circuits. The microprocessor enables power to the amplifiers at power-up via the enable driver. Additionally, the microprocessor generates a series of 8 digital line-signals that correspond to specific currents to the actuator, as shown in Table 1-4.

TABLE 1-4 D/A Actuator Signals

| DIGITAL  | HEXIDECIMAL | CURRENT              |

|----------|-------------|----------------------|

| 11111111 | (FF)        | Full Outward Current |

| 10000000 | (80)        | Zero Current (Coast) |

| 00000000 | (00)        | Full Inward Current  |

A digital-to-analog converter (DAC) transforms the eight digital lines to a current that an op amp converts to voltage (TP 7). The voltage goes into a lead-lag compensator to stabilize the loop. Finally, the compensator output passes through voltage to current amplifiers that send current to the actuator.

FIGURE 1-18

Actuator Drive Block Diagram

#### Actuator Current

The actuator microprocessor U7 sends an 8-bit word to the actuator DAC U8 to select the actuator current as one of 256 values. The range of values is 128 steps of positive current for outward movement of the actuator (towards Track 0), and 128 steps of negative current for inward movement of the actuator (towards Track 511).

The actuator microprocessor controls the actuator current in two modes: seeking and servoing. The first mode in which the actuator microprocessor controls the actuator current is the seeking mode. Seeking can be further divided into two modes: slew mode and ramped mode. During slew mode, the current to the actuator is one of three values depending on the direction and acceleration/deceleration of the actuator. See Table 1-4.

During ramped mode seeking, the actuator current is incremented or decremented in eight DAC step increments to control velocity.

FIGURE 1-19 Actuator Drive Circuit

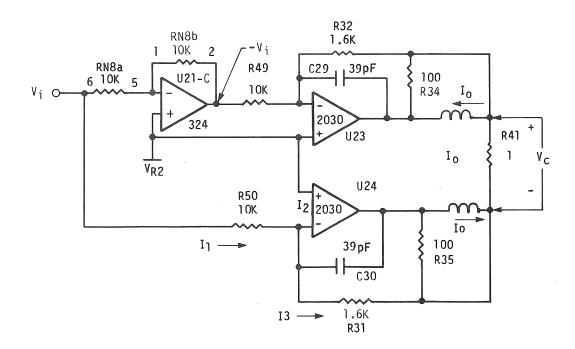

#### Actuator Drivers

Figure 1-20 illustrates the actuator driver circuits. The actuator drivers receive input  $V_i$  from the previous compensation stage (U21-B). The voltage converts to current  $I_0$  according to  $I_0 = .32 \ V_i$ . VR2 = +6.2V which goes to the + input of the TDA 2030 power op amps.

FIGURE 1-20 Actuator Driver Stage

The following summarizes the voltage and current relationships in this circuit:

$$I_2 = 0$$

, therefore  $I_1 = I_3$

$$I_1 = \frac{V_i - 6.2V}{R50} = I_3 = \frac{6.2V - V_0}{R31}$$

Since R50

$$\approx$$

6(R31), then  $V_0 = .16(1V - V_i) + 6.2V \approx 6.4 - .16V_i$

A similar analysis shows that the voltage at the other side of R41 is  $V_0 = 6.4V + .16V_i$ .

Therefore,

$$I_0 = \frac{(6.4 - 16V_i) - (6.4V + .16V_i)}{RFI} = \frac{-.32V_i}{1\Omega} = -.32V_iA$$

In summary, for any voltage  $V_i$ , a current of  $.32V_i$  A runs through the actuator coils to generate a torque. For example,

$$V_i = 1V$$

$I_0 = .32$  amp (produces an outward torque)

In summary,  $V_i > VR2 = 6.2~V$  produces an outward motion (toward Track 0) and  $V_i < VR2 = 6.2~V$  produces an inward motion (toward TK511).

Resistors R34 and R35 swamp out the effects of the inductance of the rotor coils. Capacitors C29 and C30 suppress high frequency oscillations.

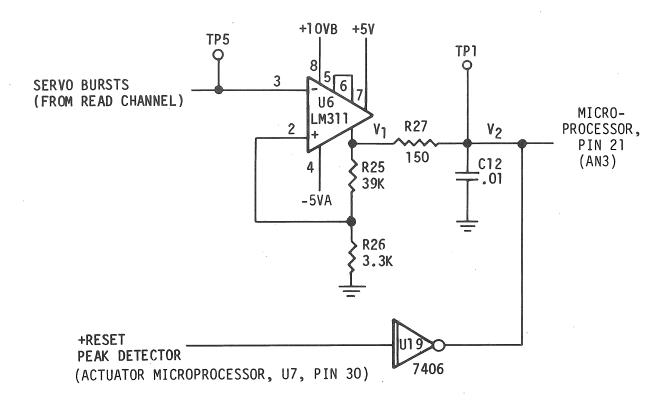

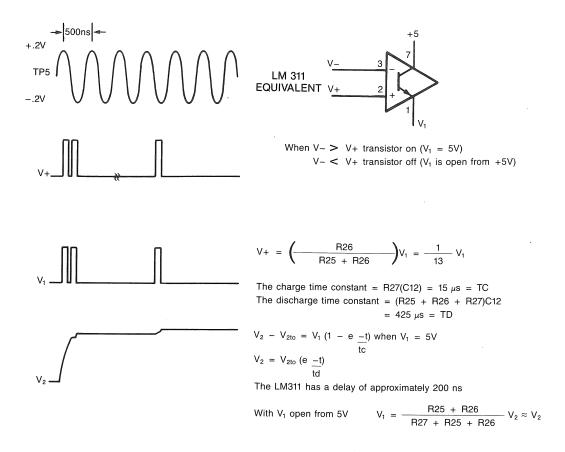

#### Servo Read and Conversion Circuits

Figure 1-21 illustrates the servo peak detector circuit. The servo peak detector takes a 2.17 MHz sine wave input and finds the greatest positive voltage. The peak voltage is amplified and held in capacitor C12. The peak detector is reset by U19 (7406) which receives its input from the actuator microprocessor and discharges C12.

FIGURE 1-21 Servo Peak Detector

Figure 1-22 illustrates the servo peak detector waveforms.

FIGURE 1-22 Servo Peak Detector Signals

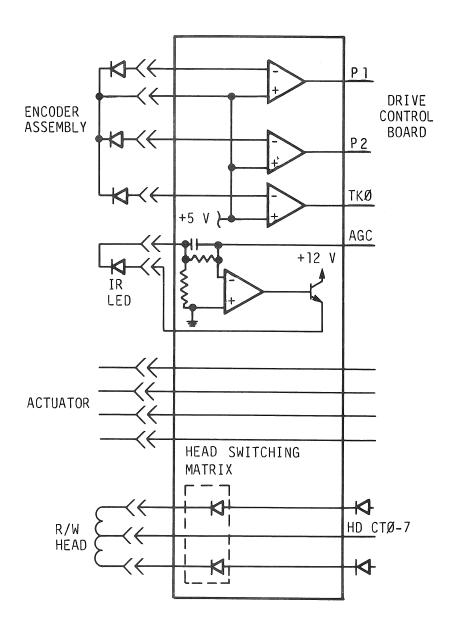

#### 1.3.12 HEAD SWITCHING MATRIX

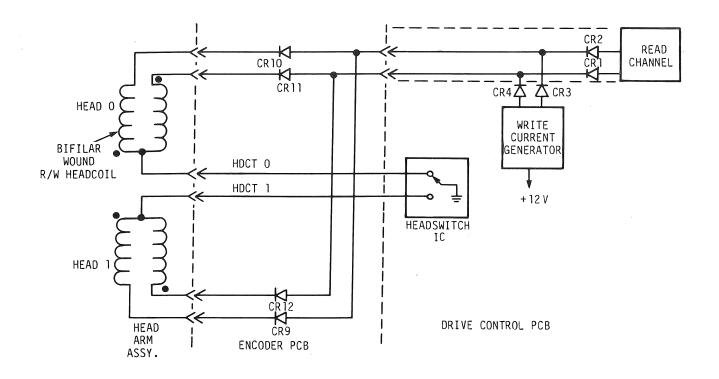

Figure 1-23 is a simplified schematic of the head switching diode matrix for two heads.

Diodes CR9-CR12 are part of the head switching matrix. When the head switch IC grounds the head center tap (HDCT 0-7), the selected head is connected to the Read/Write circuits via one of the diode pairs. None of the other diode pairs is forward biased — this isolates the other heads from the selected head. Diodes CR1-CR4 are part of the Read/Write circuits and are used to isolate the Read and Write circuits from each other.

FIGURE 1-23 Head Switching Matrix

# 1.3.13 WRITE DATA CIRCUITS

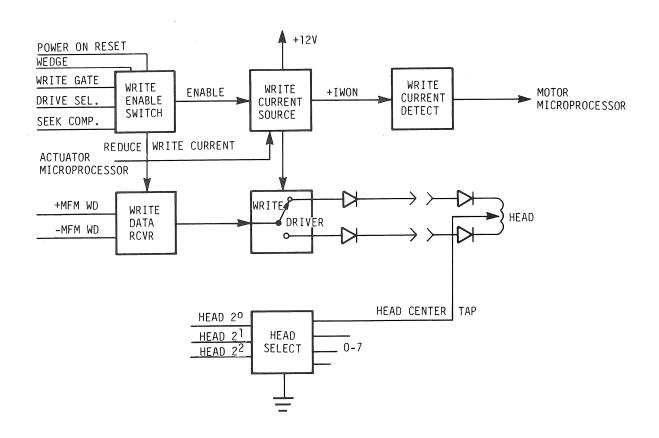

Figure 1-24 is a functional block diagram of the write circuits found in the Q500. The write enable circuit ensures that:

- 1. The 5V logic voltage is present.

- 2. The drive is selected, SEEK COMPLETE is true, and it is not wedge time (to prevent writing in the servo area). See Figure 1-28 for the wedge timing diagram.

- 3. The WRITE GATE is active.

When these conditions are met, the write enable switch turns on the write current source.

FIGURE 1-24 Write Circuit Block Diagram

When enabled, the write current source provides the write driver with 18 mA of write current. The circuit also provides a current-on signal that is used by the motor microprocessor to determine Write Fault. The write driver receives its switching input from the write data receiver. The write driver switches the write current into either end of the head coil whose center tap has been grounded by the head select switch. Refer to Figure 1-25 for a schematic illustration of the write data circuit.

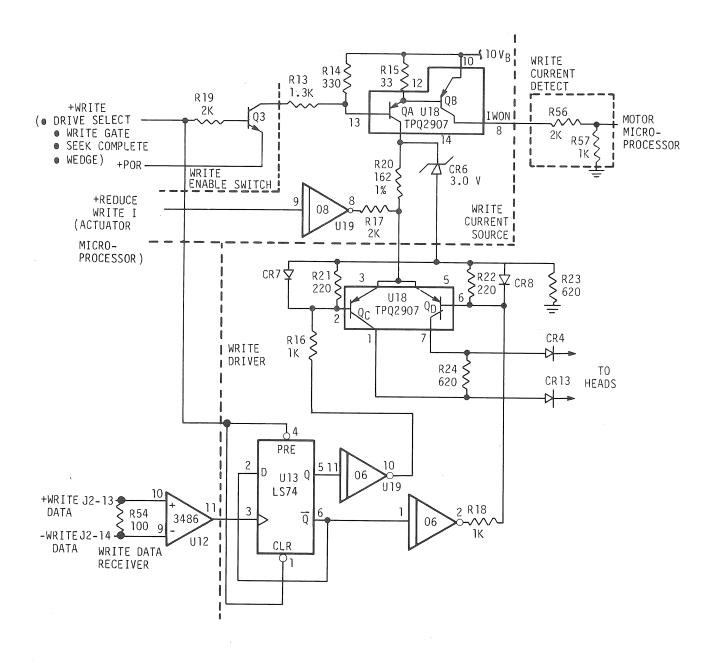

FIGURE 1-25 Write Data Circuit

Assuming that +POR is inactive and +WRITE = (DRIVE SELECT) (WRITE GATE) (SEEK COMPLETE) = HI, then  $Q_3$  (in Figure 1-25) is turned on, providing base current to  $Q_A$ , which supplies the write current.

$Q_{\rm B}$  is turned on when  $Q_{\rm A}$  is on, so current flows through the voltage divider R56/R57, creating a voltage which is detected by the motor microprocessor indicating active write current.

Write current is set by Zener diode CR6 and resistor R20 and is given by the equation:

Iwrite =

$$\frac{V_{C} (Q_{A}) - V_{E} (Q_{C,D})}{R20}$$

$$= V_{E} (Q_{C,D}) - V_{BE} (Q_{C,D}) + V_{CR8} + V_{CR6} - V_{E} (Q_{C,D})$$

$$R20$$

$$= V_{CR6} \text{ (since } V_{BE} (Q_{C,D}) = V_{CR8})$$

$$= 3 V \text{ 18 mA}$$

Current direction in the head is switched by  $Q_C$  and  $Q_D$ . Write data enters a line receiver at the data interface whose output toggels an LS74 flip-flop, U13. The Q and  $\overline{Q}$  outputs of the flip-flop are buffered and turned on either  $Q_C$  or  $Q_D$ . A write data pulse causes a switch in current direction through the head whose center tap has been grounded.

Write current is reduced automatically. At Cylinder 256, the actuator microprocessor sets the REDUCE WRITE I signal high; this grounds one end of R17 through inverting buffer U19. The other end of R17 is attached to the emitters of  $Q_C$  and  $Q_D$ . The Current sunk through  $R_{17}$  reduces the write current to the heads by approximately 20%.

#### 1.3.14 READ DATA CIRCUITS

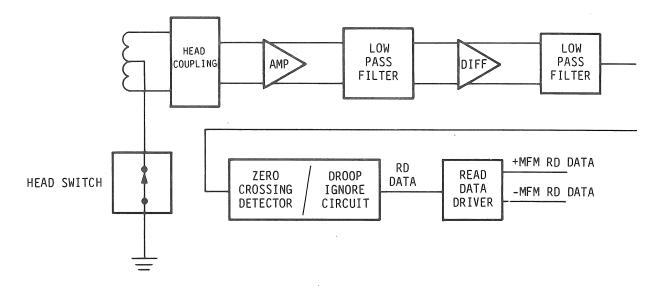

The block diagram in Figure 1-26 illustrates the functional elements of the Q500 read channel. When the head select switch connects the center tap of the selected head to ground, the diodes in the head coupling network become forward biased. Magnetic flux changes passing by the head induce current into the coil. This current is coupled through the head coupling diodes and appears as small differential voltage changes at the input of the amplifier. The amplifier boosts these changes that then travel through a low pass filter to eliminate unwanted high frequency noise. The signal is input to the differentiator, which converts the voltage peaks of the signal to zero voltage crossings. These zero voltage crossings represent the flux changes read from the disk. The differentiated signal passes through further low-pass filtering before being input to the zero crossing detector, where READ DATA pulses are created from the zero crossings. These READ DATA pulses are input to a line driver with differential output. The output of the line driver is the  $\pm$  MFM READ DATA sent to the controller via the 20-conductor data cable.

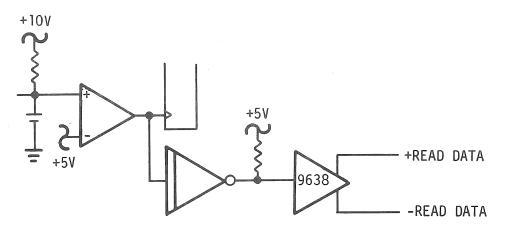

FIGURE 1-26 Read Channel Block Diagram

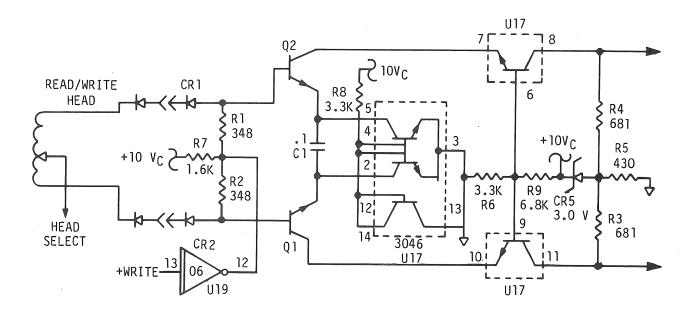

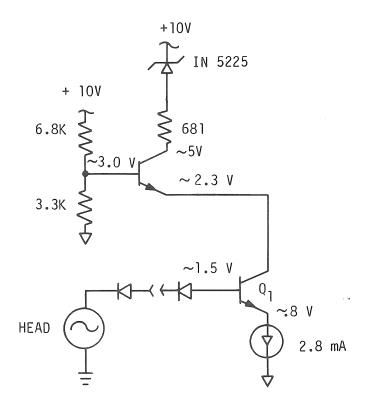

Figure 1-27 shows the front end of the read channel.

FIGURE 1-27

Read Channel Front End

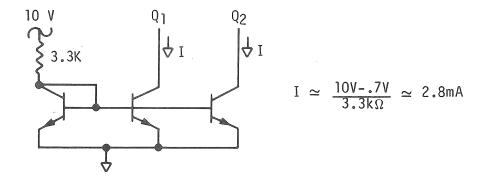

When +WRITE goes HI, CR1 and CR2 become reversed bias, as U19 Pin 12 goes LO, thus preventing the write signal from entering the read channel. When +WRITE is LO, the READ signal flows differentially to  $Q_1$  and  $Q_2$ . The three transistors of U17 provide current sources which bias  $Q_1$  and  $Q_2$  on. Refer to Figure 1-28.

FIGURE 1-28 U17 Current Source

The remaining two transistors of U17 each couple with  $Q_1$  or  $Q_2$  to constitute a cascode amplifier, shown in a simplified version in Figure 1-29.

FIGURE 1-29 Cascode Amplifier

The cascode amplifier provides small-signal current gain =  $h_{fe}(Q_1)$ , or approximately 100.

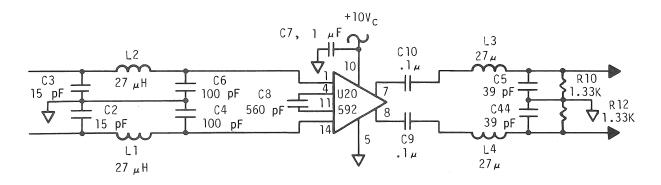

#### Low Pass Filter/Differentiator

After being amplified, the READ signal is passed through low pass filtering before entering a differential amplifier where peaks (from flux transitions inducing head current) are converted to zero-crossings.

A 592 Differential Amplifier is used to perform the differentiation and provide voltage gain of 400. The output of the differentiator passes through two capacitors (C9 and C10) which remove the dc component from the signal. After further low pass filtering, the signal proceeds to the zero-crossing detector circuit. Figure 1-30 shows the low pass/differentiator circuitry.

FIGURE 1-30 Low Pass Filter/Differentiator

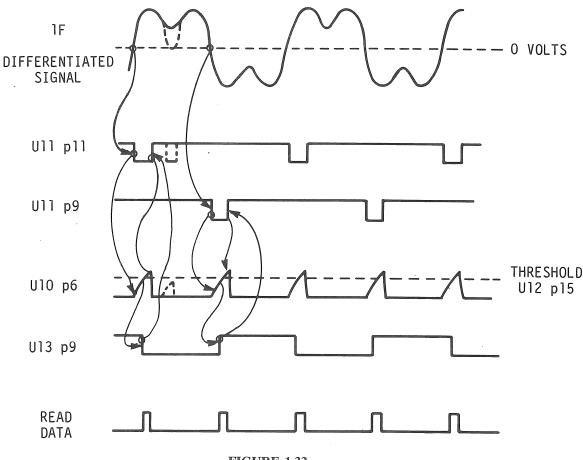

#### Zero-Crossing Detector/Droop Ignore Circuit

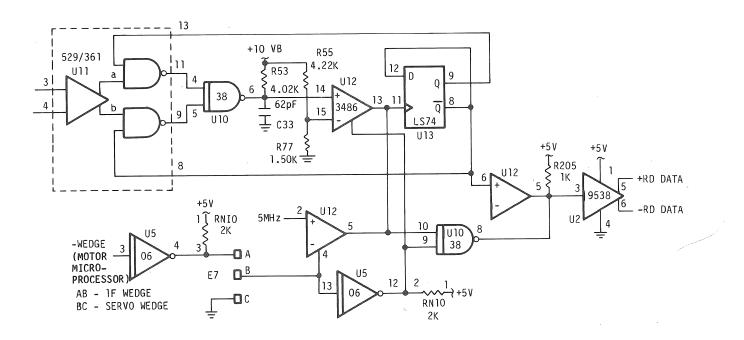

Up to this point, the read channel has detected, amplified, and filtered the flux changes recorded on the disk and transformed the resultant voltage peaks through differentiation to zero-crossings for easy detection. The signal is now input to an 529/361 comparator which detects the zero-crossings and creates READ DATA pulses. Figure 1-31 shows the comparator and its simplified internal circuit.

FIGURE 1-31 Comparator and Equivalent Internal Circuit

The end of the READ channel is shown in Figure 1-34, using the representation of the 529 comparator shown in Figure 1-31.

Placing the E7 jumper across BC, or at AB when point A is a logic zero, results in a simplified circuit output shown in Figure 1-32.

FIGURE 1-32 Simplified Circuit Output

#### **Data Pulse Generation**

For differentiated IF signal input, consider the droop ignore circuit waveforms found in the circuit illustrated in Figure 1-33. Figure 1-34 shows the droop ignore circuit. As the outputs of the 529 (Pin 9 or 11) zero-crossing detector go LO, the output of the open-collector NAND gate (U10) is allowed to go HI at a rate set by the RC time constant of R53 and C33. As the rising edge heads towards +10V, it breaks the threshold set for comparator 3486 (U12), which toggles the flip-flop (U13). When this threshold is broken, the strobe inputs (Pins 8 and 13) of the 529 change, and the output returns to HI (Pin 9 or 11), thereby forcing the NAND gate output (U10 Pin 6) to ground. The READ DATA pulse width is determined by the length of time that the signal at U10 Pin 6 is greater than the V— threshold of U12 (typically about 50 ns) set at approximately 3.0V by R55 and R77.

FIGURE 1-33

Droop Ignore Circuit Waveforms

#### **Droop Ignore Circuit**

The droop ignore circuit prevents the pulse train from generating false data pulses due to droop. Droop is the tendency of the differentiated signal to droop toward zero volts between flux transitions. Droop may occur while the drive reads low frequency data patterns from the disk and when noise or media imperfections cause the signal to cross zero between legitimate bits.

Figure 1-33 shows the signals generated for a differentiated IF signal. The droop is not crossing zero volts in this figure (which would be indicated by the signals shown inside the dotted lines). When the output of the zero-crossing detector changes to LO due to the droop, it causes the output of the NAND gate (U10) to rise. The RC time constant of R53 and C33 controls the time interval before the NAND gate signal crosses the threshold of U12, causing a READ DATA pulse. In the case of a droop zero-crossing, the output of the NAND gate does not have sufficient time to cross the threshold because the subsequent zero-crossing of the droop causes the output of the 529 to return to HI, forcing U10 Pin 6 back to ground before U12 detects a bit.

FIGURE 1-34

Zero-Crossing Detector/Droop Ignore Circuit

#### **Options**

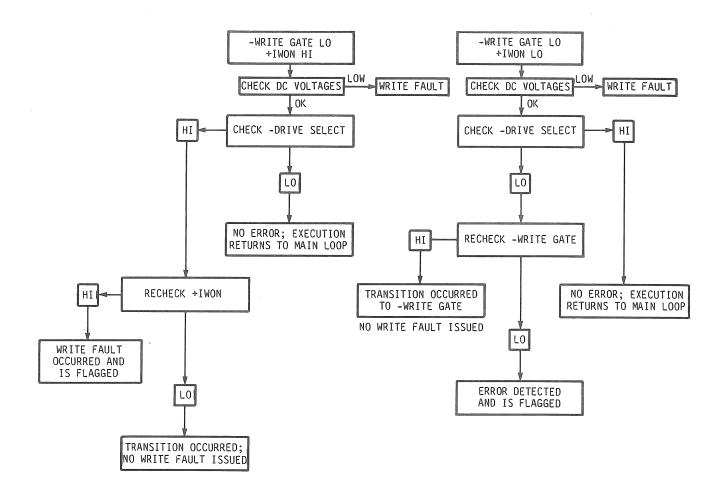

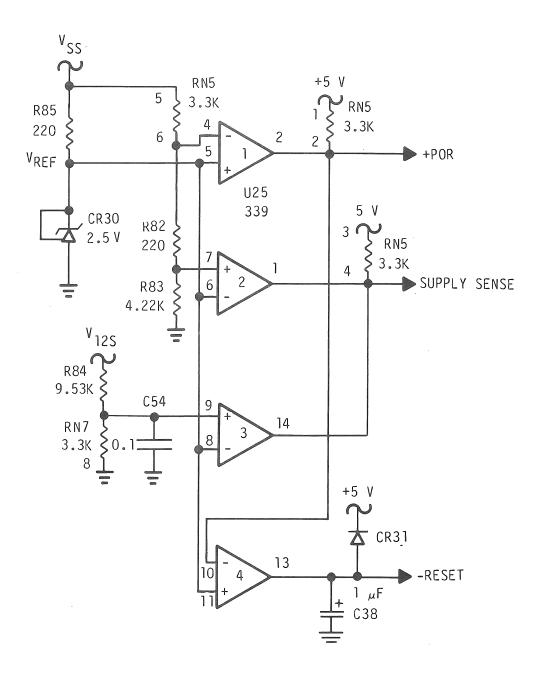

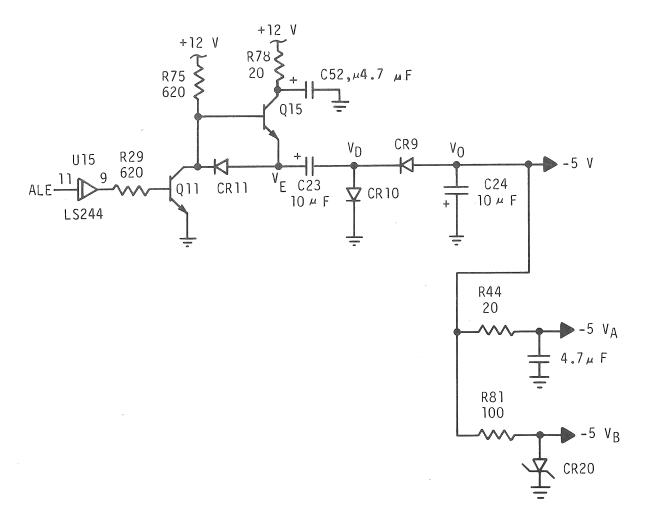

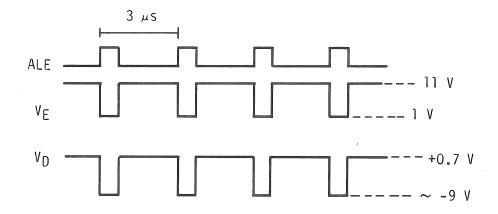

When the user places the E7 jumper in the AB position, the motor microprocessor disables the 3486 comparator which normally clocks the flip-flop with the READ DATA pulses when wedge timing occurs. During wedge timing, two other 3486 comparators are enabled which apply a 5 MHz clock to the flip-flop. The Qoutput is sent to the READ DATA interface driver which puts a IF square wave on the READ DATA output lines.