# LOGIC PRODUCTS

**APRIL 1974**

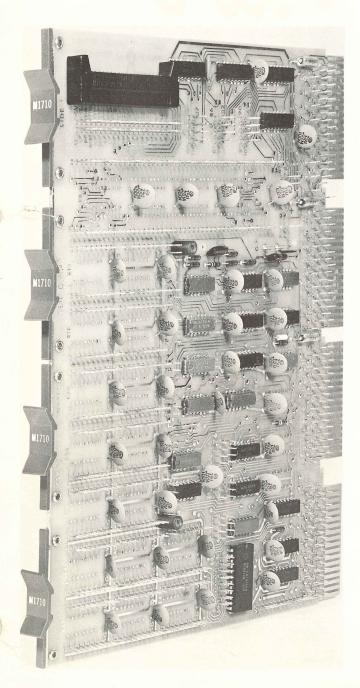

# M1710 UNIBUS Interface Foundation Module

### **DESCRIPTION**

The M1710 UNIBUS® Interface Foundation Module is a general-purpose board that provides for the construction of custom interface designs using integrated circuits (ICs). The M1710 lets users build their own interfaces between a wide variety of peripheral equipment and any PDP-11 processor. All essential UNIBUS logic, such as device address selection, interrupt circuitry, and bus receivers and drivers, is provided. In addition, IC mounting pads with wire-wrappable pins are made available for custom logic designs. These pads accommodate all common types of DIP (dual-in-line-package) integrated circuits with up to 40 pins.

The M1710 is a versatile module, ideal for any type of application. The small end user, such as a university laboratory familiar with ICs, will appreciate both the capabilities and cost-effectiveness of the module; no additional mounting panel or power supply is required. These features, coupled with the fact that the M1710 is capable of automatic wire wrapping, also should prove valuable to the large OEM user who requires many custom interfaces. And, in all cases, the module is easily adaptable to accommodate any changes in interface design.

The M1710 plugs into any Small Peripheral Controller (SPC) slot of a DECkit11-M Instrument Interface or DD11 Peripheral Mounting Panel. Additionally, it may be used in a system unit such as the BB11-A. Connection to user equipment is made via a cable that plugs directly into the M1710 module.

### **FEATURES**

- "Do-it-yourself" interfacing.

- Complete single-card interface.

- Plugs directly into Small Peripheral Controller (SPC) slot.

- Can be used with DECkit11-M Instrument Interface Kit.

- Saves hardware and building costs.

- Preassembled/pretested UNIBUS circuitry eliminates need to build the required bus interfacing functions.

- Wire-wrappable interconnections—compact,

30-gauge wiring used for all IC lead interconnections.

- I/O connection directly to module board—standard 40-conductor cables available.

- All accessories and tools available.

- Accepts all common Dual-In-Line Packages (DIPs); mounts up to 16 of the 14- or 16-pin type plus a multiuse pad set that mounts two 40-pin types, three 24-pin types, four 14- or 16-pin types, or combinations of these.

- Additional bus driver and bus receiver ICs available special high-impedance devices: DEC 8881, DEC 380.

- Includes source of +3 V—convenient for tying unused TTL inputs high, etc.

### **APPLICATIONS**

Since more and more devices are becoming available in DIP form, quite complex systems can be built on the M1710. Some typical applications include:

- Multiword input and/or output.

- Programmable instrument interfaces.

- Interprocessor buffers.

- Custom peripheral controllers.

- Interfacing of:

Microprocessors

A/D converters

Multiplexers

Counters

Shift registers

ROM and RAM memories

Arithmetic logic units

Programmable logic arrays (PLA)

### **FUNCTIONS**

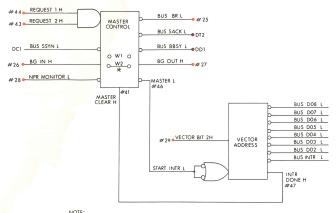

The M1710 can be divided into four functional sections: address selector logic, bus request logic, data bus interface, and miscellaneous logic. These sections are all shown on the accompanying logic diagram. The logic conventions used on the diagram are explained in the INPUT/OUTPUT SYMBOLOGY section at the end of the data sheet. In addition, note that IN and OUT are always used in respect to the master (controlling) device. Thus, when the M1710 is used in a peripheral device, an OUT transfer is a transfer of data out of the master (such as a processor) and into the device. Likewise, an IN transfer is the operation of the peripheral furnishing data to the master. A detailed discussion of UNIBUS interfacing theory is contained in the *PDP-11 Peripherals Handbook* published by Digital Equipment Corporation.

### **Address Selector Logic**

The address selector logic provides gating signals for up to 16 full 16-bit device registers. Addresses which can be chosen by the user range from  $760000_8$  to  $777777_8$ . The basic M1710 address selection logic is similar in function to the M105 Address Selector Module.

The input signals for the address selector logic consist of: 18 address lines BUS A<17:00>; two bus control lines, BUS C<1:0>; and a master synchronization line, BUS MSYN. The address selector decodes the 18-bit address on lines BUS A<17:00> as described in the following steps. This address format, used for selecting a device register is shown in Figure 1.

| 17 | 16 | 15 | 14 | 13 | 12 |                                         | 5 | 4    |            | 1  | 0 |

|----|----|----|----|----|----|-----------------------------------------|---|------|------------|----|---|

| 1  | 1  | 1  | 1  | 1  |    | SELECTED BY WIRE<br>WRAPPED CONNECTIONS |   |      | D FOR 1 OF | 16 |   |

|    |    |    |    |    |    |                                         |   | RYTE | CONTROL —  |    | 4 |

Figure 1. Device Register Select Address Format

- Line BUS A00 is used for byte control.

- Lines BUS A<04:01> are decoded by a 4-to-16-line decoder to select one of the 16 addressable device registers. The outputs from this decoder are listed in Table 1.

- Decoding of lines BUS A<12:05> is determined by wire wrap connections on the M1710 module. Both the inverted and noninverted signals are provided at wire wrap pins for each of these eight address lines. Either the inverted (address bit a binary ONE) or noninverted (address bit a binary ZERO) output of each address line must be wired to one of the eight inputs (wire wrap pins 1 through 8) of the address selector AND gate.

Table 1

Select Line Outputs

|   | Device Register Addre |    |     |    | Select Signal<br>Output | Wire Wrap |  |

|---|-----------------------|----|-----|----|-------------------------|-----------|--|

|   | (m)                   |    |     |    | - 5.1/2 5.1             | Output    |  |

|   | 04                    | 03 | 02  | 01 | (True=0V)               | Pin       |  |

|   | 0                     | 0  | 0   | 0  | SEL 0                   | #76       |  |

|   | 0                     | 0  | 0   | 1  | SEL2                    | #75       |  |

|   | 0                     | 0  | 1   | 0  | SEL4                    | #74       |  |

|   | 0                     | 0  | 1   | 1  | SEL6                    | #73       |  |

|   | 0                     | 1  | 0   | 0  | SEL 10                  | #72       |  |

|   | 0                     | 1  | 0   | 1  | SEL 12                  | #71       |  |

|   | 0                     | 1  | 1   | 0  | SEL14                   | #70       |  |

|   | 0                     | 1  | 1   | 1  | SEL16                   | #69       |  |

|   | 1                     | 0  | 0   | 0  | SEL 20                  | #68       |  |

|   | 1                     | 0  | 0   | 1  | SEL 22                  | #67       |  |

|   | 1                     | 0  | 1   | 0  | SEL 24                  | #66       |  |

|   | 1                     | 0  | 1   | 1  | SEL 26                  | #65       |  |

|   | 1                     | 1  | 0   | 0  | SEL30                   | #64       |  |

|   | 1                     | 1  | 0   | 1  | SEL32                   | #63       |  |

|   | 1                     | 1  | 1   | 0  | SEL 34                  | #62       |  |

| - | 1                     | 1  | 1 . | 1  | SEL36                   | #61       |  |

Lines BUS A< 17:13> must all be binary ONEs. This specifies an address within the top 8K byte address bounds for device registers. Control lines BUS C< 1:0> are decoded and combined with line BUS A00 to generate the signals IN, OUT LOW and OUT HIGH that must be gated with the select signals to control the direction of data transfer operations. The resultant gating signals from this decoding are listed in Table 2.

Table 2

Gating Control Signals

|        |              | 7       |          | ·         | -      |

|--------|--------------|---------|----------|-----------|--------|

| Mode C | Mode Control |         | Gating   | Transfer  |        |

| BUS C< | <1:0>        | Control | Control  | Operation | Output |

| C1     | C0           | BUS A00 | Signal   | Performed | Pin    |

| 0      | 0            | 0       | IN       | DATI      | #39    |

| 0      | 0            | 1       | IN       | DATI      | #39    |

| 0      | 1            | 0       | IN       | DATIP     |        |

| 0      | 1            | 1       | IN       | DATIP     |        |

| 1      | 0            | 0       | OUT LOW, | DATO      |        |

|        |              |         | OUT HIGH |           |        |

| 1      | 0            | 1       | OUT LOW, | DATO      |        |

|        |              |         | OUT HIGH |           |        |

| 1      | 1            | 0       | OUT LOW  | DATOB     | #40    |

| 1      | 1            | 1       | OUT HIGH | DATOB     | #38    |

The handshaking operation between the master and the slave device (M1710) is as follows:

The master sends out the address and gating control code to the M1710. After a 150-ns wait (75 ns to allow for signal skew and 75 ns to allow the M1710 to decode the address), the master device sends BUS MSYN L. The address is decoded as described above and, if it is one of the addresses assigned to the M1710, signal BUS SSYN L is asserted following a 100-ns delay. This delay time may be extended to a maximum of 400 ns by adding an external capacitor between the solder lugs provided on the module. Refer to the SPECIAL WIRING/ADJUSTMENTS section of this data sheet for details. When SSYN INHB is grounded, it inhibits the acknowledgment signal BUS SSYN L normally generated by the M1710. In this case, the BUS SSYN L must be generated by another source.

BUS SSYN L indicates the address was recognized and

the data is stored in the M1710 if it is an OUT operation; for an IN operation, BUS SSYN L indicates the address was recognized and data is present on the D lines for transfer to the master. In either case, when the master receives BUS SSYN L, it clears BUS MSYN L. The M1710 receives cleared BUS MSYN L and clears BUS SSYN L. The master, in turn, receives cleared BUS SSYN L which signifies the end of the current transaction; the bus is now free for other use.

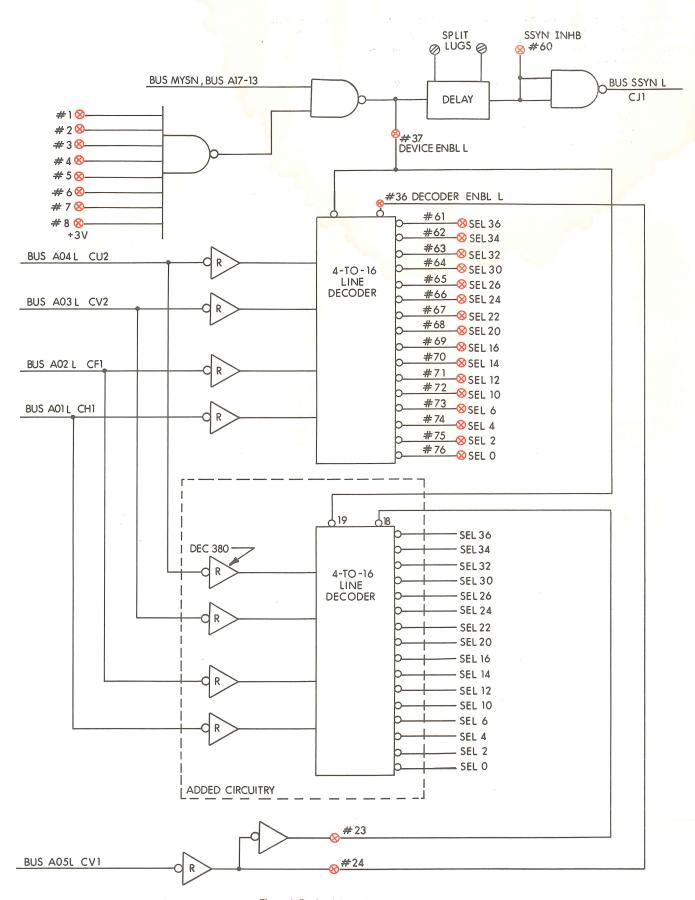

The 4-to-16-line decoder logic is enabled at MSYN time if the signal DECODER ENBL L is grounded. This same logic may be disabled or dynamically enabled to allow for the expansion capability of addressing up to 32 16-bit words. Details for this addressing flexibility are provided in the SPECIAL WIRING/ADJUSTMENTS section of this data sheet.

### **Bus Request Logic**

The M1710 contains the circuitry required to make a bus request and gain control of the bus at either the NPR level or at one of the BR levels. The module also includes circuitry required for transferring a vector address during an interrupt operation. Selection of whether this logic is used for a BR or an NPR level request is explained in the SPECIAL WIRING/ADJUSTMENTS section.

To cause a bus request, whether BR or NPR, both the REQUEST 1 H and REQUEST 2 H inputs must be brought High, causing BR L to be asserted. The particular bus request level is chosen by wire wrapping the BR L output to the proper pin at the bottom of the M1710 that corresponds to one of the BUS BR 4 L through BUS BR 7 L signals. This procedure is described in the SPECIAL WIRING/ADJUSTMENT section.

To acknowledge a bus request, the module must receive the appropriate bus grant signal (BUS BG 4 IN H through BUS BG 7 IN H). The priority level of this grant is the same as the request level and is determined by wire wrapping the BG IN H and BG OUT H signals to the appropriate pins as described in the SPECIAL WIRING/ADJUSTMENTS section.

The BG IN H signal energizes the BUS SACK L output if the particular M1710 is requesting. If the module is not the requesting device, the BG signal will pass through the module and on to the next device via the BG OUT H output.

When the BUS SACK L signal has been sent and the current bus master releases bus control, the M1710 will become the new bus master by asserting BUS BBSY L and MASTER L outputs. Once master, the M1710 can transfer data on the bus. Signal SACK ENABLE L should normally be held High and asserted Low just prior to the last data cycle. BUS SACK L, in turn, will be unasserted as soon as SACK ENABLE L goes Low.

When the M1710 has completed its last data transfer, it can perform either an active or passive bus release if the operation is a BR-type interrupt. A passive bus release is performed by clearing BUS BBSY L and allowing either the processor or another interrupting device to become bus master. If, instead of clearing BUS BBSY L in a passive release, the device asserts BUS INTR L, the processor conducts an interrupt bus transaction called an active bus release.

An active bus release can be performed by tying MASTER L (pin 46) to START INTR L (pin 48). When BUS SACK L is dropped as explained previously, the BUS INTR L output will be activated and the vector address of the interrupt will be placed on the bus data lines, BUS D02L through BUS D08L. This vector address is chosen by wire wrapping logic Highs or Lows on the VECTOR BIT 2 H through VECTOR BIT 8 H inputs. When the processor has accepted the vector address, it returns a BUS SSYN L to the M1710 which now clears BUS INTR L, the vector address, and BUS BBSY L, and releases the bus to the processor, thus completing the interrupt.

When the interrupt is completed, the INTR DONE H can be used to clear the request flip-flop by wiring INTR DONE H to the CLEAR H (pin 41) input. The proper connections necessary for this interrupt circuit are described in the SPECIAL WIRING/ADJUSTMENTS section.

In addition, the single interrupt circuitry on the M1710 can be configured (by adding external gates and flipflops) to handle two or more interrupting devices, each with a separate vector address.

### **Data Bus Interface**

The M1710 contains standard UNIBUS receivers which provide a buffered bus signal output for each of the 16 data lines OUT 00 H through OUT 15 H. Output drive capability of these receivers is seven TTL unit loads.

The module also includes 16 bus drivers which drive data lines IN 00 H through IN 15 H. Input loading to each driver is 1.25 standard TTL loads. All 16 drivers have two common gate line enables (DRIVER ENABLE 1 and DRIVER ENABLE 2) which require a logic Low for assertion. Each enable represents four TTL unit loads.

### Miscellaneous Logic

The following additional circuitry is also provided on the M1710:

- Inverted and noninverted buffered INIT outputs (pins 58 and 59) capable of driving 28 and 30 TTL unit loads respectively.

- A general-purpose flip-flop with all input and output pins available for wire wrap (pins 51 through 57).

- A +3-volt source (pin 50) capable of driving 30 TTL unit loads.

### **SIGNAL SPECIFICATIONS**

For purposes of this data sheet, all signals to and from the M1710 can be categorized into two areas: UNIBUS signals and non-UNIBUS signals.

### **UNIBUS Signals**

All UNIBUS signals described below conform to specifications outlined in the *PDP-11 Peripherals Handbook*. Refer also to the INPUT/OUTPUT SYMBOLOGY section of this data sheet for loading information.

BUS MSYN L—a signal from the master device that initiates the particular M1710 operation and gates in the address and data signals.

BUS SSYN L—a signal to the master device indicating the M1710 has received the address and data, and the bus is now free for other operations.

BUS A00 L through BUS A17 L—18 lines from the master device to all slaves to determine which slave is to be selected.

BUS C00, C01—selects the type of transfer operation. BUS D00 L through BUS D15 L—the 16 bidirectional data lines.

BUS NPG IN (OUT)—(Non-Processor Request Grant) the response by the processor to an NPR.

BUS BG4 IN (OUT) H through BG7 IN (OUT) H—(Bus Grant) the response by the processor to a BR.

BUS NPR L—(Non-Processor Request) a signal from the M1710 to the processor requesting control of the bus for data transfers.

BUS BR4 L through BR7 L—(Bus Request) signals from the M1710 requesting control of the bus.

BUS INTR L—(Interrupt) a signal from the M1710 (master) to processor to initiate program interruption.

BUS SACK L—(Selection Acknowledge) a signal from the M1710 to the processor acknowledging receipt of a BG or NPG.

BUS BBSY L—a signal asserted by the master device to indicate bus is being used.

BUS INIT L—a clear signal asserted by the PDP-11 when the START key on the console is depressed, when a RESET instruction is executed, or when the power fail sequence occurs.

### **Non-UNIBUS Signals**

All inputs from external equipment or user-installed IC logic must be standard TTL-compatible levels. All outputs to user-installed IC logic are standard TTL-compatible levels.

SSYN INHB—When this input is grounded, it inhibits the acknowledgment signal (SSYN) normally generated by the M1710. In this case, the SSYN must be generated by another source.

DECODER ENBL L—When asserted, this signal will permit the 4-to-16-line address decoder to select one of 16 peripheral registers.

DEVICE ENBL L—The AND condition of Bus A<05:17> and Bus MSYN. This signal is asserted when one of 16 device registers has been addressed.

SEL 0 through SEL 36—Sixteen signals utilized to select one of 16 peripheral registers. Outputs of address decoder.

CLEAR H—General reset line used to clear the Bus Request Logic.

REQUEST 1 H, REQUEST 2 H—Two signals that are logically ANDed. When both are asserted, a BR or NPR will result.

TEST POINT 1 L—External signal that may be asserted to initiate a BR or NPR from the Bus Request Logic.

BG IN H—Bus Signal, Processor Arbitration Logic response to a Bus Request.

SACK ENABLE L—A signal that will inhibit the clearing of Bus Sack. Used for block transfer DMA cycles.

MASTER L—Signal asserted by the Bus Request Logic of the M1710 which indicates the M1710 is the Bus Master.

TEST POINT 2 H—This signal is the high-going pulse that is utilized in the M1710's Bus Request Logic to check the Master flip-flop. This signal is for test purposes only.

START INTR L—Signal that when asserted will generate a Vector Address and the Interrupt signal to the PDP-11. The signal that initiates the interrupt processes.

VECTOR BIT 2 H-8 H—Seven lines that are strobed during the interrupt process to point the processor to the new Program Counter.

INTR DONE H—Signal generated by the M1710 when the interrupt process has been completed.

IN 00 H-IN 15 H—Sixteen information bits from an external device. Driven by Bus Drivers to the Bus Data lines.

DRIVER ENABLE 1, 2—Two signals that when asserted permit the sixteen IN lines to be asserted on the Bus Data lines.

OUT 00 H-OUT 15 H—Sixteen information bits that are outputted to an external device. Received by Bus Drivers from the Bus Data lines.

NPR MONITOR L—For BR requests, this signal must be connected to the BUS NPR L line. This configuration, if it detects the assertion of the bus grant line to which the module is wired while BUS NPR L is asserted, will block the grant and return BUS SACK L. When the prior bus master has completed its transaction, signal BUS SACK L will be cleared off the bus. The processor will then be able to service the NPR, thus improving the latency time for NPR devices.

### HARDWARE/ACCESSORIES

The M1710 plugs directly into a Small Peripheral Controller (SPC) slot, a DECkit11-M Instrument Interface, or a DD11 Peripheral Mounting Panel.

### Cables

Two cable types are available from DIGITAL in several standard lengths. These cables have the 40-pin (female) mating connector (H856) installed on one or both ends. The part numbers for these two cables are:

BC07A—20-conductor twisted pair, H856 connector on one end only; other end is left unterminated to allow unique connections by the user.

BC08R—40-conductor flat ribbon, H856 connector on both ends; matches male connector H854 for printed circuit board mounting.

### Wire Wrapping Supplies

Wrapping Tool—H811-A, H810-A, H810-D Unwrapping Tool—H812-A 30-gauge wire—P/N935

Slip-on patchcords may be used in lieu of wire wrapping for temporary connections. The type 915 patchcord accepts 30-gauge wire-wrap pins and comes in various standard lengths from 2 inches to 64 inches.

All cables, hardware, and wire-wrap tools are described in the 1973-74 DIGITAL Logic Handbook.

### **Integrated Circuits**

DIGITAL makes available the following special integrated circuits for bus interfacing purposes:

|          | - · ·                                                              |                           |  |  |  |

|----------|--------------------------------------------------------------------|---------------------------|--|--|--|

| DEC 380  | High input impedance,<br>2-input NOR gate IC for                   | P/N 956                   |  |  |  |

|          | receiving UNIBUS                                                   | \$17.00                   |  |  |  |

|          | signals. Four gates/IC.                                            | Pack of 10 ICs            |  |  |  |

| DEC 8881 | Low output leakage<br>current, 2-input NAND<br>gate IC for driving | P/N 957                   |  |  |  |

|          | UNIBUS lines. Four gates/IC.                                       | \$19.00<br>Pack of 10 ICs |  |  |  |

16-pin IC socket, P/N 954 solder-in type. Pack of 10 sockets \$ 7.00

### SPECIAL WIRING/ADJUSTMENTS

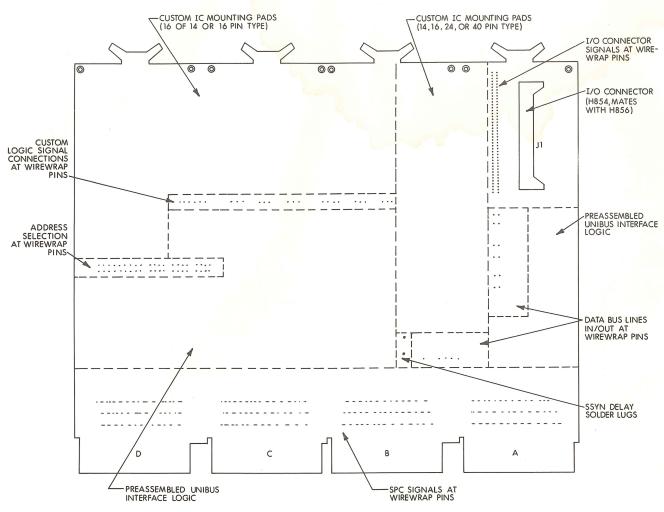

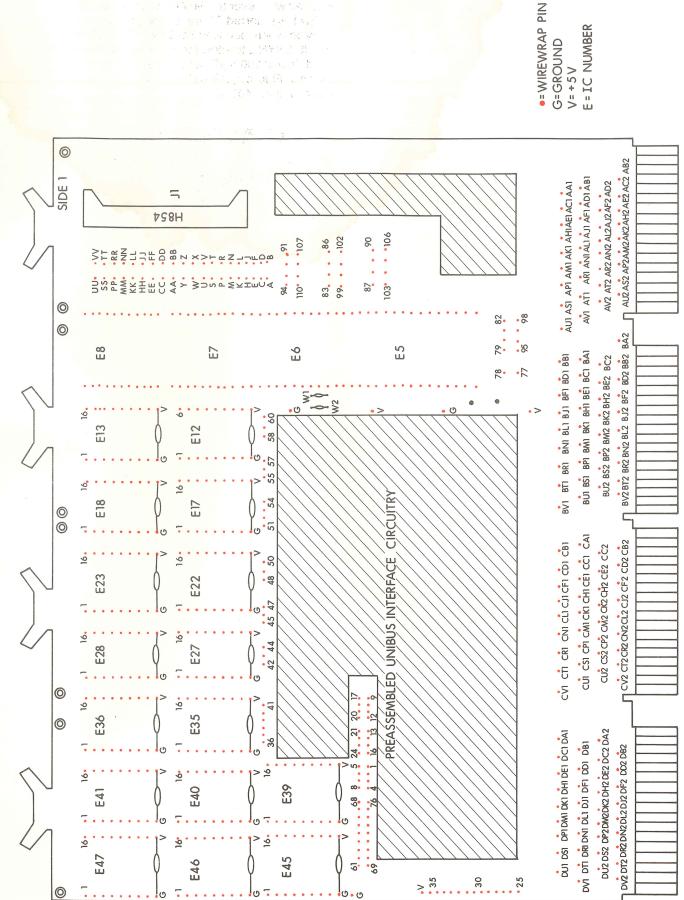

This section describes how to perform the special wiring and adjustments referenced previously in the FUNCTIONS section. All wire wrapping should be performed using 30-gauge solid, insulated wire or, temporarily, with slip-on patchcords. The physical layout of the M1710 is shown in Figure 2 and wire-wrap pin layout is illustrated in Figure 3.

BUS SSYN Delay Adjustment—Signal BUS SSYN L is asserted whenever the M1710 is addressed and BUS MSYN L is asserted. There is an approximate 100 ns delay between receiving BUS MSYN L and the assertion of BUS SSYN L to allow for decoding. By incorporating an additional  $1000\mu\mu$ F capacitor at the solder lugs shown in Figure 2, this delay can be increased to approximately 400 ns.

Figure 2. M1710 Physical Layout (Side 1)

Figure 3. Wirewrap Pin Location Diagram

**⊗** REPRESENTS WIRE WRAP PINS Figure 4. Device Address Expansion Logic

Device Address Expansion—By adding the circuitry shown in Figure 4, additional address flexibility can be provided in the M1710. This circuit expansion allows the user to address 32 16-bit device registers.

NPR or BR Level Request Selection—There are two types of bus requests: NPR and BR.

For NPR requests, the setup is:

- 1. Signal NPR MONITOR L tied to +3 V source.

- Jumper W2 removed (jumper W1 must remain inserted).

- SACK ENBL'L is held High until the beginning of the last bus cycle.

Item 1 disables the BUS NPR monitoring circuitry which is not necessary when using this circuit with an NPR device. Item 2 enables the circuitry required for the nonassertion of BUS SACK. Item 3 allows the user to perform multiple word (DMA) transfers during one interrupt cycle.

For BR requests, the setup is:

- 1. NPR MONITOR L tied to pin DJ1.

- Jumper W1 removed (jumper W2 must remain inserted).

Item 1 enables the BUS NPR monitoring circuitry which is required when performing BR interrupts. Item 2 enables the circuitry necessary to clear the BUS SACK flip-flop during BR interrupts.

Bus Request Level Selection—When generating an interrupt, the appropriate bus request level is chosen by wire wrapping the BR L output to the proper pin at the bottom of the M1710 as follows:

| Level | <u>Pin</u> |

|-------|------------|

| BR4   | BH2        |

| BR5   | BF2        |

| BR6   | BE2        |

| BR7   | BD2        |

| NPR   | DJ1        |

|       |            |

Bus Grant Level Selection—The priority level of the grant signal received must be the same as the request level. To accomplish this, the BG IN H and BG OUT H signals must be wire wrapped to one of the following pins

| Level   | Pin |

|---------|-----|

| BG IN 4 | BS2 |

| BG IN 5 | BP2 |

| BGIN6   | BM2 |

| BG IN 7 | BK2 |

| NPG IN  | AA1 |

Typical Interrupt Circuit—All of the necessary connections required for the typical interrupt circuit as described earlier in the FUNCTIONS section are shown in Figure 5.

\* WHEN USED AS A BR DEVICE W2 INSERTED WI OMITTED

WHEN USED AS A NPR DEVICE W2 OMITTED WI INSERTED

Figure 5. Typical Interrupt Circuit Connection

### **POWER REQUIREMENTS**

All power necessary is provided by the respective PDP-11 processor. The preassembled UNIBUS interface logic uses the following power:

User IC logic also draws its power from the processor supply. Wirewrap pin connections are made available at each IC mounting pad for +5 V and GND. The user should calculate the worst case current drain for his custom logic and assure that the processor's supply can accommodate it prior to plugging in the M1710.

### INPUT/OUTPUT SYMBOLOGY

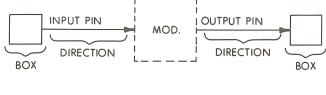

The direction of signal flow on the module diagram is indicated by arrows on the signal lines. Arrows toward the module indicate input signals; arrows away from the module indicate output signals.

Figure 6. Signal Flow Direction

Fan-In and Fan-Out—(in TTL unit loads) is indicated by the number contained in the box associated with each pin. A "B" designation indicates direct connection to the bus.

### Inputs

The loading or designation box always precedes the pin. Symbols with an "R" designation are UNIBUS-compatible receivers.

### **Outputs**

The loading or designation box always follows the pin. Symbols with a "D" designation are UNIBUS-compatible, open-collector drivers.

### MAIN OFFICE AND PLANT

Maynard, Massachusetts, U.S.A. 01754 • Telephone: From Metropoutan Boston: 646-8600 • Elsewhere: (617)-897-5111 TWX: 710-347-0212 Cable: DIGITAL MAYN Telex: 94-8457

### DOMESTIC

### NORTHEAST

| NORTHEAST | REGIONAL OFFICE: 275 Wyman Street, Waltham, Mass. 02154 | Telephone: (617)-890-0320/0330 | Dataphone: 617-890-0065 | CONNECTICUIT | 240 Pomeroy Avenue, Meriden, Conn. 06540 | Telephone: (030)-237-8441/7466 | Dataphone: 203-237-8205 | MASSACHUSETTS | Cambridge/ Boston | 899 Main Street, Cambridge, Mass. 02139 | Telephone: (617)-491-6130 | Dataphone: 617-491-3351 | WALTHAM | WALTHAM | Page 1 | Waltham | Waltham

vvaLIHAM 15 Lunda Street, Waltham, Mass. 02154 Telephone: (617)-891-1030 Dataphone: 617-899-6394 NEW YORK

NEW YORK

Rochester

130 Allens Creek Road, Rochester, New York

Telephone: (716)-461-1700 Dataphone: 716-244-1680

SYRACUSE

5858 East Molloy Road, Rm. 142, Picard Building

Syracuse, New York 13211

Telephone: (315)-455-5987/5988 Dataphone: 315-454-4152

### MID-ATLANTIC

MID-ATLANTIC

REGIONAL OFFICE:

U.S. Route 1, Princeton, New Jersey 08540

Telephone: (603)-452-2940

FLORIDA:

F

2815 Clearview Place, Suite 100

Atlanta, Georgia 03040

Telephone: (404)-451-7411 Dataphone: 305-859-2360

NORTH CAROLINA

NORTH CAROLINA

Durham/Chapel Hill

Executive Park

3700 Chapel Hill Blvd.

Durham, North Carolina 27707

Telephone: (919-489-3347 Dataphone: 919-489-7832

NEW YORK

253 Passaic Ave., Fairfield, New Jersey 07006

Telephone: (201)-227-9280 Dataphone: 201-227-9280

NEW JERSEY

Metuchen Mahaba Nambara 20040

Metuchen 195 Main Street, Metuchen, New Jersey 08840 Telephone: (201)-549-4100/2000 Dataphone: 201-548-0144

TENNESSEE

Kropxville

631 Kingston Pike, Suite 21E

Knoxville, Tennessee 37919

Telephone: (615)-588-6571 Dataphone: 615-584-0571

WASHINGTON D.C.

Executive Building

6811 Kenilworth Ave., Riverdale, Maryland 20840

Telephone: (301)-779-1600, 752-8797

Dataphone: 301-779-1600 Ex. 53

MID-ATLANTIC (cont.)

PRINCETON

MANHATTAN 810 7th Ave. New York, N.Y. 10019 Telephone: (212)-582-1300 PENNSYLVANIA

VENTIAL

REGIONAL OFFICE:

1850 Frontage Road, Northbrook, Illinois 80062

Telephone: (312)-498-2500

Dataphone: 312-498-2500

Ex. 78 INDIANA

PENNSYLVANIA

Philadelphia

Digital Hall

1740 Walton Road, Blue Bell, Pennsylvania 19422

Telephone: (215)-825-4200

TENNESSEE

U.S. Route 1

Princeton, New Jersey 08540

Telephone: (609)-452-2940

Dataphone: 609-452-2940

NEW YORK

Long Island

I Huntington Quadrangle

Suite 1507 Huntington Station, New York 11746

Telephone: (516)-694-4131, (212)-895-8095

Dataphone: 516-293-5693

INDIAWA Indianapolis 21 Beachway Drive, Suite G Indianapolis, Indiana 46224 Telephone: (317)-243-8341 Dataphone: 317-247-1212 ILLINOIS

ILLINUIS

Chicago

1850 Frontage Road

Northbrook, Illinois 60062

LOUIS/ANA

New Orleans

3100 Ridgelake Drive, Suite 108

Metairie, Louisiana 70002

Telephone: (504)-837-0257

Dataphone: 504-833-2800

CENTRAL (cont.)

MICHIGAN MICHIGAN

Ann Arbor

Ann Arbor, Michigan 48103

Telephone: (313)-761-1150

DETROIT

23717 Greenfield Road

Suite 189

Southfield, Michigan 48075

MINNESOTA

MINNESOTA

MINNESOTA

Minneapolis 8030 Cedar Ave. South, Minneapolis, Minnesota 55420 Telephone: (612)-854-6562-3-4-5 Dataphone: 612-854-1410 MISSOURI

MISSOURI Kanasa City 12401 Esst 43rd Street, Independence, Missouri 64055 Telephone: (816)-252-2300 Dataphone: 816-461-3100 ST. LOUIS Suite 110, 115 Progress Parkway Maryland Heights, Missouri 63043 Telephone: (314)-878-4310 Dataphone: 816-461-3100 OHIO

OHIO

Cleveland

250 Euclid Avenue, Euclid, Ohio 44117

Telephone: (216)-946-8484

DAYTON

3101 Kettering Boulevard

Dayton, Ohio 45439

Telephone: (513)-294-3323

Dataphone: 513-298-4724

OKLAPION

Tulsa

3149 S. Winston

Winston Sq. Bldg., Suite 4, Tulsa, Oklahoma 74135

Telephone: (918)-749-4476

Dataphone: 918-749-2714

PENNSYLVANIA

PENNSYLVÀNIÁ

PIRISBURGH

400 Penn. Center Boulevard, Pittsburgh, Pennsylvania 15235

Telephone: (412)-243-9404

TEXAS

Dallas

Plaza North, Suite 513

2880 LBI Freeway, Dallas, Texas 75234

Telephone: (214)-620-2051

HOUSTON

6556 Hornwood Drive

HOUSTON Dataphone: 214-620-2061 6856 Hornwood Drive Monterey Park, Houston, Texas 77036 Telephone: (7/3)-777-9471 WISCONSIN Milwaukee

Milwaukee 8531 West Capitol Drive, Milwaukee, Wisconsin 53222 Telephone: (414)-463-9110 Dataphone: 414-463-9115

WEST

REGIONAL OFFICE:

310 Soquel Way, Sunnyvale, California 94086

Telephone: (408)-735-9200 Dataphone: 408-735-1820 ARIZONA

Phoenix 4358 East Broadway Road, Phoenix, Arizona 85040 Telephone: (602)-268-3488 Dataphone: 602-268-7371 CALIFORNIA

Santa Ana 2110 S. Anne Street, Santa Ana, California 92704 Telephone: (714)-979-2460 Dataphone: 714-979-7850

SAN DIEGO 6154 Mission Gorge Road Suite 110, San Diego, California Telephone: (714)-280-7880/7970 Dataphone: 714-280-7825 SAN FRANCISCO 1400 Terra Bella, Mountain View, California 94040 Telephone: (415)-964-6200 Dataphone: 415-964-1436

OAKLAND

7850 Edgewater Drive, Oakland, California 94621

Telephone: (415)-635-5453/7830 Dataphone: 415-562-2160

WEST LOS ANGELES

1510 Cotner Avenue, Los Angeles, California 90025

Telephone: (213)-479-3791/4318 Dataphone: 213-478-5626

COLORADO 7901 E. Bellevue Avenue Suite 5, Englewood, Colorado 80110 Telephone: (303)-770-6150 Dataphone: 303-770-6628

NEW MEXICO

Albuquerque 10200 Menual N.E., Albuquerque, New Mexico 87112 Telephone: (505)-296-5411/5428 Dataphone: 505-294-2330 OREGON

ORCEON Portland Suite 168 5319 S.W. Westgate Drive, Portland, Oregon 97221 Telephone: (503)-297-3761/3765 UTAH

UTAH

Salt Lake City

431 South 3rd East, Salt Lake City, Utah 84111

Telephone: (801)-328-9839 Dataphone: 801-364-9956 WASHINGTON Bellevue 13401 N.E. Bellevue, Redmond Road, Suite 111

Bellevue, Washington 98005 Telephone: (206)-545-4058/455-5404 Dataphone: 206-747-3754

### **EUROPEAN HEADQUARTERS**

Digital Equipment Corporation International Europe 81 route de l'Aire 1211 Geneva 26, Switzerland Telephone: 42 79 50 Telex: 22 683

Equipment Digital Centre Silic Centre Sillo 94 533 Rungis , Paris, France 74 543 Rungis , Paris, France 74 549 GRENOBLE Equipment Digital Tour Mangin 16 — Rue de' General Mangin, 38, 100 Grenoble, France 74 Telephone: (76) 87-03-21 Telex: 212-32882

### GERMAN FEDERAL REPUBLIC

Digital Equipment GmbH

MUNICH

8 Muenchen 13, Wallensteinplatz 2

Telephone: 0811-35031 Telex: 524-226

COLOGNE

# AUSTRIA

Digital Equipment Corporation Ges.m.b.H. VIENNA Mariahilferstrasse 136, 1150 Vienna 15, Austria Telephone: 85 51 86

### UNITED KINGDOM

Digital Equipment Co., Ltd.

U.K. HEADQUARTERS

Arkwright Road, Reading, Berks

Telephone: 0734-583555 Telex: 84327

READING The Evening Post Building, Tessa Road Reading, Berks. Fountain House Fountain House

Butts Centre

Reading, RGI 7ON

Telephone: Reading 583555

Teles: 84328

BIRMINGHAM

29/31, Birmingham Road, Sutton Coldfield, Warwicks.

Telephone: (004/)21-355-5501

Teles: 337 060

MANCHESTER

Digital Flaujument Co., Ltd. Digital Equipment Co., Ltd. Digital Equipment Co., Ltd.

Arndale House.

Chester Road, Stretford, Manchester M32 9BH

Telephone: (061)-865-7011 Telex: 668666

LONDON

Bilton House, Uxbridge Road, Ealing, London W.5.

Telephone: 01-579-2334 Telex: 22371

EDINBURGH

Shiel House, Craigshill, Livingston,

West Lothian, Scotland

Telephone: 32705 Telex: 727113

### NETHERLANDS

Digital Equipment N.V. THE HAGUE THE HAGUE Sir Winston Churchillian 370 Rijswijk/The Hague, Netherlands Telephone: 94 9220 Telex: 32533

### BELGIUM

Digital Equipment N.V./S.A.

BRUSSELS

108 Rue D'Arlon

1040 Brussels, Belgium

Telephone: 02-139256 Telex: 25297 SWEDEN

Digital Equipment AB STOCKHOLM STOCKHOLM Englundavagen 7, 171 41 Solna, Sweden Telephone: 98 13 90 Telex: 170 50 Cable: Digital Stockholm

### NORWAY

Digital Equipment Corp. A/S OSLO Trondheimsveien 47

### DENMARK

Digital Equipment Aktiebolag COPENHAGEN Hellerupveg 66 2900 Hellerup, Denmark

### FINLAND

Digital Equipment AB HELSINKI Titismaantie 6 SF-00710 Helsinki 71 Telephone: (090) 370133 Cable: Digital Helsinki

### SWITZERLAND

SWITZERLAND

Digital Equipment Corporation S.A.

GENEVA

81 Route de l'Aire

1211 Geneva 26, Switzerland

Telephone: 42 79 50 Telex: 22 683

ZURICH

Scheuchzerstrasse 21

CH-8006 Zurich, Switzerland

Telephone: 01/60 35 66 Telex: 56059

### ITALY

TIALY

Digital Equipment S.p.A.

MILAN

Corso Garibaldi 49, 20121 Milano, Italy

Telephone: 872 748 694 394

Telex: 33615

### SPAIN

Digital Equipment Corporation Ltd.

MADRID

Ataio Ingenieros S.A., Enrique Larreta 12, Madrid 16

Telephone: 215 35 43 Telex: 27249

BARCELONA BARCELONA Ataio Ingenieros S.A., Granduxer 76, Barcelona 6 Telephone: 221 44 66 ISRAEL

DEC Systems Computers Ltd.

TEL AVIV

Suite 103, Southern Habakuk Street

Tel Aviv, Israel

Telephone: (03) 443114/440763

Telex: 922-33-3163

## INTERNATIONAL

CANADA Digital Equipment of Canada, Ltd.

CANADIAN HEADQUARTERS

P.O. Box 11500

Ottawa, Ontario, Canada

K2H 8K8

Telephone: (613)-592-5111 TWX: 610-562-8732

TORONTO

### GENERAL INTERNATIONAL SALES

GENERAL INITIONAL SALES

REGIONAL OFFICE

146 Main Street. Maynach, Massachusetts 01754

Telephone: (617) 897-5111

From Metropolitan Boston, 646-8600

TWX: 710-347-0217/0212

Cable: DIGITAL MAYN

Telex: 94-8457

### AUSTRALIA

AUSTRALIA

Digital Equipment Australia Pty. Ltd. SYDNEY

P.O. Box 491, Crows Nest

N.S.W. Australia 3065

Telephone: 439-2566

Telephone: 439-2566

Telephone: 699-2868

Telex: AA20740

Cable: DIGITAL, SYDNEY

MELBOURNE

80 Park Street, South Melbourne, Victoria, 3205

Telephone: 699-2888

Telex: AA40616

Telephone: 21-4993

Telex: AA492140

ADELAIDE

Wast Perth, Western Australia 6005

Telephone: 21-4993

Telex: AA92140

ADELAIDE

Norwood, South Australia 5067

Telephone: 63-1339

Telex: AA82825

BRISBANN

313 Leichhardt Street

Spring Hill

Brisbane, Queensland, Australia 4000

Telephone: 444047

### NEW ZEALAND

Digital Equipment Corporation Ltd.

AUCKLAND

Hilton House, 430 Queen Street, Box 2471

Auckland, New Zealand

Telephone: 75533

Digital Equipment Corporation International Kowa Building No. 16 — Annex, First Floor 9:20 Akasaka 1-Chome Minato-Ku, Tokyo 107, Japan Telephone: 586-2771 Telex: J-26428

### JAPAN (cont.)

Rikei Trading Co., Ltd. (sales only)

Kozato-Kaikan Bldg.

No. 18-14 Nishishimbashi 1-Chome

Minato-Ku, Tokyo, Japan

Telephone: 5915246 Telex: 781-4208

### PUERTO RICO

Digital Equipment Corporation de Puerto Rico MIRAMAR MIRAMAR American Airlines Bldg. 804 Ponce De Leon, Miramar, Puerto Rico Telephone: 809-723-8068/67 Telex: 385-9056

## ARGENTINA

BUENOS AIRES Coasin S.A. Virrey del Pino, 4071, Buenos Aires Telephone: 52-3185 Telex: 012-2284

### BRAZIL

BHAZIL

RIO DE JANEIRO — GB

Ambriex S.A.

Rua Ceară, 104, 2 e 3 andares ZC - 29

Rio De Janeiro — GB

Telephone: 264-7406/0461/7625

SÃO PAULO

Ambriex S.A. SAO PAOLO

Ambriex S.A.

Rua Tupi, 538

Sao Paulo — SP

Telephone: \$2-7806/1870, 51-0912

PORTO ALEGRE — RS

Rua Coronel Vicente 421/101

Porto Alegre — RS

Telephone: 24-7411

### CHILE

SANTIAGO SANTIAGO

Coasin Chile Ltda. (sales only)

Casilla 14588, Correo 15,

Telephone: 396713 Cable: COACHIL

### INDIA

INDIA

BOMBAY

Hinditron Computers Pvt. Ltd.

69/A, L. Jagmohandas Marg.

Bombay-6 (WB) India

Telephone: 38-1815: 36-5344

Cable: TEKHOS.

# MEXICO

MEXICO CITY Mexitek, S.A. Eugenia 408 Deptos. 1 Apdo. Postal 12-1012 Mexico 12, D.F. Telephone: (905) 536-09-10 PHILIPPINES

MANILA

Stanford Computer Corporation

P.O. Box 1608

416 Dasmarinas St., Manila

Telephone: 49-68-96

Telex: 742-0352

CARACAS CARACAS Coasin, C.A. Apartado 50939 Sabana Grande No. 1, Caracas 105 Telephone: 72-8662; 72-9637 Cable: INSTRUVEN

ZI